该文描述了引起功率MOSFET发生寄生导通的机制,并进一步指出为了避免寄生导通,在选取MOSFET时应遵循什么准则。

功率MOSFET的寄生导通

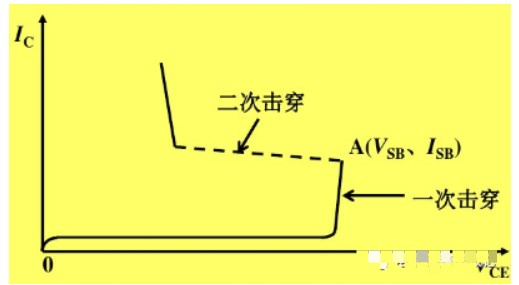

实际上,功率MOSFET发生寄生导通(不希望发生的事件)的机率比我们的预计更高,造成的损失也更大。寄生导通通常会损坏MOSFET,且之后很难查出故障的根源。寄生导通机制取决于漏源和栅源电压间的电容分压比例 。

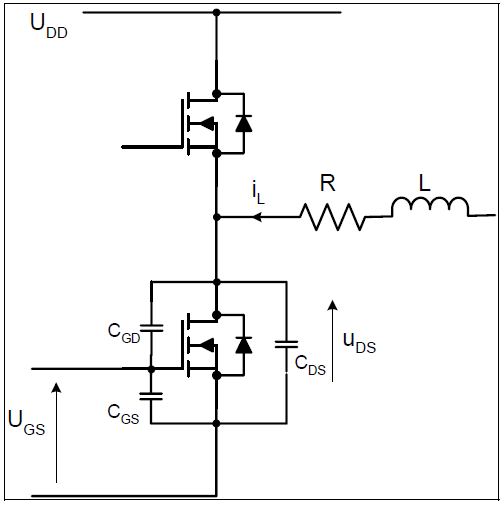

图1是一个基本的半桥配置,该半桥是H桥或三相桥的一部分。如果半桥上管的MOSFET导通了,为了避免直通和因过流而可能出现的MOSFET故障,必须关断半桥下管的一个MOSFET。

图1 MOSFET半桥及其感性负载

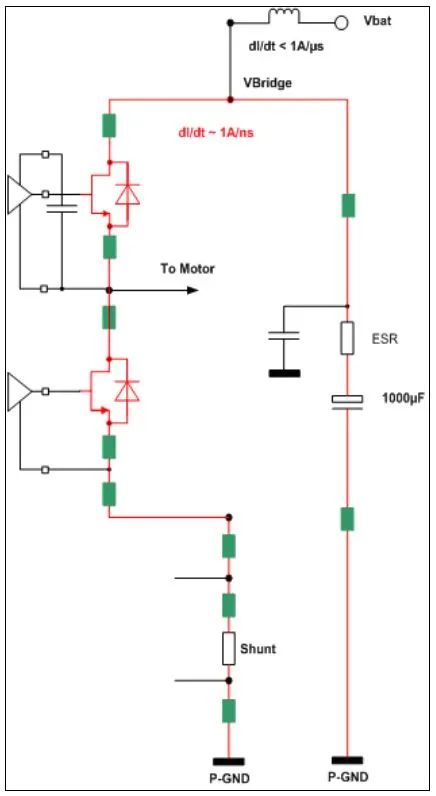

此时,可通过下列公式(1)计算出栅极和源极间的电压:

因此,即便驱动电路试图关断半桥下管的MOSFET,即驱动电路将栅极和源极间的电压置为0(UGS=0V),但由于漏源电压发生变化,且分压线路包含米勒电容(CGD)和栅源电容,所以MOSFET仍然有导通的风险。电容分压器是最快的分压器,对漏源之间出现的所有瞬态电压反应极快,并对其中的高频瞬态电压(即du/dt高的UDS )反应尤其快。在栅极和源极之间安装一个电阻在一定程度上可以防范寄生导通,但作用很小且对高du/dt值无作用。

下面的例子阐述了这些电压到底有多高,多快:

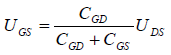

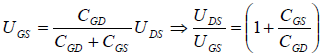

图2是具有寄生元件的逆变器桥臂的半桥配置。电路布局,几何约束或MOSFET连接线所造成的寄生电感,电阻和电容是无法避免的。另一方面,逆变器所在的电路具有最高的di/dt值(典型值约为1A/ns),而电机的相电流和电源线里的电流变化相对平稳。

图2 具有寄生电感(绿色部分)的逆变器半桥基本设计图

MOSFET里的二极管恢复脉冲常常在半桥里产生最高的di/dt。寄生电感和高di/dt感应同时出现或多或少会产生高感应电压尖峰,并在半桥里产生大量地高频噪声。根据寄生电感的尺寸,在12V应用中会出现过压和欠压尖峰,范围是1-2V和几十伏。除了产生高频噪声,这些电压尖峰还会危害MOSFET,桥式驱动器和其它的ECU元件。此外,它们还会使功率MOSFET意外导通。

为避免寄生导通,如何选取MOSFET

再看公式(1):

为了防止寄生导通,UGS/UDS比必须尽量小,UDS/UGS 比必须尽量大,CGS/CGD比也必须尽量大。因此,建议:

为了对寄生导通反应低敏,CGS/CGD 比必须尽量大,大于15(或者最小大于10)。

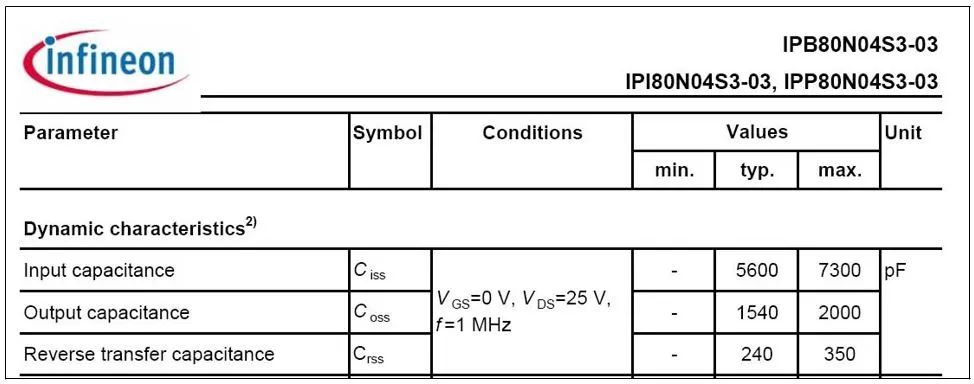

下面的例子说明了如何从数据手册摘录所需的值(本例中的器件为用于电机驱动的 IPB80N04S3-03, OptiMOS-T 40V功率MOSFET):

由于:

可以计算出:CGD_typ=240pF 且CGS_typ=5360pF。CGS/CGD 比是22.3,这个值完全可以防止寄生导通。

图3 数据手册中的电容值

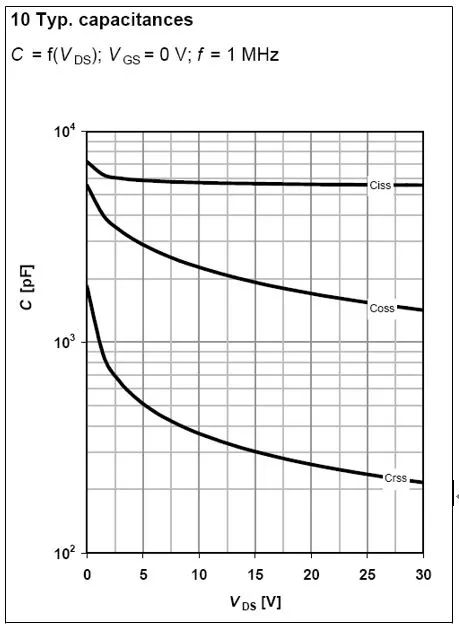

为了获知这些电容值和电源电压大小之间的关系,数据手册还提供了栅漏电容和栅源电容与漏源电压之间的关系,图4是它们之间关系的曲线图。

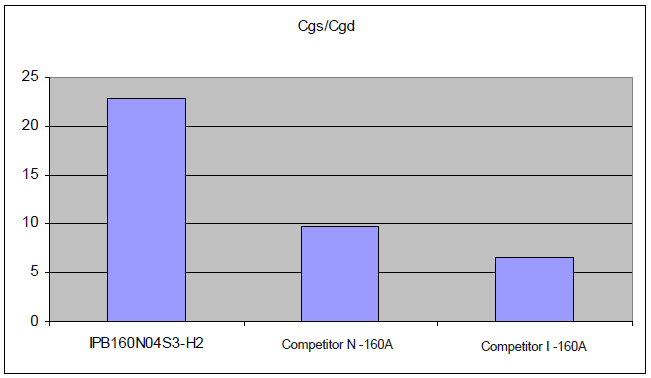

图5比较了MOSFET在不同的大电流应用中(如安全关键电子助力转向,或电子液压助力转向,或发电机)的Cgs/Cgd比。可以看出使用IPB160N04S3-H2后,不会发生寄生导通了,而使用其它两个MOSFET,仍然可能发生寄生导通。

图4 栅漏电容和栅源电容与漏源电压的典型关系

图5 MOSFET在不同的大电流应用中CGS/CGD 的比

审核编辑 黄宇

-

MOSFET

+关注

关注

146文章

7148浏览量

213074 -

导通

+关注

关注

1文章

35浏览量

11334

发布评论请先 登录

相关推荐

安世半导体CCPAK1212封装再次提升Nexperia功率MOSFET的性能表现

AOS MOSFET并联在高功率设计中的应用

功率MOSFET的选型法则

功率MOSFET故障分析

SMT贴片加工中避免导通孔与焊盘的连接不良的有效方法

igbt功率管寄生电容怎么测量大小

MOSFET导通电压的测量方法

功率 MOSFET、其电气特性定义

开关MOSFET为什么会有振铃和电压尖峰

基于NX封装的低杂感SiC MOSFET模块设计

如何避免功率MOSFET发生寄生导通?

如何避免功率MOSFET发生寄生导通?

评论