TWU

table walk unit:包含从内存中读取translation tables的逻辑

一个完整的页表翻译和查找的过程叫作页表查询(Translation Table Walk),页表查询的过程由硬件自动完成,但是页表的维护需要软件来完成。

页表查询是一个相对耗时的过程,理想的状态是TLB里缓存有页表转换的相关信息。当TLB未命中时,才会去查询页表,并且开始读入页表的内容。

page table

page table是每个进程独有的,是软件实现的,是存储在main memory(比如DDR)中的

Address Translation

因为访问内存中的页表相对耗时,尤其是在现在普遍使用多级页表的情况下,需要多次的内存访问,为了加快访问速度,系统设计人员为page table设计了一个硬件缓存 - TLB,CPU会首先在TLB中查找,因为在TLB中找起来很快。TLB之所以快,一是因为它含有的entries的数目较少,二是TLB是集成进CPU的,它几乎可以按照CPU的速度运行。

如果在TLB中找到了含有该虚拟地址的entry(TLB hit),则可从该entry中直接获取对应的物理地址,否则就不幸地TLB miss了,就得去查找当前进程的page table。这个时候,组成MMU的另一个部分table walk unit就被召唤出来了,这里面的table就是page table。

使用table walk unit硬件单元来查找page table的方式被称为hardware TLB miss handling,通常被CISC架构的处理器(比如IA-32)所采用。它要在page table中查找不到,出现page fault的时候才会交由软件(操作系统)处理。

与之相对的通常被RISC架构的处理器(比如Alpha)采用的software TLB miss handling,TLB miss后CPU就不再参与了,由操作系统通过软件的方式来查找page table。使用硬件的方式更快,而使用软件的方式灵活性更强。IA-64提供了一种混合模式,可以兼顾两者的优点。

如果在page table中找到了该虚拟地址对应的entry的p(present)位是1,说明该虚拟地址对应的物理页面当前驻留在内存中,也就是page table hit。找到了还没完,接下来还有两件事要做:

• 既然是因为在TLB里找不到才找到这儿来的,自然要更新TLB。

• 进行权限检测,包括可读/可写/可执行权限,user/supervisor模式权限等。如果没有正确的权限,将触发SIGSEGV(Segmantation Fault)。

如果该虚拟地址对应的entry的p位是0,就会触发page fault,可能有这几种情况:

• 这个虚拟地址被分配后还从来没有被access过(比如malloc之后还没有操作分配到的空间,则不会真正分配物理内存)。触发page fault后分配物理内存,也就是demand paging,有了确定的demand了之后才分,然后将p位置1。

• 对应的这个物理页面的内容被换出到外部的disk/flash了,这个时候page table entry里存的是换出页面在外部swap area里暂存的位置,可以将其换回物理内存,再次建立映射,然后将p位置1。

后面再进一步就是看看这个TLB中具体是怎么找的,在page table中又是怎么“walk”,这部分就是具体的地址是怎么转换的,翻译的。

-

处理器

+关注

关注

68文章

19349浏览量

230311 -

内存

+关注

关注

8文章

3037浏览量

74151 -

操作系统

+关注

关注

37文章

6856浏览量

123450 -

MMU

+关注

关注

0文章

91浏览量

18320

发布评论请先 登录

相关推荐

如何从可编程逻辑访问处理器内存?

CPU怎样通过控制器将待运行的程序从FLASH中读入内存中

CXL内存协议介绍

如何从mifare和/或Felica读取内存内容?

GIC ITS的ITS tables和Command Queue访问简析

ARMv8 MMU translation stages与相关寄存器介绍

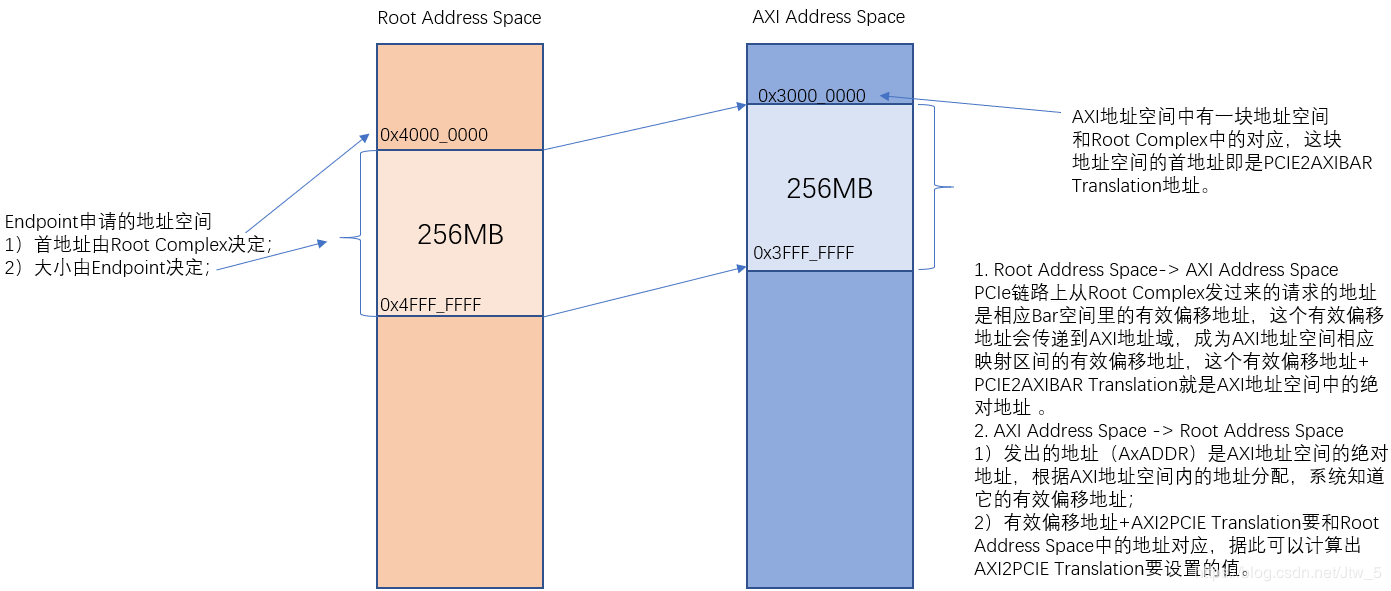

FPGA逻辑中关于地址映射说明

ARM SMMU Data structure之Context Descriptors

从内存中读取translation tables的逻辑介绍

从内存中读取translation tables的逻辑介绍

评论