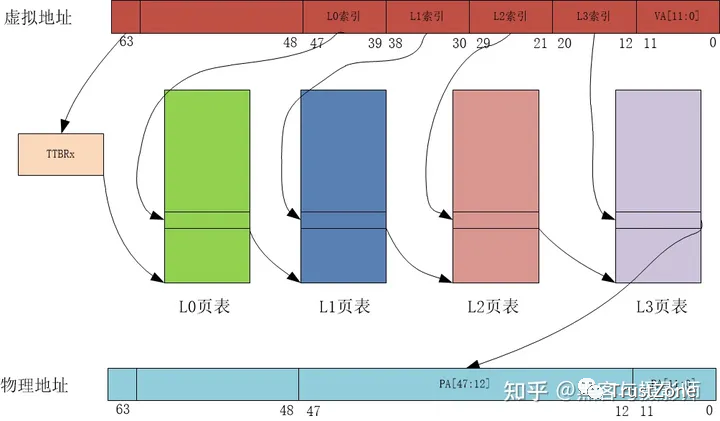

物理页面大小一级地址总线宽度不同,页表的级数也不同。以AArch64运行状态,4KB大小物理页面,48位地址宽度为例,页表映射的查询过程如图:

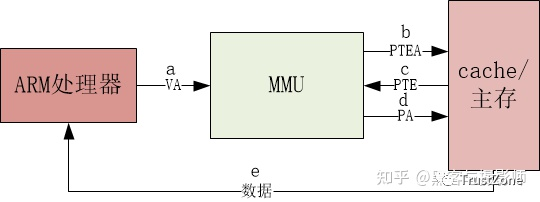

对于多任务操作系统,每个用户进程都拥有独立的进程地址空间,也有相应的页表负责虚拟地址到物理地址之间的转换。MMU查询的过程中,用户进程的一级页表的基址存放在TTBR0。操作系统的内核空间公用一块地址空间,MMU查询的过程中,内核空间的一级页表基址存放在TTBR1。当TLB未命中时,处理器查询页表的过程如下:

• 处理器根据虚拟地址第63位,来选择使用TTBR0或者TTBR1。当VA[63]为0时,选择TTBR0,TTBR中存放着L0页表的基址。

• 处理器以VA[47:39]作为L0的索引,在L0页表中查找页表项,L0页表有512个页表项。

•L0页表的页表项中存放着L1页表的物理基址。处理器以VA[38:30]作为L1索引,在L1页表中找到相应的页表项,L1页表中有512个页表项。

•L1页表的页表项中存放着L2页表的物理基址。处理器以VA[29:21]作为L2索引,在L2页表中找到相应的页表项,L2页表中有512个页表项。

•L2页表的页表项中存放着L3页表的物理基址。处理器以VA[20:12]作为L1索引,在L3页表中找到相应的页表项,L3页表中有512个页表项。

•L3页表的页表项里,存放着4KB页面的物理基址,然后加上VA[11:0],这样就构成了物理地址,至此处理器完成了一次虚拟地址到物理地址的查询与翻译的工作。

-

处理器

+关注

关注

68文章

20343浏览量

255357 -

操作系统

+关注

关注

37文章

7443浏览量

129644 -

MMU

+关注

关注

0文章

92浏览量

19293

发布评论请先 登录

MMU多级页表映射过程

MMU多级页表映射过程

评论