来源:《半导体芯科技》杂志

比利时根特大学的两位教授Roel Baets和Gunther Roelkens,以及imec的两位科学家Joris Van Campenhout和Bernardette Kunert,四人共同撰写的一篇文章“4 Ways to Put Lasers on Silicon”发表在IEEE Spectrum上。文章介绍了关于实现激光器与硅紧密集成的四种方法:倒装芯片集成、微转印、晶圆键合和单片集成,就这些方法的工作原理、可扩展性和成熟度级别等方面进行了比较探讨。以下是我们根据该文章编译整理的部分内容,供读者参考。

引言

光子集成电路(PIC)是在单个芯片上结合了一系列光电功能。PIC在日常生活中正在成为越来越普遍的一部分。它们用于连接数据中心服务器机架的高速光收发器,包括用于提供网站的收发器,用于保持自动驾驶汽车在轨道上的激光雷达,用于发现大气中化学物质的光谱仪,以及许多其他应用。所有这些系统都已经变得比较便宜,并且在某些情况下,通过使用硅制造技术制造了大部分IC,在经济上变得可行。

工程师们已经能够在硅光子芯片上集成几乎所有重要的光学功能,包括调制和检测的基本功能,但是还不能将光发射功能集成到硅光子芯片上。因为硅本身并不能有效地做到这一点,因此通常采用由III-V族材料组成的半导体来制造单独的组件以产生光。

如果您可以在设计中使用外部激光二极管,那就没有问题了。但最近有几个因素促使工程师将激光器与硅光子产品集成在一起。比如,可能没有空间放置单独的光源。例如旨在植入体内以监测血糖水平的微型设备可能会面临这个问题。或者,出于对应用成本的考虑,可能需要更紧密的集成:当您可以在单个硅晶圆上装进数百或数千个激光器时,与需要连接这些单独的芯片相比,将激光器与硅晶圆集成会使您最终获得更低的成本和更高的可靠性。有很多方法可以实现激光器与硅的更紧密集成。比利时纳米电子研发中心imec开展了相关的研究工作,他们目前正在采用四种基本策略:倒装芯片集成、微转印、晶圆键合和单片集成。下面就这些方法的工作原理、它们的可扩展性和成熟度级别,以及它们的优缺点等方面进行讨论。

倒装芯片集成

在硅晶圆上直接集成激光器,这种直接方法是一种芯片封装技术,被称为倒装芯片工艺。

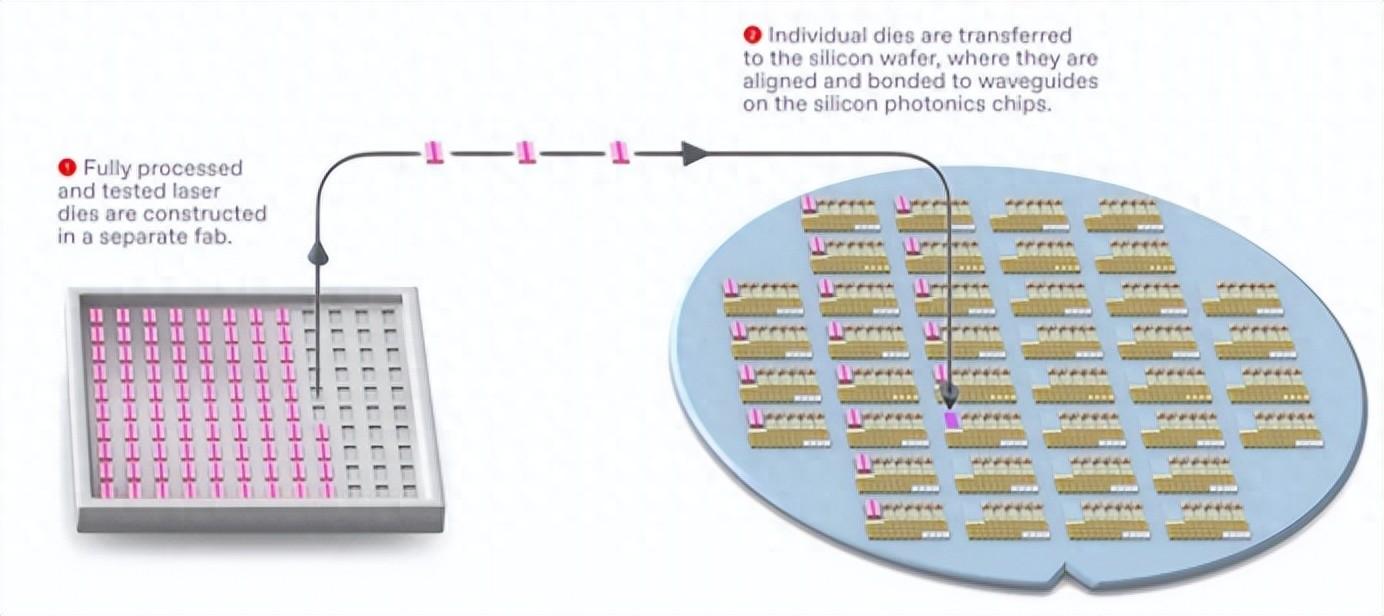

△图1:在倒装芯片键合中,激光芯片(左)被一个一个地转移并键合到硅光子晶圆上。(By Emily Cooper)

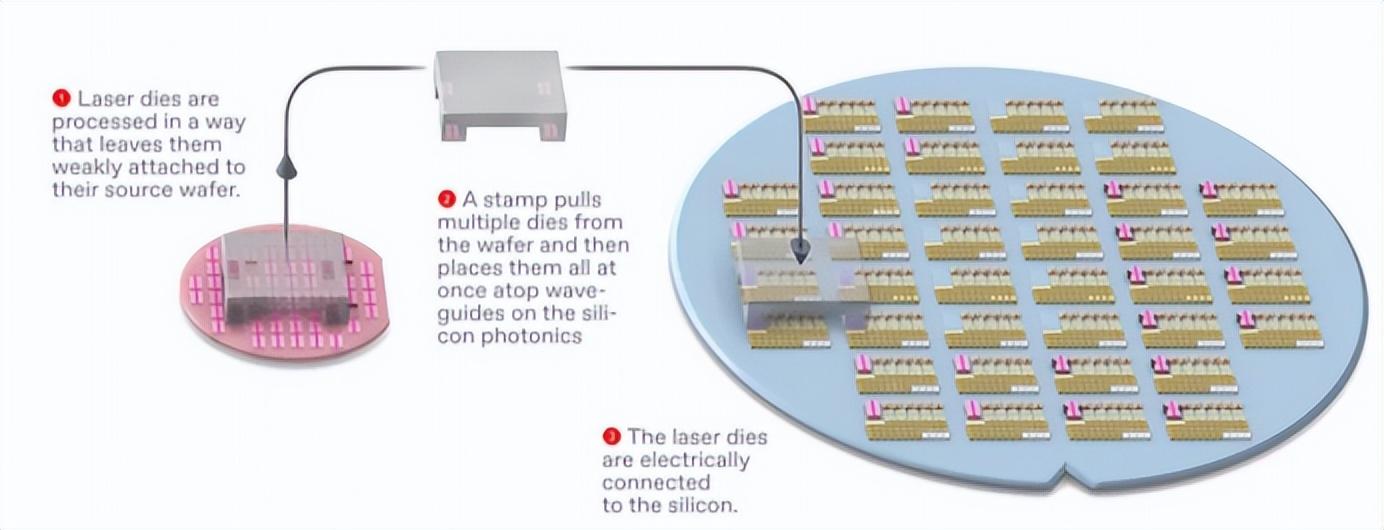

△图2:在微转印印刷中,激光芯片(红色矩形,左)被很弱地固定在自己的晶圆上。印章(浅灰色)一次拾取多个激光器,然后将它们放置在硅光子晶圆上。(By Emily Cooper)

芯片的电气连接在顶部,互连的最上层终止在金属衬垫(焊盘)上。倒装芯片技术依靠焊球附着在这些焊盘上。将芯片翻转过来,使焊料与芯片封装上(或者在我们的情况下在另一个芯片上)的相应焊盘对齐。然后将焊料熔化,将芯片键合到封装上。

当试图将激光芯片键合到硅光子芯片时,这个概念与倒装芯片技术是相似的,但更加严格。边缘发射激光器在晶圆上已经加工完成,被切割成单独的芯片,并由供应商进行测试。然后,使用高精度的倒装工艺,将单个激光芯片与目标硅光子晶圆键合,一次键合一个激光芯片。困难的部分是确保从边缘发射的激光输出与硅光子芯片的输入对齐。我们使用一种称为对接耦合(butt-coupling)的工艺,将激光芯片放置在硅的凹槽处,以使它横向靠近硅光子波导的蚀刻面。

为此,倒装芯片工艺要求在空间三个维度上全部实现亚微米级对准精度。在过去的几年里,imec已经开发了专门的倒装芯片键合工具来完成这项工作,他们与合作者,以及开发合作伙伴已经使用它们来优化组装流程。利用先进的拾取和放置工具,使用机器视觉来保持精确对准,可以在短短几十秒内放置和键合激光器,精度优于500纳米。

2021年,imec还建立了晶圆级硅光子工艺,以改善这一性能。它为硅芯片增加了机械对准基座和更精确的蚀刻对接耦合接口,以实现优于几百纳米的垂直对准。使用这些技术,他们在300毫米硅光子晶圆上组装了一些激光器件。并且很高兴地看到,来自每个激光器的50毫瓦激光有多达80%耦合到它所连接的硅光子芯片中。最坏的情况下整个晶圆的耦合率仍在60%左右。这样的结果可以与主动对准实现的耦合效率相媲美,而主动对准是一种更耗时的过程,其中来自激光器本身的光用于引导对准过程。

倒装芯片方法的一个显著优势是配接芯片类型的简单性和灵活性。因为芯片可以在现有的制造生产线中生产,额外增加的工程有限,所以它们都可以从多个制造商处采购。而且,随着市场需求的增加,越来越多的供应商正在提供倒装芯片组装服务。另一方面,这个工艺的顺序性(每个激光芯片都需要单独拾取和放置)是一个明显的缺点。从长远来看,它限制了制造吞吐量和大幅降低成本的潜力。这对于成本敏感型应用尤其重要,比如消费类产品,以及

每个芯片需要多个激光装置的系统。

微转印

微转印(microtransfer printing)消除了对接耦合的一些对准困难,同时也使组装过程更快。就像在倒装芯片集成中一样,发光器件先在III-V族半导体衬底上生长。但有一个很大的区别:III-V族晶圆没有被切成单独的芯片。而是将晶圆上的激光器底切,因此它们仅通过很小的束缚弱连接固定在源晶圆上。然后用一种类似墨水印章的工具把这些激光器一起拾取起来,打破它们与源晶圆的小束缚。然后,印章再将这些激光器与硅光子晶圆上的波导结构对准,并在那里键合它们。

倒装芯片技术使用的是金属焊料凸点,而微转印使用粘合剂,甚至可以仅使用分子键合,依靠两个平面之间的范德华力来将激光器固定。此外,在硅光子芯片中,光源和波导之间的光耦合也是通过不同的过程发生的。该过程称为倏逝波耦合,它是将激光器放置在硅波导结构的顶部,让光线“流入”其中。虽然以这种方式传输的功率较少,但与对接耦合相比,倏逝波耦合对于对准精度的要求较低。

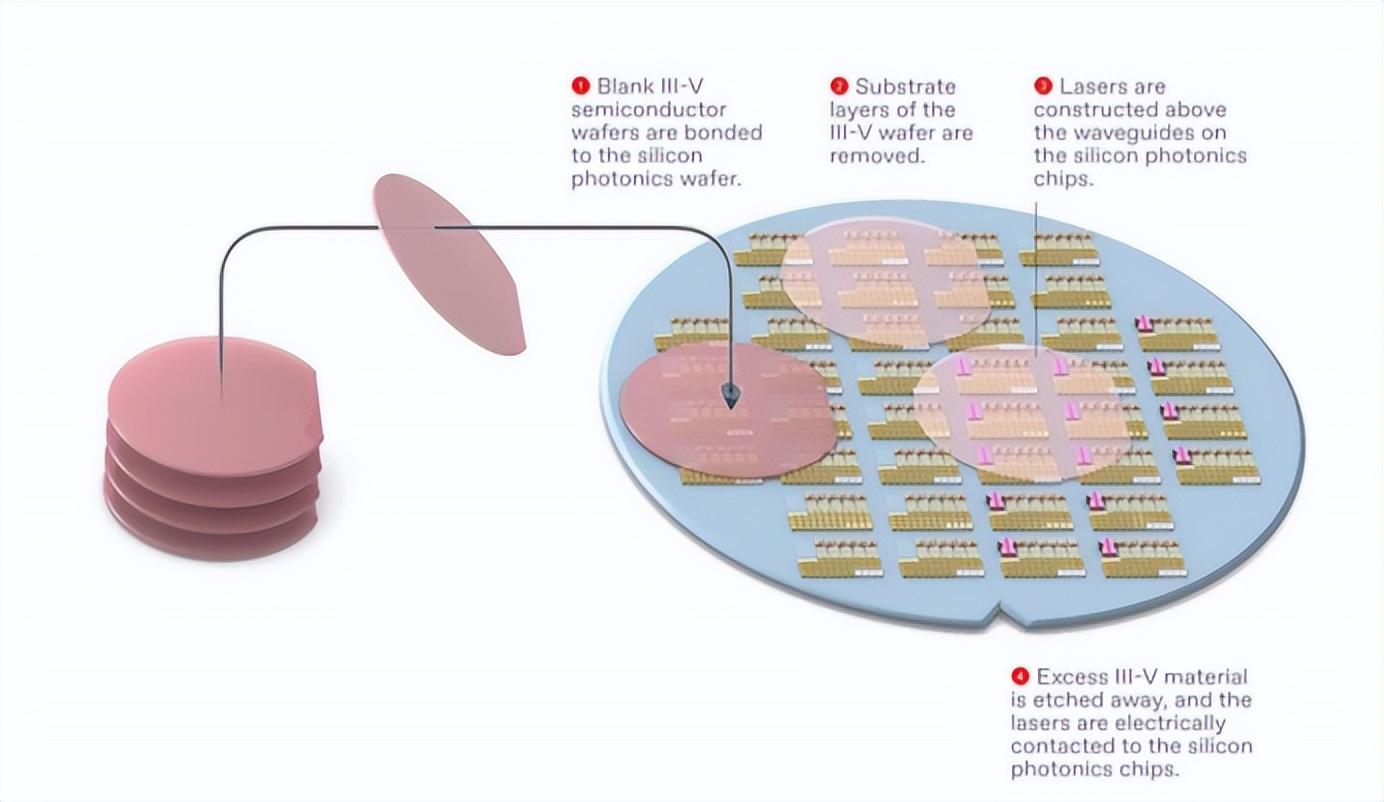

△图3:在die-to-wafer键合中,III-V族半导体(粉红色)的空白片被粘合到已经加工过的硅光子

晶圆上。III-V族材料在硅波导上方被加工成激光器件。然后将多余的III-V族材料蚀刻掉。(By Emily Cooper)

因为允许具有较大的对准偏差,使该技术能够一次转移数千个组件。因此,原则上,它应该允许比倒装芯片工艺更高的吞吐量,非常适合每单位面积需要集成大量III-V族组件的应用。

尽管转移印刷是制造microLED显示器的既定工艺,例如许多增强现实和虚拟现实产品的显示器制造需要转移印刷工艺,但该工艺尚未准备好用于打印激光器或光放大器。但imec正在努力实现它。

去年,imec使用转移印刷成功地将这种光源连接到包含硅光子波导、高速光调制器和光电探测器的晶圆上。他们还打印了波长可调超过45nm的红外激光器和适用于基于芯片的光谱系统的高脉冲能量器件。这些只是为了演示目的而制作,但看不出这种方法不能获得高产量的好结果的根本原因。因此,他们预计这项技术将在几年内准备好部署在生产线上。

Die-to-Wafer键合

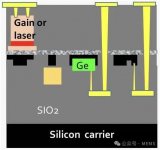

在上面讨论的两种技术中,将发光元件与其搭配的硅光子部件精确对准是关键的一步。但有一种技术,被称为III-V-to-silicon-wafer键合的形式,找到了解决这个问题的方法。该方案不是将已经构建的激光器(或其他发光元件)转移到加工过的硅晶圆上,而是将III-V半导体的空白die(甚至小晶圆)粘合到硅晶圆上。然后在相应的硅波导上构建所需的激光装置。

在转移的材料中,我们只对其中称为外延层的结晶III-V族材料薄层感兴趣。因此,在与硅晶圆结合后,其余的材料会被去除。然后,在与底层硅波导对准的外延层中使用标准光刻和晶圆级工艺制造激光二极管。最后将所有不需要的III-V族材料蚀刻掉。

英特尔公司的工程师在过去十年中开发了这种方法,并于2016年推出了第一批使用该方法构建的商业产品,即光收发器。该方法允许高吞吐量集成,因为它可以同时并行处理多个组件。与转移印刷一样,它在III-V族和硅材料之间使用倏逝波耦合,从而可以产生一个高效光接口。

III-V-to-silicon-wafer键合有一个缺点:您需要大量投资来建立一条生产线,该生产线可以使用用于制造直径为200毫米或300毫米的硅晶圆的工具来处理III-V族工艺步骤。这些工具与激光二极管代工厂中使用的工具非常不同,后者典型的晶圆直径要小得多。

单片集成

结合这两种不同材料的理想方法是直接在硅上生长III-V族半导体,这种方法被称为单片集成。这将消除任何粘合或对准的需要,并将减少III-V族材料的浪费量。但是,要使这种方法切实可行,还需要克服许多技术障碍。因此,imec和其他机构仍然在对这种方法继续进行研究。

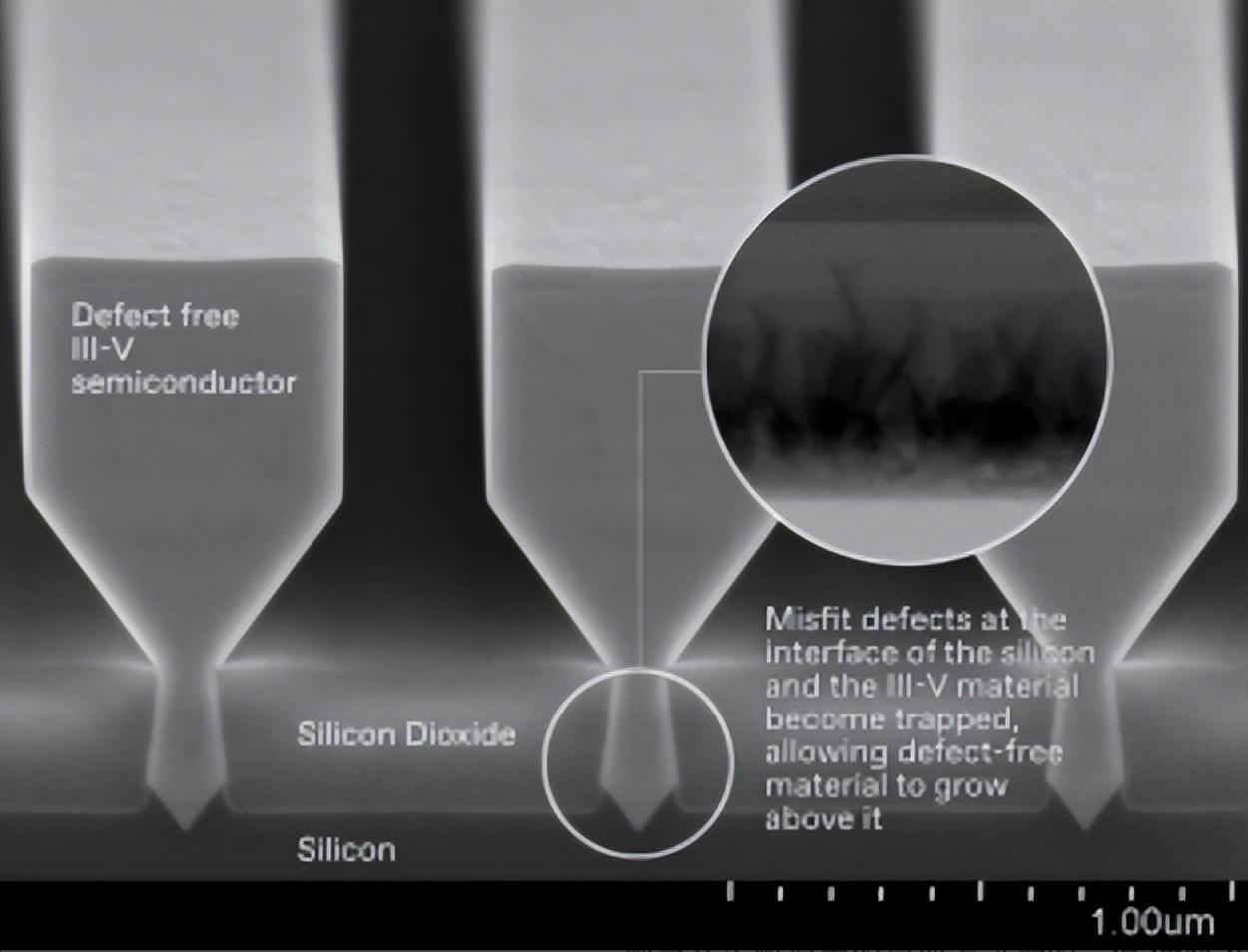

△图4:纳米脊工程在硅中特殊形状的沟槽中生长适合激光器件的半导体。沟槽的形状将缺陷(嵌入)捕获到远低于构建激光器件的区域。(Source:imec)

该研究的主要目的是制造具有低缺陷密度的结晶III-V族材料。根本问题是,硅中原子的晶格间距与感兴趣的III-V族半导体中原子的晶格间距之间存在相当大的不匹配-超过4%。

由于这种晶格不匹配,在硅上生长的每个III-V层都会产生应变。在添加几纳米的III-V族薄膜后,晶体中就会出现缺陷,以释放积聚的应变。这些“不匹配”的缺陷沿着穿透整个III-V族层的线条形成。这些缺陷包括开放的晶体键线和局部晶体畸变,这两者都会严重降低光电器件的性能。

为了防止这些缺陷扼杀激光器,必须把缺陷限制在远离激光装置的地方。因此,通常需要铺设一层几微米厚的III-V族材料,在下面的不匹配缺陷和上方的无应变区域之间形成一个巨大的缓冲区,然后在那里可以制造激光装置。加州大学圣巴巴拉分校的研究人员曾报告了使用这种方法取得的出色进展,展示了高效率基于砷化镓的量子点激光器,具有良好的可靠性寿命。

然而,这些实验只在小规模上进行。将该技术扩展到工业中使用的200毫米或300毫米晶圆上是困难的。添加厚缓冲层可能会导致各种机械问题,例如III-V族薄膜内部出现裂纹或晶圆弯曲。此外,由于有源器件位于如此厚的缓冲层之上,因此将光耦合到硅衬底中的底层波导具有挑战性。

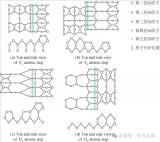

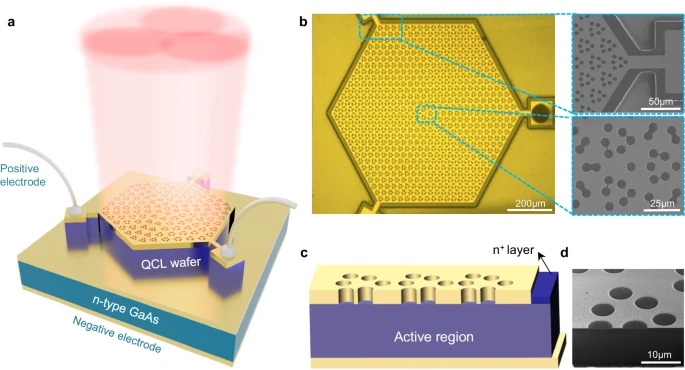

为了规避这些挑战,imec引入了一种新的单片集成方法,称为纳米脊工程(nanoridge engineering, NRE)。该技术旨在迫使缺陷形成在非常狭窄的空间内,从而可以在与底层硅的界面上方略高于100纳米的位置构建发光器件。NRE使用一种称为纵横比捕获的现象将缺陷限制在小区域。它首先在一层二氧化硅绝缘体内创建窄而深的沟槽。在沟槽的底部,绝缘体与硅相接触的地方,会有一个凹槽切入硅中,使空隙具有箭头形的横截面。然后在沟槽内生长一层薄薄的III-V族晶体,应变引起的失配缺陷被有效地捕获在沟槽侧壁上,防止这些缺陷线进一步渗透。沟槽被填满后,生长物继续在沟槽上方形成更大的III-V族材料纳米脊。纳米级脊中的材料足够好,没有缺陷,因此可用于制作激光器件。

大多数关于单片集成的研究都是在改进单个器件并确定其失败原因的层面上进行的。但imec在采用该技术的晶圆级集成方面已经取得了实质性进展,在300毫米硅试验生产线中生产了高质量的基于GaAs的光电二极管。下一个里程碑将是演示基于与光电二极管类似设计的电泵浦激光器。纳米脊工程仍在实验室开发中,但如果它有效,无疑将对这个行业产生重大影响。

硅上激光器的前景

未来几年,这里讨论的每种方法肯定会进一步发展,预计它们最终将共存以满足不同的应用需求和用例。

倒装芯片激光器组装,因为相对适中的生产成本和成熟性,将使其近期产品化成为可能,对于每个PIC只需要一个或两三个激光器的应用(例如数据中心中使用的光收发器)特别有吸引力。此外,这种方法固有的灵活性使其对需要非标准激光波长或不常见光子技术的应用具有吸引力。

对于每个PIC需要多个激光器或放大器的大批量应用,转移印刷和die-to-wafer键合可提供更高的制造吞吐量,更小的耦合损耗,并有可能进一步降低成本。由于生产投入成本很高,因此这些技术适合的应用必须具有很大的市场。

最后,在硅上直接进行III-V外延,如NRE纳米脊技术,代表了激光器件集成的最终水平,但还需要在材料质量和晶圆级集成方面取得进一步进展才能释放其潜力。

审核编辑 黄宇

-

芯片

+关注

关注

456文章

50884浏览量

424150 -

封装

+关注

关注

126文章

7932浏览量

143040 -

激光器件

+关注

关注

0文章

18浏览量

7289

发布评论请先 登录

相关推荐

高功率半导体激光器的散热秘籍:过渡热沉封装技术揭秘

激光显示上游核心器件系列:激光器

大研智造 半导体激光器在电子焊接中的应用及优势

石墨烯在激光器中的应用

Scintil Photonics集成激光器的PIC将在Tower实现量产

光纤耦合激光器是什么 光纤耦合激光器支持多波长激光输出吗?

常见激光器类型

将激光器件与硅集成的方法探讨

将激光器件与硅集成的方法探讨

评论