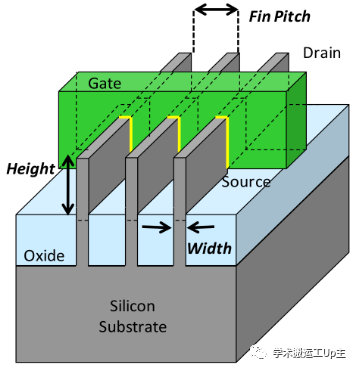

今天分享另一篇网上流传很广的22nm 平面 process flow. 有兴趣的可以与上一篇22nm gate last FinFET process flow 进行对比学习。 言归正传,接下来介绍平面工艺最后一个节点22nm process flow。

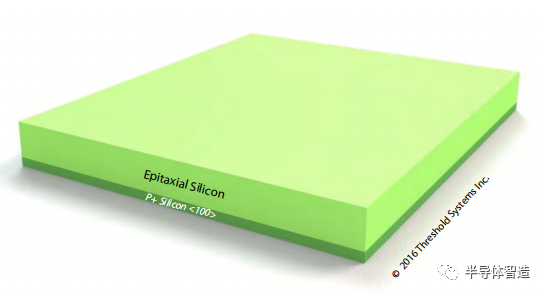

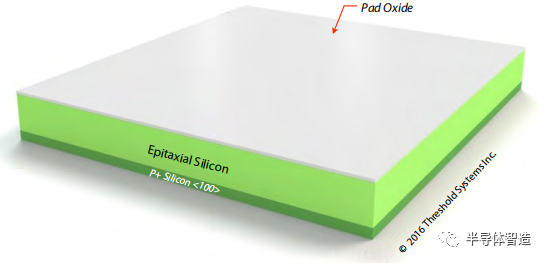

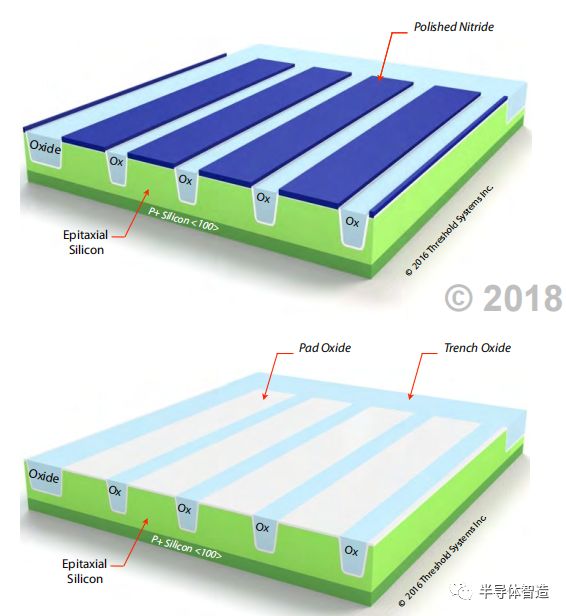

Pad Oxide Growth

首先是P型衬底上面有一层外延生长的Si,然后再生长一层Pad Oxide。此氧化层充当后面SiN和底层硅表面之间的应力缓冲层,并防止SiN对硅表面造成损伤。

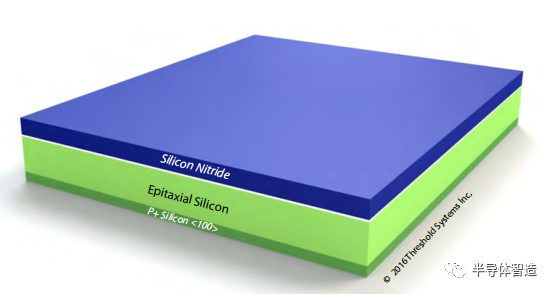

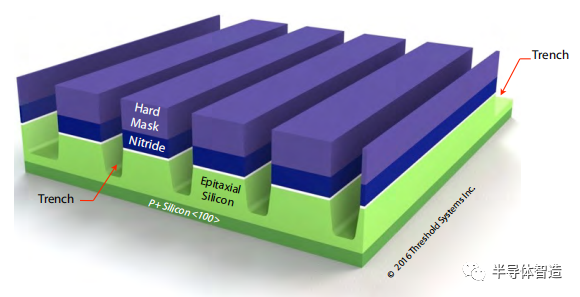

2.Nitride Barrier Deposition

接下来,通过化学气相沉积(CVD)方法沉积一层厚度约1,200Å左右的SiN。然后,将晶片在SC1溶液中清洗。

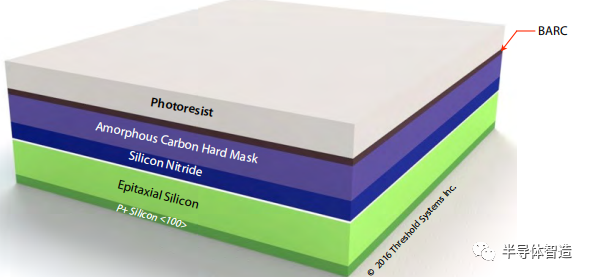

3.Hard Mask Deposition & Lithography

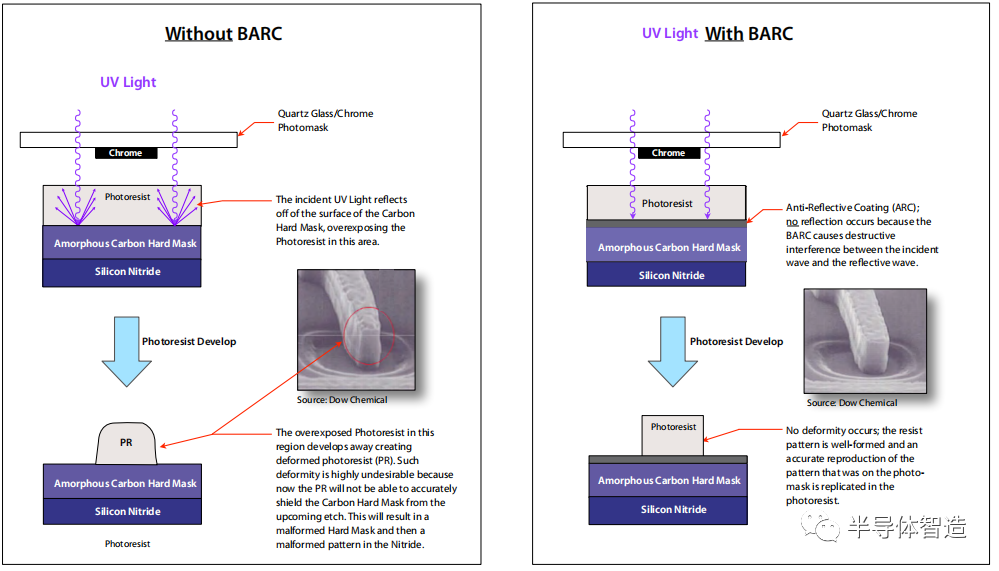

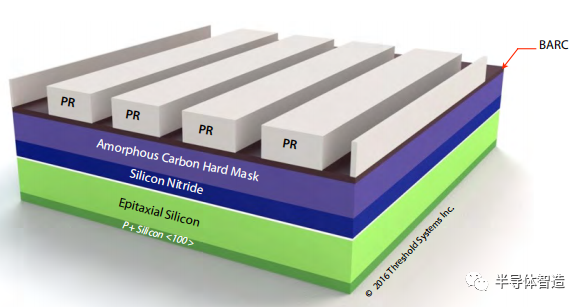

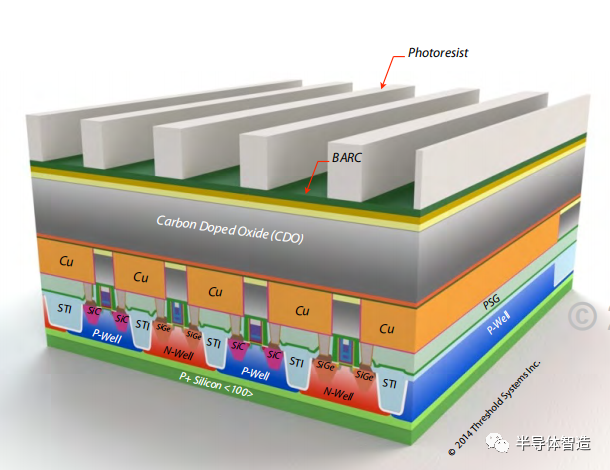

使用化学气相沉积(CVD)方法,在晶片表面沉积一层厚度为2,000Å的Amorphous Carbon(A-C)。然后在其上沉积一层厚度为500Å的底部防反射涂层(Bottom Anti-Reflective Coating, BARC)。A-C将充当一种硬掩膜(hard mask)。接下来,将约3,000Å的光刻胶涂敷在晶片上,并进行烘烤(soft baked)。

Bottom Anti-Reflflective Coatings (BARC )

4.Hard Mask Defifinition

然后对其进行曝光和显影。将Mask上的pattern转移到Hard mask上。

5.Photoresist Strip & Trench Etch

用SPM去除PR,并继续往下刻蚀,形成STI的结构。

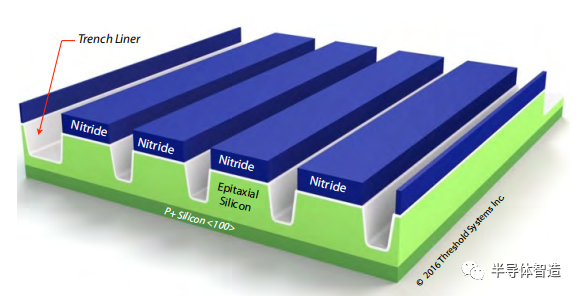

6.Trench Liner Growth

晶片再次经过清洗(HF/SC1/SC2),然后在沟槽中生长出100Å厚度的二氧化硅层。这个氧化层被称为“沟槽衬垫”,有助于缓解沟槽上下角附近硅材料的应力。

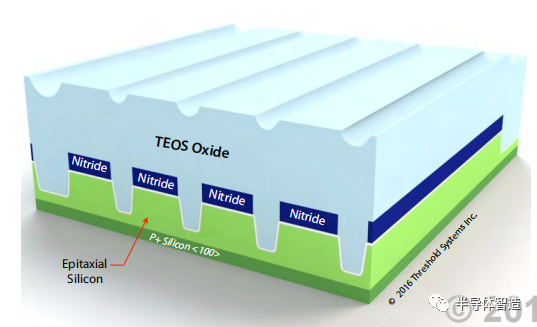

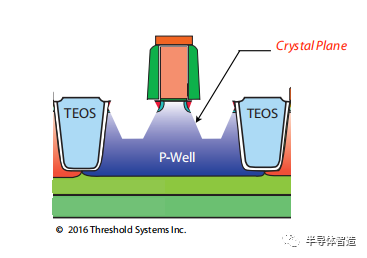

7.Trench Fill

然后沉积了4,000 Å 的TEOS(四乙基正硅酸酯)氧化物。TEOS是通过化学气相沉积(CVD)沉积的氧化物,与生长(热)氧化物相对。它的主要优势是可以快速沉积厚度较大的氧化物。它的主要缺点是沉积的TEOS氧化物不如生长的氧化物致密。接下来,晶片在1,000˚C加热20分钟,使TEOS变得更加致密,更具抗湿法蚀刻的能力。

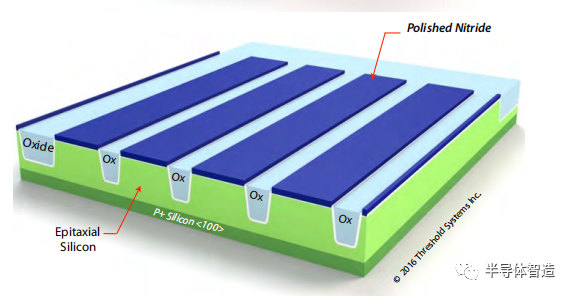

8.Oxide Polish

晶片经过化学机械抛光(CMP)后。非常坚硬的氮化硅层起到了CMP停止作用。在氧化物被抛光后,表面上起CMP停止作用的薄层氮化物必须被去除。

9.Nitride Strip

在CMP后,表面的薄层氮化物必须被去除(通过将晶片浸入热酸140ºC的磷酸中20分钟来去除残留的氮化硅。磷酸对氮化硅具有较高的选择性,而不会侵蚀氧化物)。

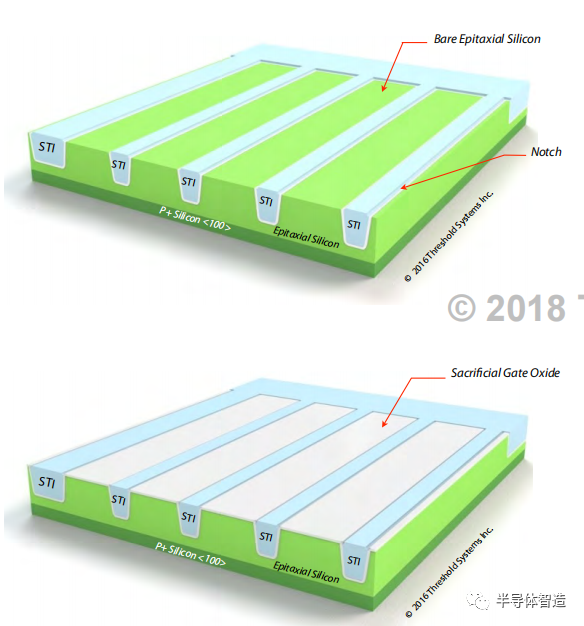

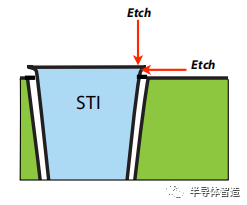

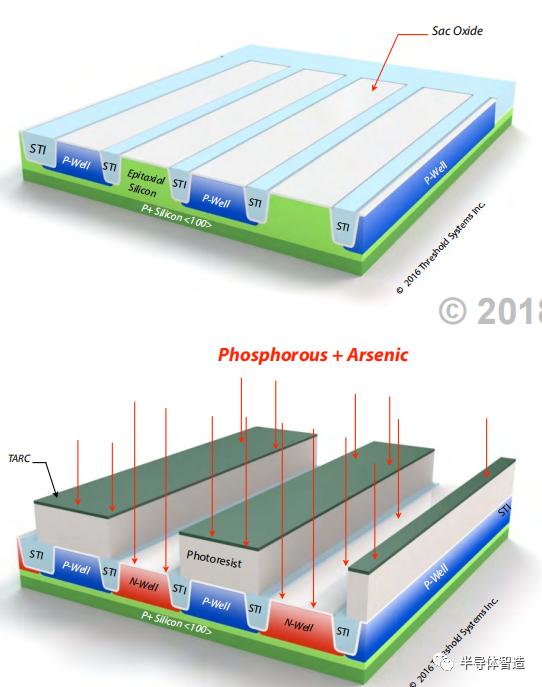

10.Pad Oxide Strip & Sacrifificial Gate Growth

接下来,将晶片浸泡在氢氟酸中,去除Pad Oxide。Pad Oxide去除过程中会优先去除沟槽角落处的氧化物,因为这些区域受到应力并且蚀刻速度更快。这会导致沟槽的侧面出现“凹槽”(Divot),可能在后续过程中引起问题。

然后晶片在SC1/SC2中进行清洗,并生长出50 Å的牺牲栅氧化物(Sac Ox)。牺牲栅氧化物也起到了屏蔽氧化物(Screen Oxide)的作用。

注:Pad Oxide的去除在沟槽的角落处优先去除了氧化物,主要是因为STI(shallow trench isolation)氧化物是一种沉积氧化物,比Pad Oxide(生长热氧化物)要软得多。此外,STI 氧化物的角落区域受到机械应力影响,而受应力影响的微结构腐蚀速度更快。最后,在Pad Oxide蚀刻过程中,STI 氧化物的锐利角落受到两侧的攻击,加速了这些角落的退让。这种优先腐蚀导致沿着沟槽侧壁产生“凹槽”,可能在后续过程中引起问题。

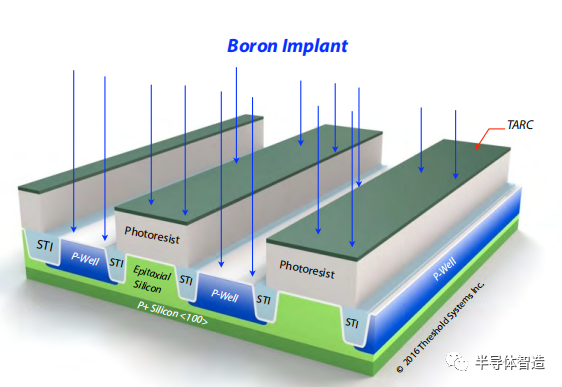

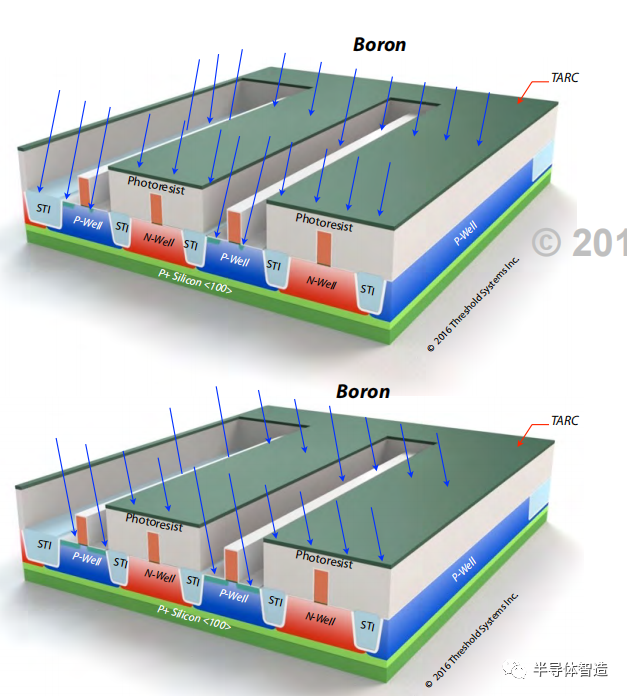

11.P-Well Implant

接下来,晶片被注入硼元素以建立反向掺入的P-Well。

12.Photoresist Strip and N-Well Implant

去完光阻,同理进行N-Well区的定义,主要进行磷和砷的注入。

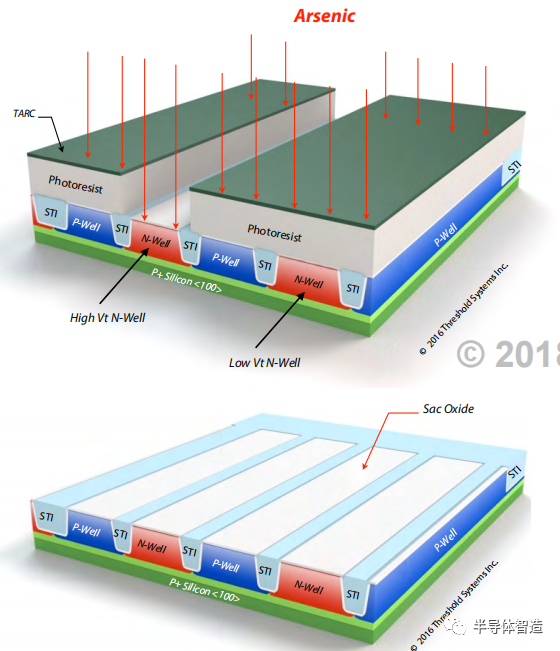

13.High Vt N-Well Vt Adjust

高压N-Well接受As元素注入,使其具有比低压N-Well更高的阈值电压(Vt)。完成后并去胶。

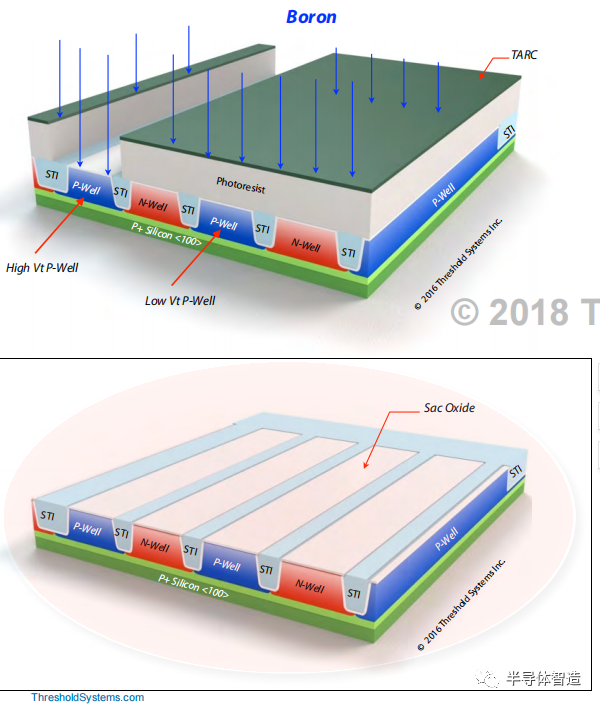

14.High Vt P-Well Vt Adjust & Well Anneal

同理,高压P-Well接受B元素注入,使其具有比低压P-Well更高的阈值电压(Vt)

在完成井注入之后,晶片经过快速热退火(RTA),在1,000ºC下加热10秒钟,以激活注入井中的杂质元素。退火过程使掺杂原子电活性,并修复注入过程中对硅材料造成的损伤。

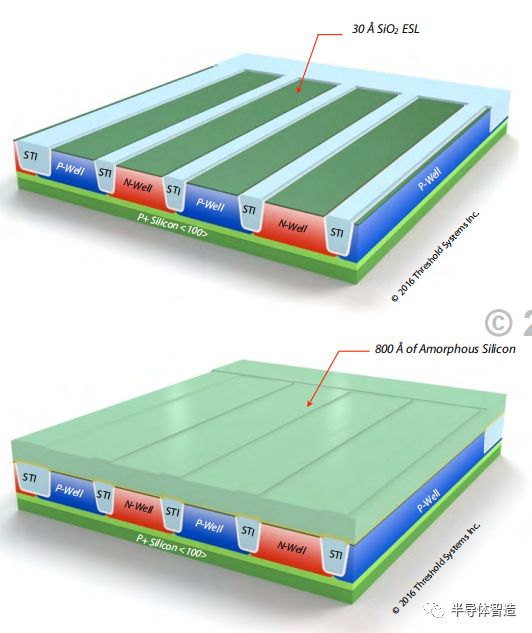

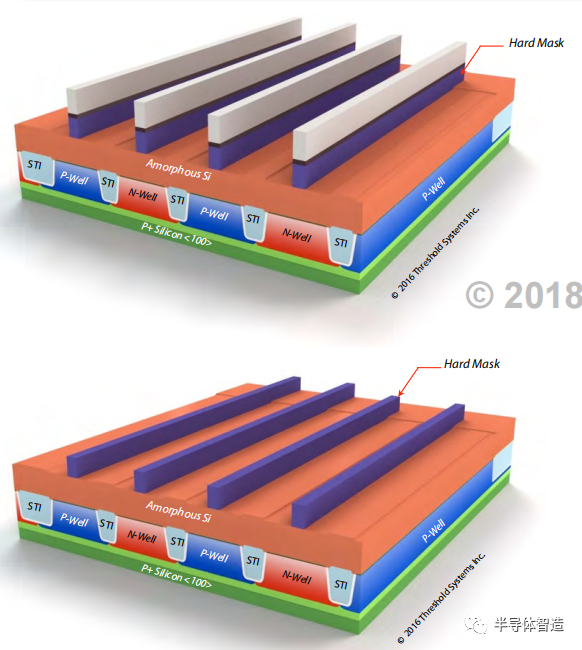

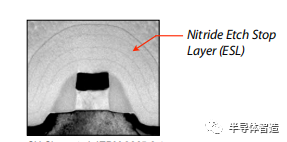

15.Oxide ESL Growth & AmSi Deposition

在晶片的表面上生长一个厚度为30Å的SiON热层氧化物,形成一个薄的刻蚀停止层(Etch Stop Layer,ESL)。当非晶硅栅极支撑柱(尚未沉积)被刻蚀掉时,这层氧化物将作为刻蚀停止层来保护晶体管通道。

请注意,在流程中的这个阶段没有进行Hi-k介电沉积。

采用化学气相沉积(CVD)技术沉积了厚度为800Å的非晶硅(AmSi)。这里的非晶硅是未掺杂的。在进行图案化和刻蚀后,非晶硅形成了牺牲性栅极支撑柱。

请注意,在非晶硅栅极电极下方没有金属栅极。

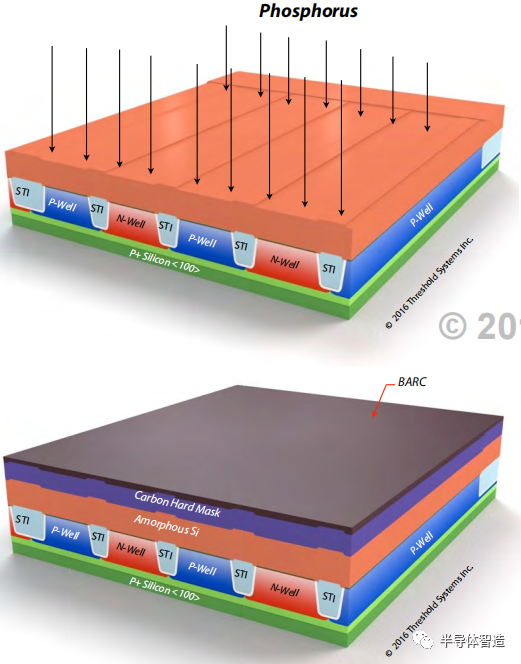

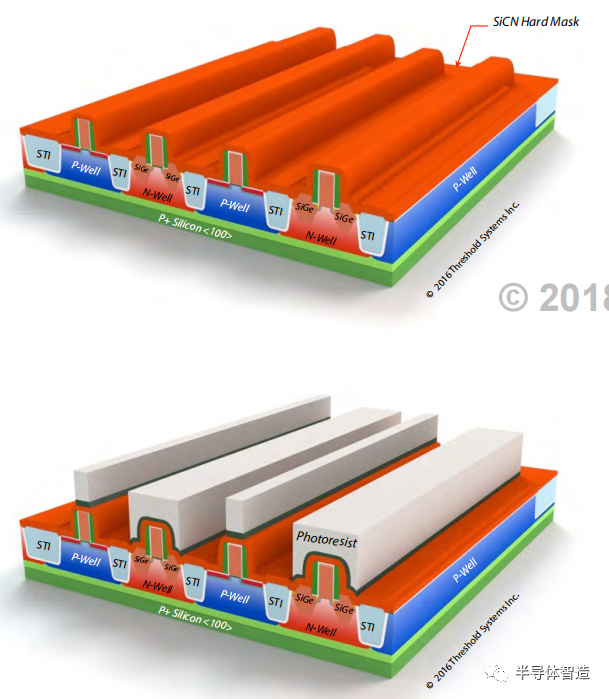

16.Amorphous Silicon Dope & Hard Mask Dep

非晶硅通过注入磷(Phosphorus)进行掺杂,以使其具有导电性。栅电极是牺牲性的,将在后续工艺中去除。掺杂栅电极有助于其去除,但并非必要。

接下来沉积了厚度为1,500Å的非晶碳硬膜和厚度为300Å的BARC层。

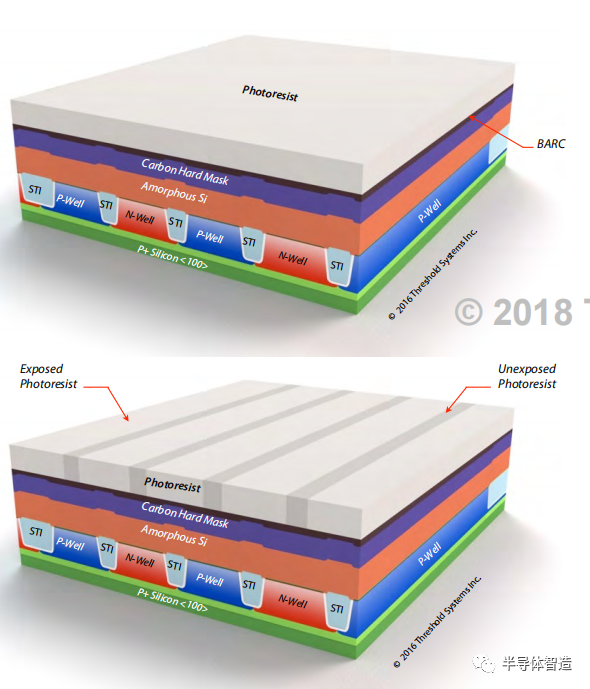

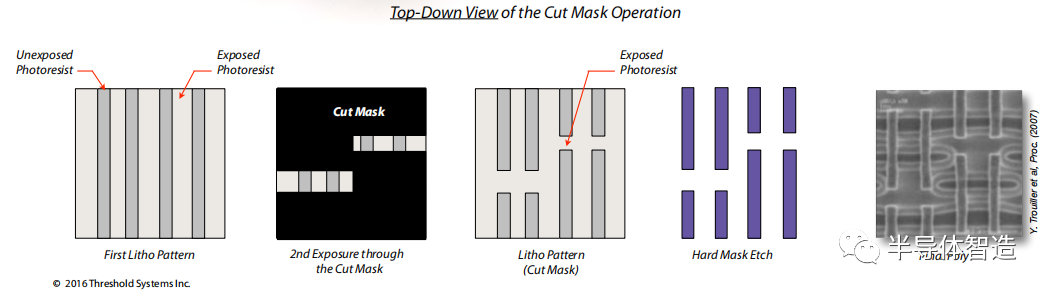

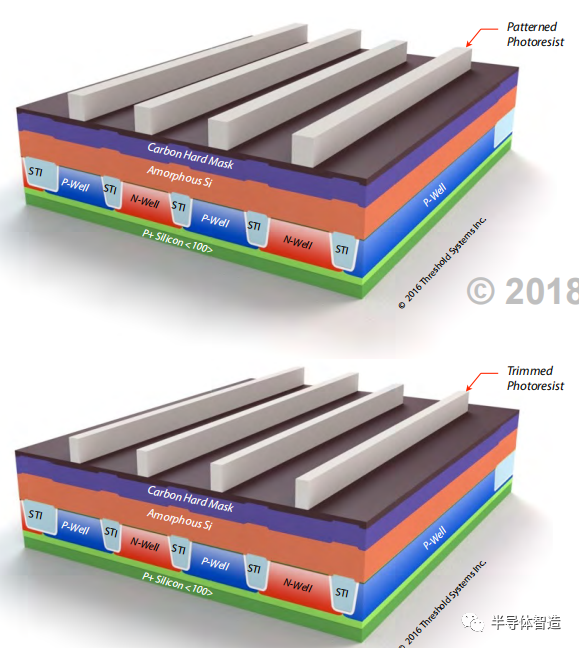

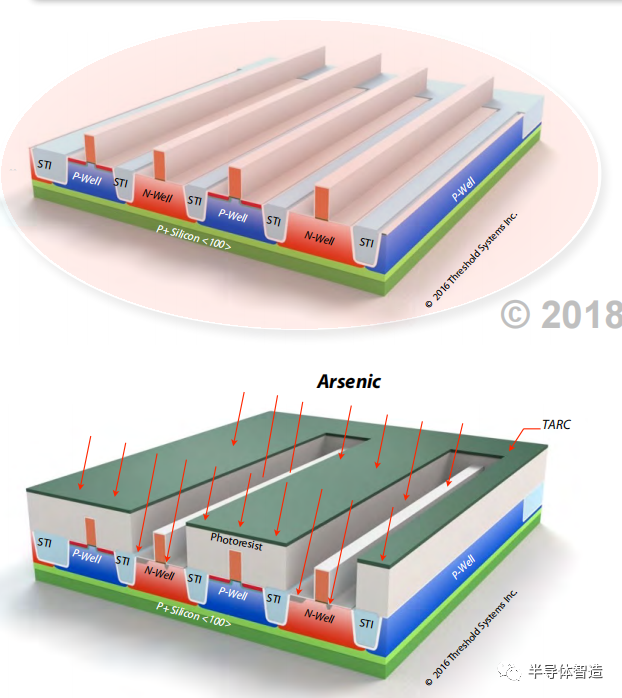

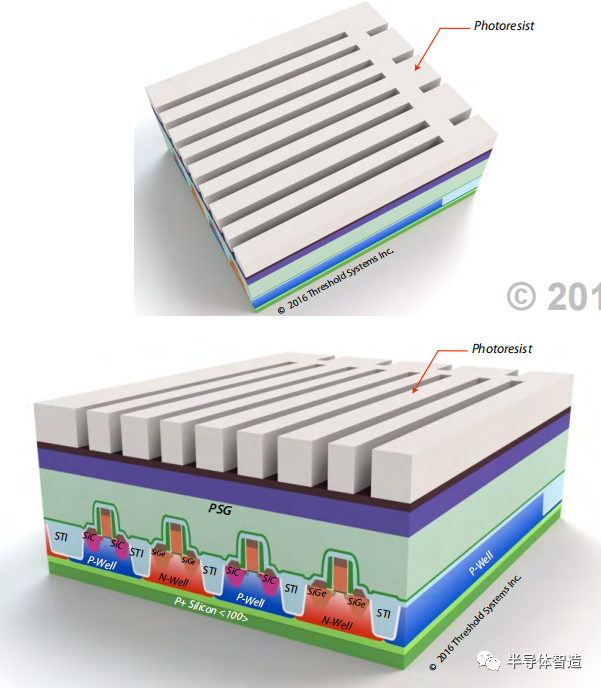

17.Photoresist Deposition & 1st Patterning

接下来,晶片会先在HMDS中进行预处理,然后涂覆BARC(底部抗反射涂层),光刻胶和光刻图案。这是整个流程中最关键的光刻操作。它生成一系列平行线,接下来会通过随后的光刻操作中的切割掩模来进一步定义这些线。

然后,使用一个光栅掩模对晶片进行曝光。该掩模只在一个方向上打印直线。光刻胶尚未进行显影。

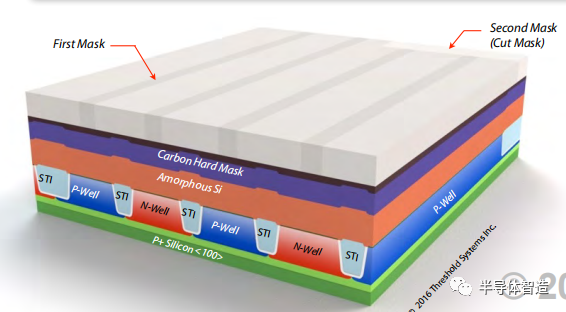

18.Cut Mask 2nd Patterning

接下来,通过一个“切割掩模”对光刻胶进行曝光,该掩模将未显影的光刻胶暴露在与第一个掩模方向垂直的方向上。这样可以沿着这个轴线暴露光刻胶,并允许将贯穿整个芯片的连续光栅线进行切割。

19.Photoresist Trim Process

在控制的氧等离子体下进行曝光,该氧等离子体会对图案化的光刻胶进行各向异性刻蚀。这会导致光刻胶尺寸缩小到目标尺寸。这个过程被称为“光刻胶修整,修整后的光刻胶线条现在更窄了,可以用来定义更窄的栅极电极。

光刻胶修整是一种技术,可以制造非常窄的光刻胶线条(因此也是窄的栅极电极线条),其尺寸比光学打印的光刻胶线条更小。

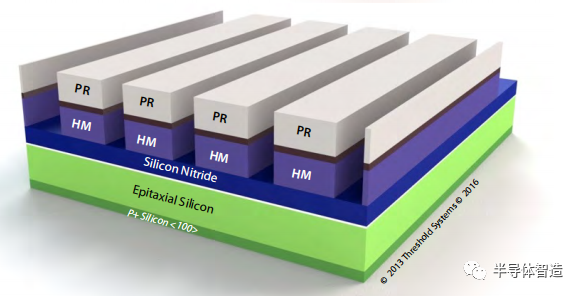

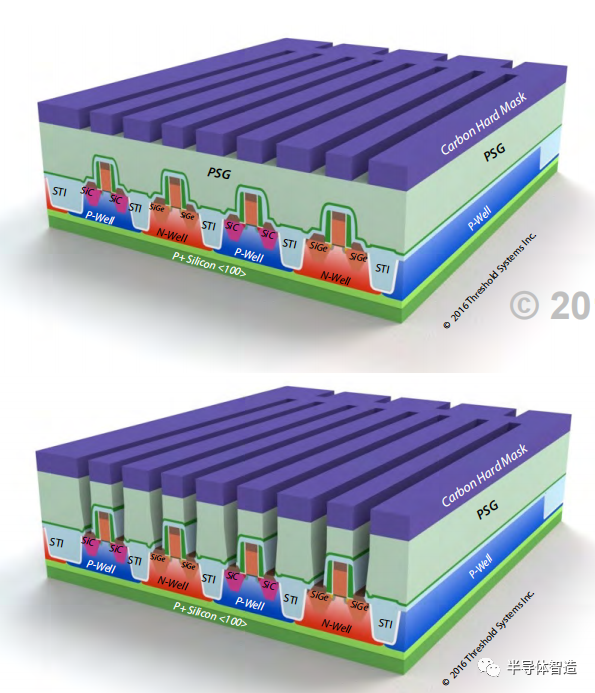

20.Hard Mask Etch & Photoresist Strip

通过高度各向异性的刻蚀过程,对非晶碳硬掩模进行刻蚀,刻蚀过程会停在非晶硅处,刻蚀完成后去掉PR。

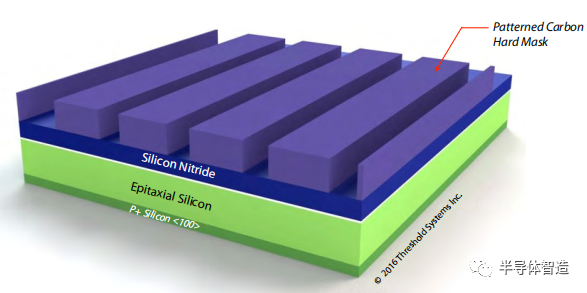

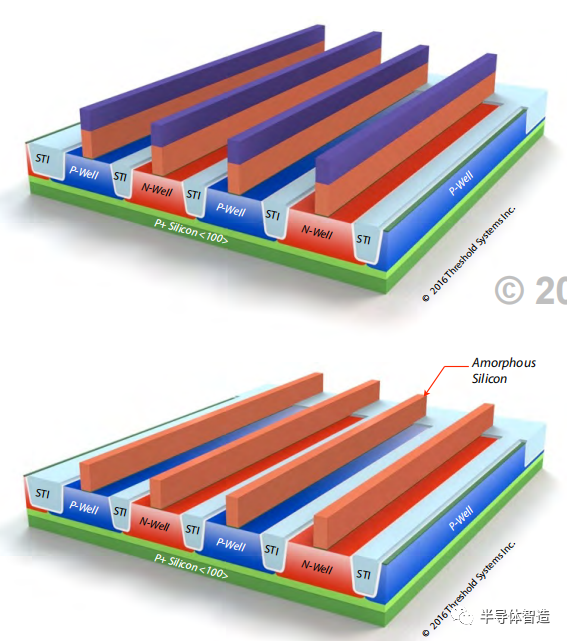

21.Amorphous Silicon Etch & Hard Mask Strip

然后使用高度各向异性的刻蚀recipe,将图案从硬掩模转移到非晶硅中。

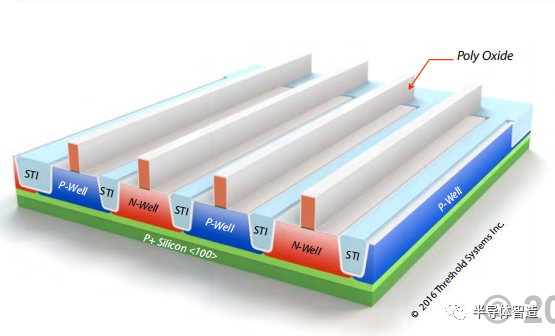

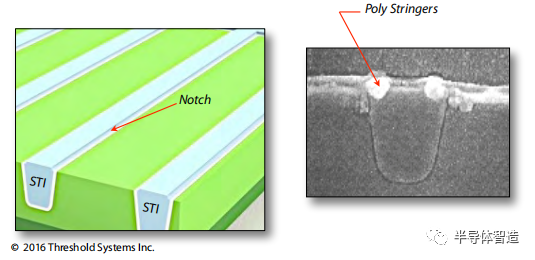

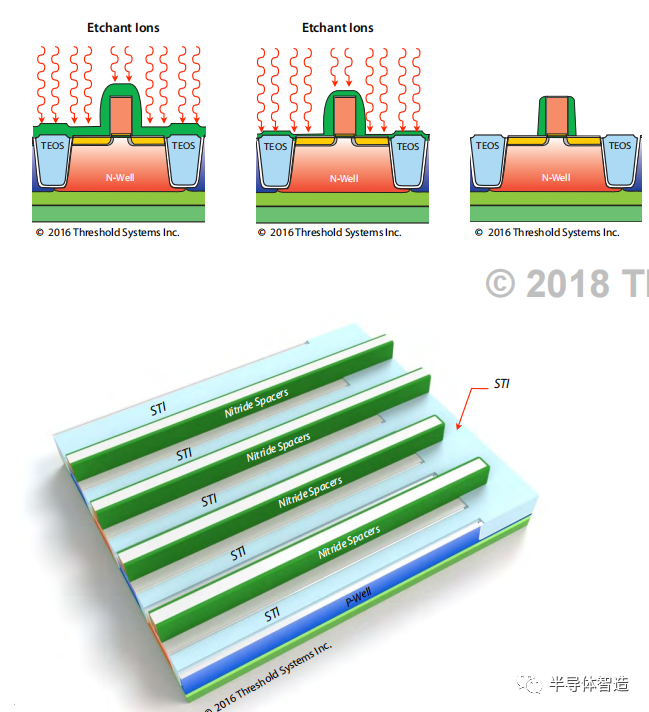

22.Poly Oxidation & Poly Stringers

首先生长出15 Å thermal poly oxide。随后会沉积15 Å的CVD oxide)。这两层氧化硅构成了所谓的“偏移间隔层”(Offset Spacer)(有时也称为“Spacer0或Spacer1)。

最初的Pad氧化物去除(在填充沟槽和去除氮化物之后进行了几个操作)优先从沟槽角落处去除氧化物,从而在沟槽的两侧形成了沿着全程都存在的“凹槽”,有利于多晶硅线的形成。

多晶硅线在多晶硅刻蚀操作的最后阶段形成。这个刻蚀过程的最后阶段是高度选择性的过刻,旨在去除源/漏区域和凹槽中剩余的少量多晶硅。如果这个刻蚀阶段没有经过精心设计,厚的多晶硅线将留在沟槽凹槽中,并形成意外的导电通路,导致相邻晶体管短路。

因此,尽量减小凹槽的尺寸以便于轻松去除多晶硅线非常重要。

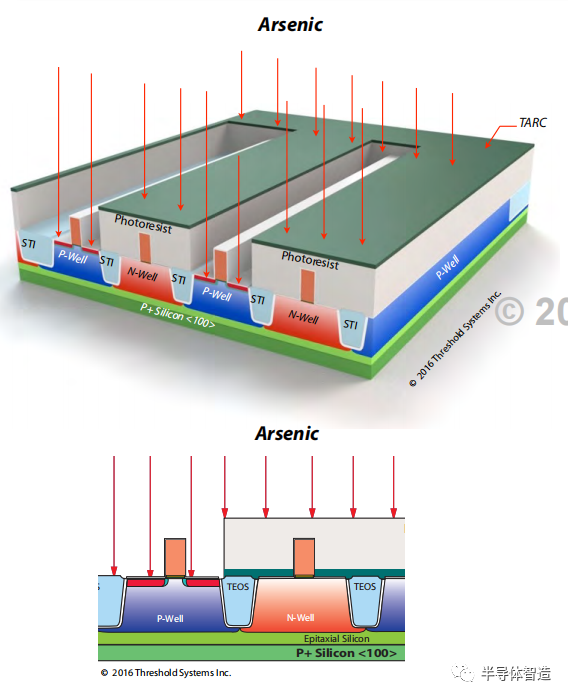

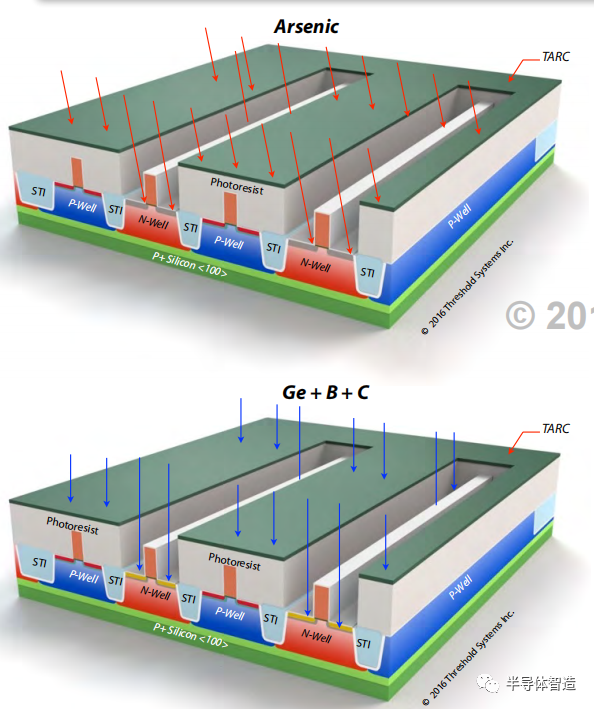

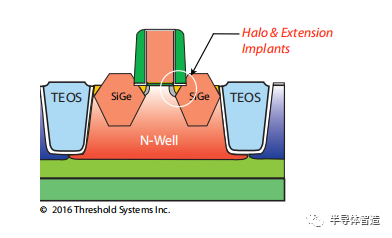

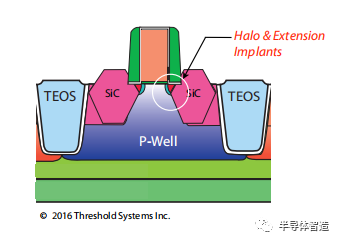

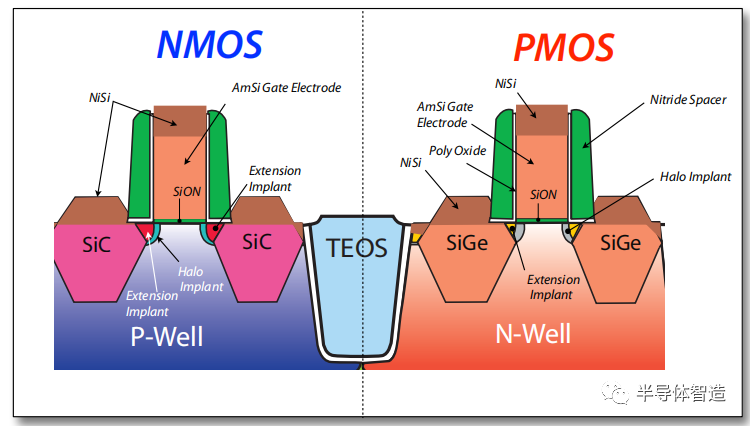

23.NMOS Halo Implant

对高阈值P-Well施加硼离子注入Halo注入的深度约为150-200 Å。

24.NMOS Extension Implant

将砷(Arsenic)延伸注入到P-Well区域。这个注入确定了NMOS晶体管的延伸注入。

延伸注入的深度与Halo注入大致相同(对于20纳米器件大约为150-200 Å)。

25.NMOS Anneal & PMOS Halo

接下来,晶圆经历快速热处理(约950摄氏度的瞬时峰值加热1秒,然后以约1,350摄氏度的闪光退火1-3毫秒),以激活NMOS的延伸和Halo注入。在某些工艺流程中,闪光退火会被一个相同温度(约1,350摄氏度)的部分熔融激光退火所取代。延伸注入的位置决定了NMOS晶体管的最终等效长度(Leff)。

退火过程使掺杂原子电活化,并退火修复了硅中在注入过程中产生的损伤。

26.PMOS Halo & Extension

同理,进行PMOS Halo处延伸注入,

对N-Well区域进行了锗(Germanium)的预非晶华离子注入,然后施加低能量的Boron的延伸注入然后进行碳(Carbon)注入,以获得更好的延伸注入剖面。

预非晶华离子注入限制了硼原子的通道化现象,而硼注入则确定了PMOS晶体管的延伸注入部分。

27.PMOS Anneal

先前工序中的光阻已经被脱除。然后晶圆进入快速热处理(约950摄氏度的瞬时温度升高,持续约1秒,随后进行约1,350摄氏度的快速退火处理,持续1-3毫秒),以激活PMOS扩散和外围注入。在某些工艺流程中,闪光退火被以同样温度(约1,350摄氏度)的次熔激光退火所替代。扩散注入的位置决定了PMOS晶体管的最终有效通道长度(Leff)。退火过程使掺杂原子电性活化,并消除硅材料在注入过程中的损伤,对Idsat(饱和漏电流)有巨大影响。

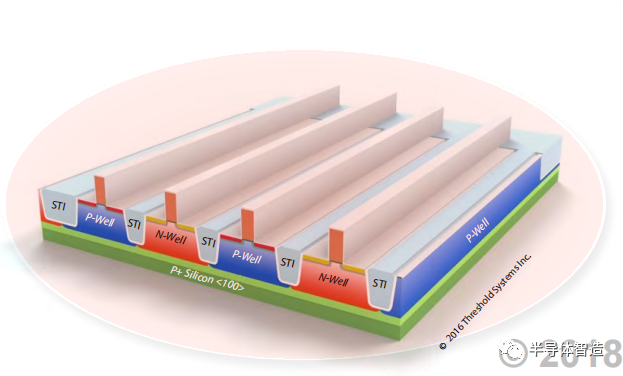

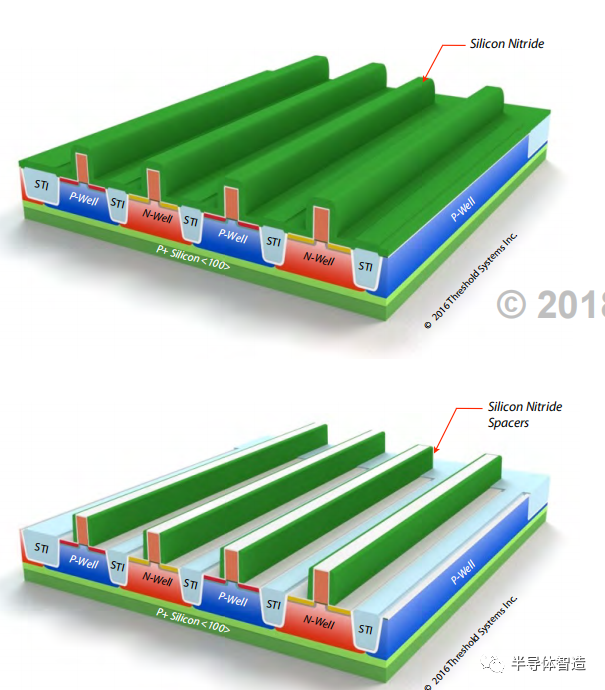

28.Nitride Spacer Deposition and Etch

在晶圆的表面上沉积了一个厚度为150 Å的均匀层硅氮化物。由于硅氮化物具有良好的复合性,它在栅极的侧壁处最厚。

经过高度各向异性的腐蚀,所有水平表面上的硅氮化物被去除,但在栅极侧面保留了硅氮化物侧壁间隔物,因为这里的硅氮化物最厚。硅氮化物侧壁间隔物在后续的接触注入过程中起到微型注入掩膜的作用。

29.Nitride Spacer Etch

由于腐蚀过程高度各向异性(只朝一个方向进行腐蚀,即向下),所以除了栅极侧壁上的硅氮化物之外,硅氮化物在其他地方都被清除掉了,因为栅极侧壁上的硅氮化物是最厚的部分。

高度各向异性的腐蚀过程从所有水平表面去除了硅氮化物,但在栅极侧面保留了硅氮化物侧壁间隔物。这些硅氮化物侧壁间隔物在后续的接触注入过程中充当微小的注入屏蔽层。

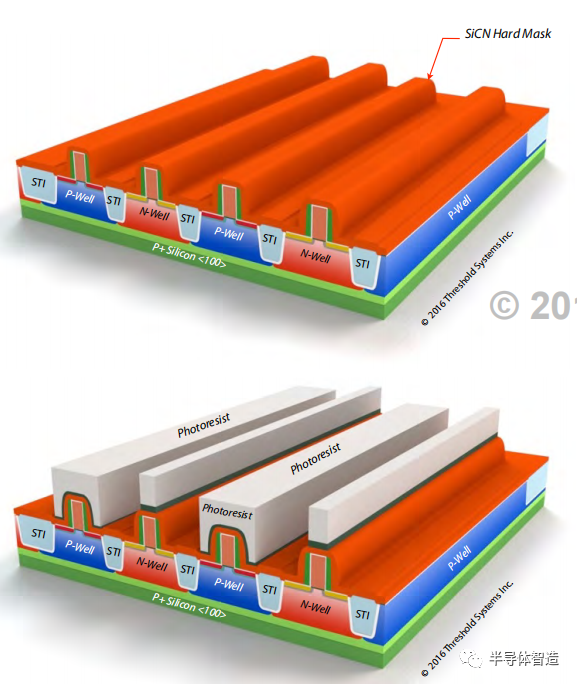

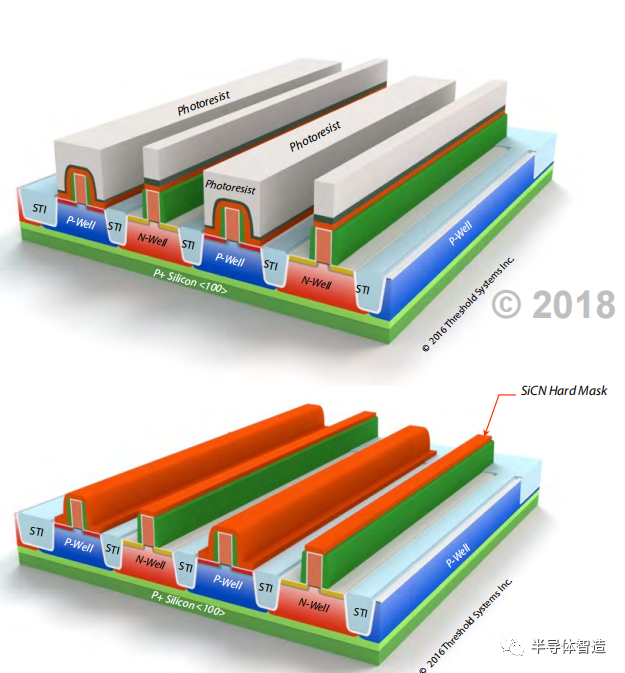

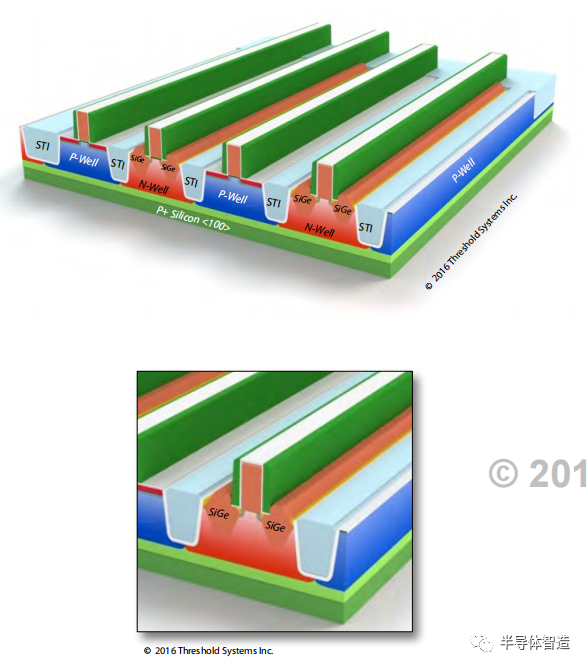

30.PMOS Hard Mask Deposition & Patterning

接下来,在晶圆的表面上沉积300Å的SiCN。

31.PMOS Hard Mask Etch & Photoresist Strip

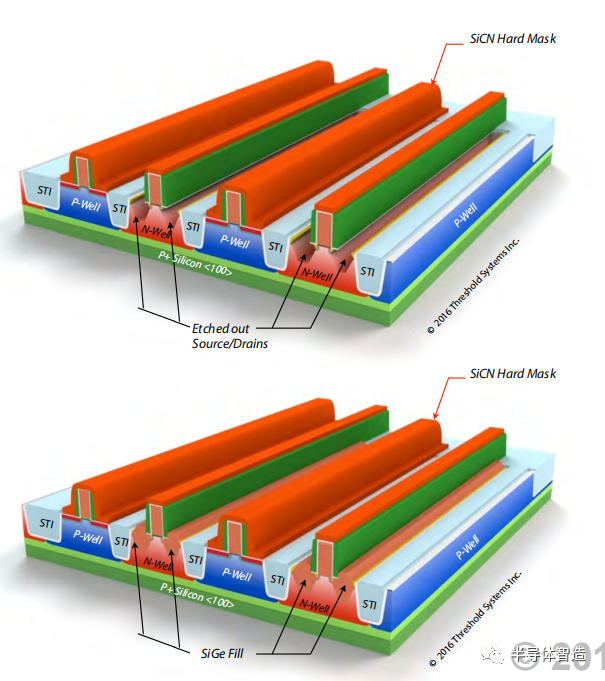

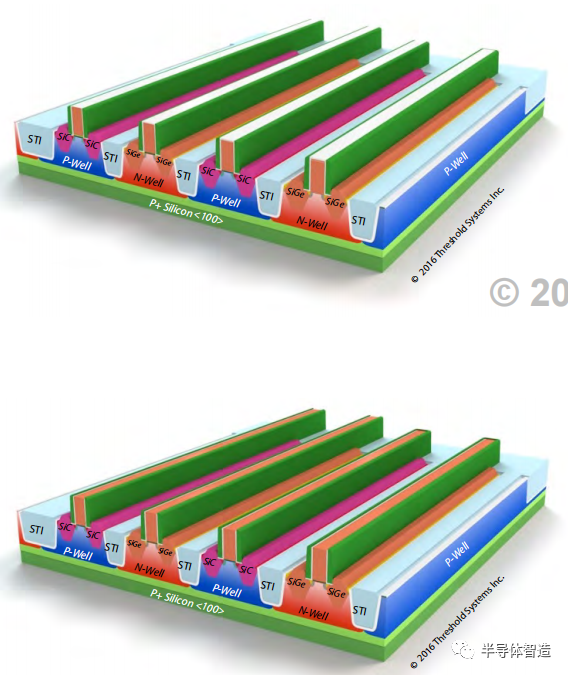

32.PMOS Source/Drain Etch & SiGe Fill

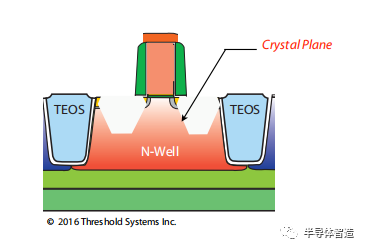

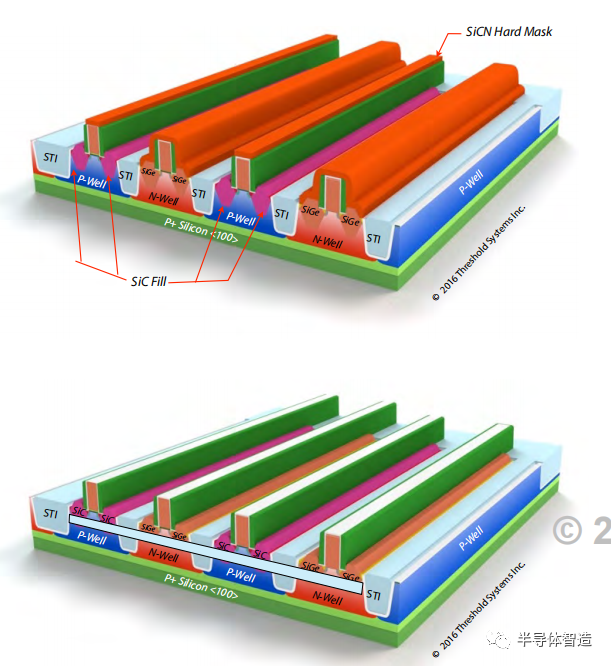

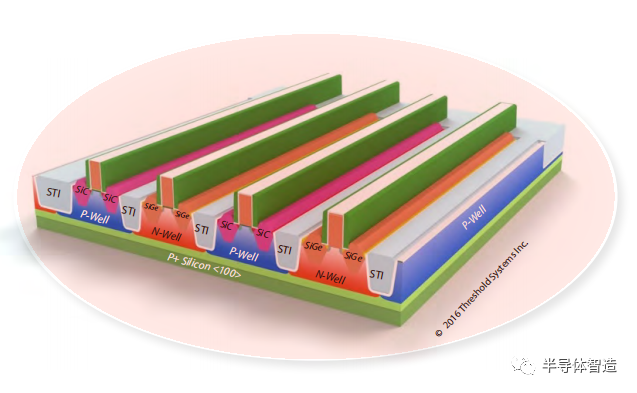

使用NH4OH溶液对PMOS晶体管的暴露源/漏区进行湿腐蚀,该溶液能够沿着晶体学平面进行腐蚀。P-衬底和栅极由SiCN保护。腐蚀过程不会影响STI沟槽中的暴露氧化物。

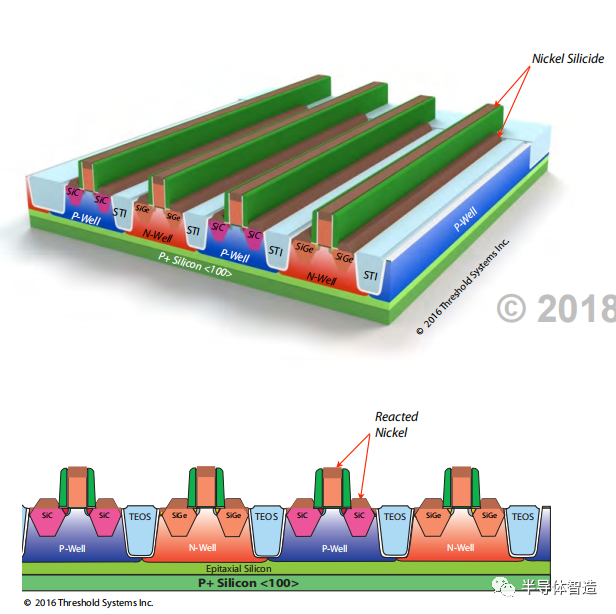

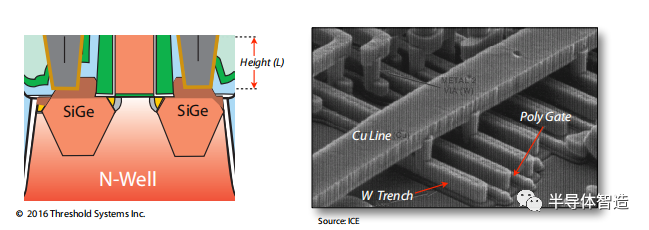

然后,晶圆会经过选择性外延沉积SiGe。SiGe只能在暴露的硅表面上成核,这意味着它只会形成在PMOS的源/漏区域(晶圆的其他部分由氮化物或氧化物构成,或者覆盖有SiCN)。SiGe的Ge含量约为40%,它会对PMOS通道施加高度压缩应变,极大地提高通道内电洞的迁移率,从而增加Idsat。

随着外延SiGe的沉积,它会掺杂大量的硼,使其成为P型硅。

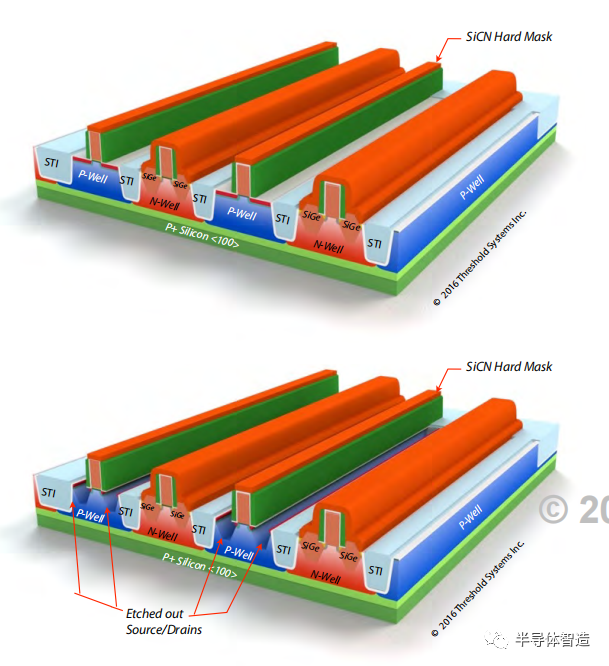

33.Hard Mask Strip

剩余的SiCN硬膜会在各向同性腐蚀中被去除。下图显示了PMOS器件的SiGe替代源/漏区的近距离视图。请注意,尽管源/漏区已被替换,但扩展和晶团注入仍然存在。

34.NMOS Hard Mask Deposition & Patterning

接下来,将在晶圆表面上沉积300Å的SiCN薄膜。

35.NMOS Hard Mask Etch + Source/Drain Etch

使用HF湿腐蚀剂去除源/漏区上的氧化物。然后,使用NH4OH溶液进行湿腐蚀,该溶液会沿着晶体学面去除PMOS晶体管的暴露的源/漏区。

36.NMOS Source/Drain Selective SiC Dep

然后,晶圆会经过选择性外延沉积SiC的过程。SiC只会在暴露的硅表面上形成晶核,这意味着它只会在PMOS源/漏区域形成(晶圆的其他部分由氮化物或氧化物组成,或者覆盖有SiCN)。SiC对NMOS沟道施加非常强的拉应力,并增加电子的迁移率。这增加了NMOS器件的Idsat。随着SiC的沉积,它会被磷掺杂以使其成为N型材料。

适当施加应变到晶体管通道,可以显著增加晶体管的驱动电流,从而提高晶体管的速度。为了实现这一效果,PMOS晶体管通道必须处于压应变状态,而NMOS晶体管的通道则处于拉应变状态。有多种方法可以在晶体管通道中引入压应变或拉应变,但最有效的方法是用掺有具有较大或较小晶格常数的原子的硅外延替换晶体管的源/漏区。这分别引入了压应变或拉应变。如先前提到的,在每个新节点中,PMOS SiGe源/漏区的Ge含量增加,以保持对晶体管通道的压应力(目前在20nm节点上为55%的Ge含量)。另一种技术是将SiGe晶体的尖锐边缘靠近通道,以引发更多应力。这在32nm节点上已经实施。

适当施加应变到晶体管通道,可以显著增加晶体管的驱动电流,从而提高晶体管的速度。为了实现这一效果,PMOS晶体管通道必须处于压应变状态,而NMOS晶体管的通道则处于拉应变状态。有多种方法可以在晶体管通道中引入压应变或拉应变,但最有效的方法是用掺有具有较大或较小晶格常数的原子的硅外延替换晶体管的源/漏区。这分别引入了压应变或拉应变。如先前提到的,在每个新节点中,PMOS SiGe源/漏区的Ge含量增加,以保持对晶体管通道的压应力(目前在20nm节点上为55%的Ge含量)。另一种技术是将SiGe晶体的尖锐边缘靠近通道,以引发更多应力。这在32nm节点上已经实施。

替代栅极还提供了另一种增加PMOS应变的方法。当多晶硅栅极电极被去除时,腔隙层和相关结构向内移动,压缩晶体管通道并引发压应力。

使用替代源/漏区方法给NMOS晶体管施加应变是相当棘手的,因为很难找到一个比硅具有更小晶格常数同时又具有高度稳定性的材料。因此,通常会采用其他技术来实现NMOS的拉应变,而不是替代源/漏区。然而,最近已经完善了一种技术,将磷或碳和磷掺入到硅外延中。由于碳比硅小38%,用这种外延替换源/漏区会在通道两侧产生拉应变,并在通道上形成拉应力。这正是增强晶体管性能所需的(驱动电流增加高达20%)。为了达到这个目的,可以使用磷或碳/磷外延。

NMOS器件上应力记忆技术(SMT)的一个更具体的名称是“边缘位错应力”。这是一种通过SMT技术在NMOS通道中产生边缘位错并引发剧烈拉应力的技术。在P或P&C替代源/漏外延技术出现之前,这项技术首先应用于45/32纳米节点的NMOS晶体管。该过程涉及进行深度非晶化注入,然后沉积一层氮化物应力覆盖层。在进行快速热退火以诱导SMT后,应力覆盖层被去除,形成了边缘位错。SMT的初始预非晶化注入(PAI)在源/漏区域下形成多个边缘位错,增强了短通道迁移率。整体上,可实现10%的Idsat增加。需要注意的是,通常会同时使用不同的应变技术,因为它们对性能增强的贡献是累加的。

37.Source /Drain Anneal

然后,晶圆将经历快速热处理(约950摄氏度处理约持续1秒,随后进行约1,350摄氏度的闪光退火处理持续1-3毫秒),以激活PMOS和NMOS的掺杂原子。

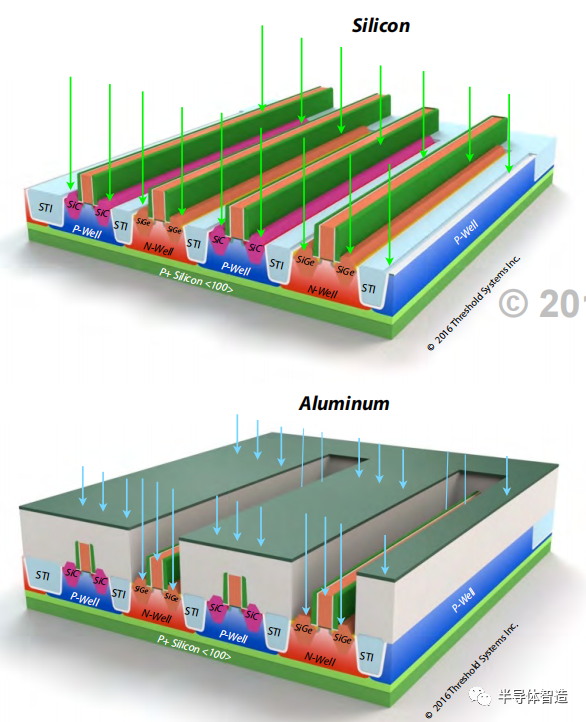

38.Nickel Salicidation Oxide Strip

退火后,晶圆上的栅极顶部仍然有一层氧化物。在SiGe和SiC源/漏区域上可能还存在着天然氧化物。这两种氧化物必须被去除,以便为硅化处理暴露出裸露的硅表面。

然后,晶圆被浸泡在HF中,去除栅极顶部以及源/漏区域表面的所有二氧化硅。这个步骤准备晶圆进行接下来的硅化处理。

39.Salicidation Implants

晶圆接受了硅预非晶化注入(PAI)。这使得硅表面非晶化,并有助于形成更加均匀、电阻较低的硅化物(在接下来的操作中形成)

晶圆使用光刻胶进行图案定义,仅暴露出P井。然后,使用铝进行注入(。铝的位置安排使其位于SiGe与尚未沉积的Ni/Pt之间的界面上。这种注入能够降低PMOS器件的接触电阻,因为铝会分离到SiGe的顶部,并且由于是P型掺杂,它会将电子空穴的肖特基势垒高度从约0.4电子伏降低到约0.12电子伏,同时提高驱动电流达19%。

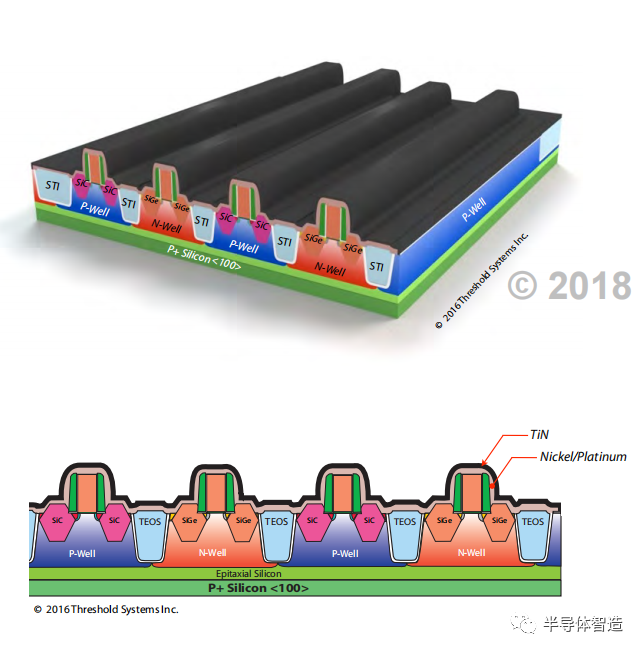

40.Nickel/Platinum/TiN Deposition

晶圆经过P/SC1清洗后,采用物理气相沉积法在上面均匀涂覆约125 Å的镍/铂和约150 Å的钛氮化物。镍上覆盖的钛氮化物帽层有助于防止在高温硅化过程中镍的扩散,并促进更均匀的NiSi形成。5-10%的铂有助于降低Ni-Si界面的势垒并建立更低的接触电阻。它还延迟了低电阻NiSi向较高电阻NiSi2的转变。

2D图像展示了在初始沉积之后及在退火之前的镍/铂/钛氮化物层堆叠。

41.Salicidation Anneal

晶圆经历了大约250℃、30秒的快速热退火(RTA),将镍铂转变为高电阻的C49相。接着,进行了第二次约390℃、30秒的RTA,将晶圆表面的镍转变为低电阻(15 µΩ-cm)的C54 NiSi相。

采用NiSi是因为它比相同厚度的CoSi2消耗至少30%的硅。这一点非常重要,因为20纳米节点结深度非常浅。此外,NiSi具有非常光滑的表面,可以最小化结漏电。

2D图像展示了器件上反应和未反应的镍/铂。为了形成镍硅化物,镍/铂层必须与裸露的硅表面接触。唯一有裸露硅的位置是在栅极的顶部或源/漏区域。位于STI(shallow trench isolation,浅沟槽隔离)和氮化物间隔层上的镍/铂将保持未反应状态。

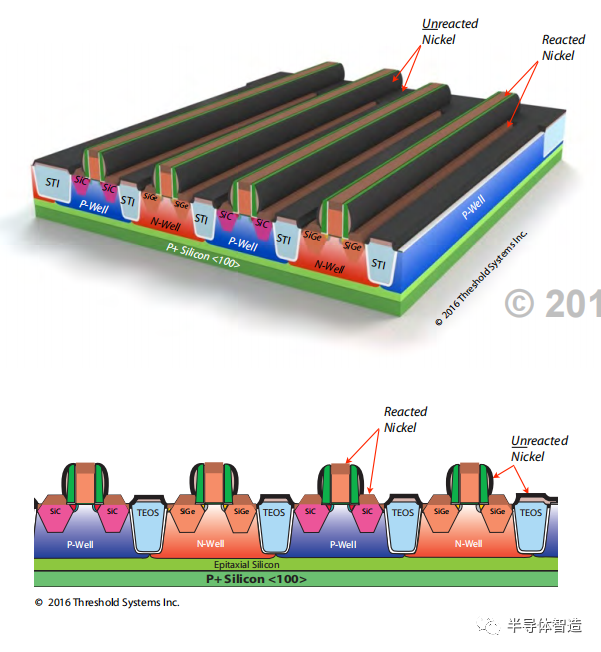

42.Unreacted Nickel Strip

位于间隔层侧壁和STI上的未反应镍会被SC1溶液刻蚀掉。这种刻蚀具有高选择性,只保留在栅极顶部和源/漏区域上的已反应硅化物。这种刻蚀还会从晶片的所有表面上去除钛氮化物覆盖层。

2D图像阐明了蚀刻溶剂能够迅速攻击并去除氮化物间隔层侧壁和STI顶部上的未反应镍/铂。然而,蚀刻溶剂不会攻击源/漏区域上的已反应镍硅化物,也不会攻击栅极顶部的已反应镍硅化物。

Transistor Nomenclature

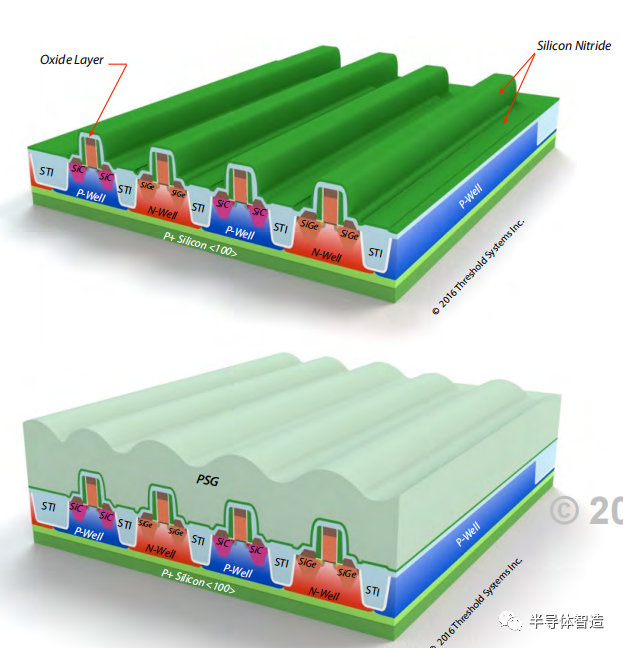

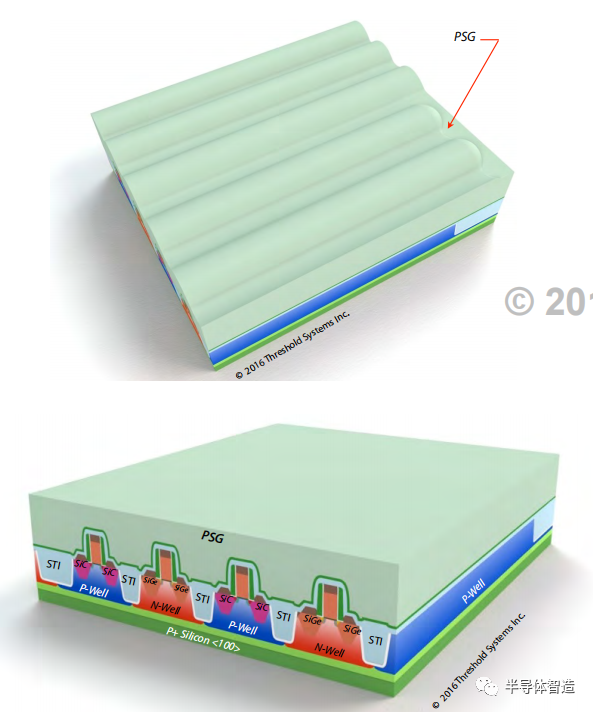

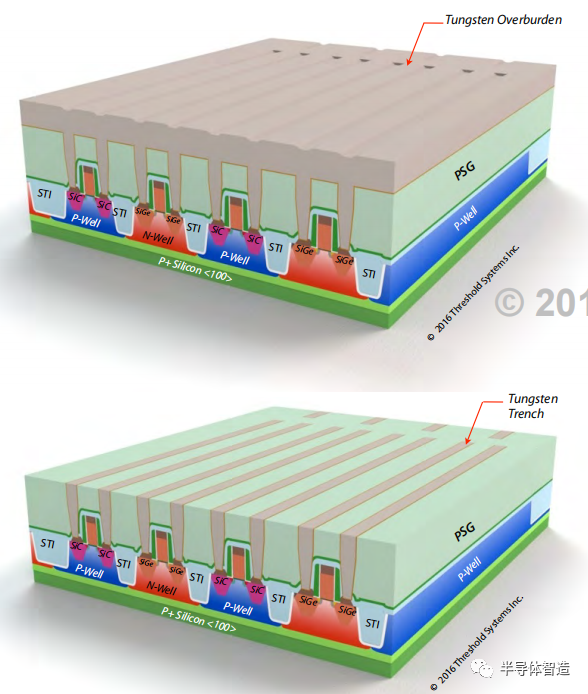

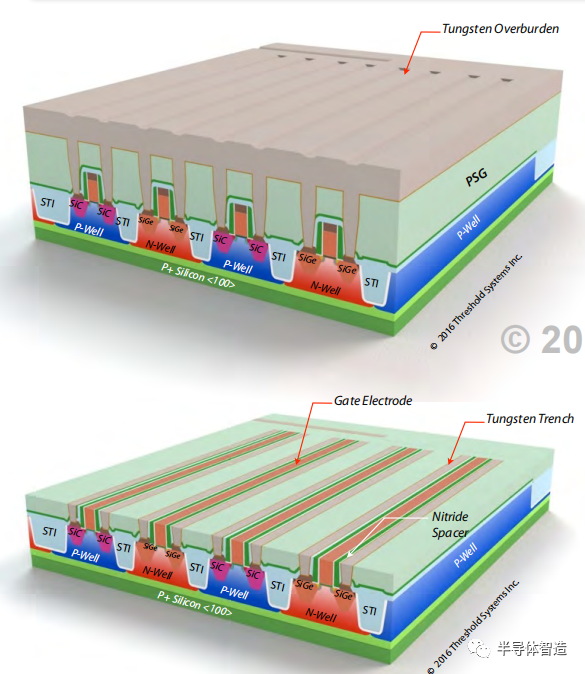

43.Pre-Metal Dielectric (PMD)

晶圆首先在P/SC1(一种清洗溶液)中进行清洗,然后沉积薄约75Å的二氧化硅层,接着沉积约75Å的氮化物层。氧化物作为扩散屏障,防止外部杂质掺入器件层(即“活性”层)。

硅氮化物将作为蚀刻停止层,用于连接晶体管的源/漏区和栅极电极到尚未形成的钨沟槽中的接触刻蚀。

接下来,使用高密度化学气相沉积(CVD)技术,在晶圆上沉积2,000 Å的磷掺杂玻璃,也称为PSG(磷硅酸盐玻璃)。这一层形成了前金属介电层(Pre-Metal-Dielectric,PMD)。

44.Pre-Metal Dielectric Polish-Back

在抛光之前,观察 PSG 层的自上而下视图。请注意 PSG 中的凸起,这是由于栅极电极高度引起的底层地形。

使用CMP(化学机械抛光)将晶圆抛光至约1,200Å的厚度。

45.Hard Mask Patterning

接下来,晶圆涂覆光刻胶并进行图案化处理。下面插图是沟槽接触光刻胶图案的自上而下视图。请注意图像右侧的栅极电极接触沟槽。

这将是一个双重图案化操作过程。

46.Hard Mask Etch & Photoresist Strip

光刻胶被氧化灰化以去除,留下图案化的非晶碳硬膜。然后,晶圆在蚀刻溶液中进行清洗,以去除任何残留的光刻胶

利用非晶碳硬膜作为模板,进行高度各向异性刻蚀,穿过PSG层形成接触孔。刻蚀在源/漏区域上方的硅氮化物和栅极顶部停止。然后改变刻蚀化学组分,对硅氮化物和底层氧化物进行蚀刻。刻蚀在源/漏区域上方的镍硅化物和栅极顶部停止。

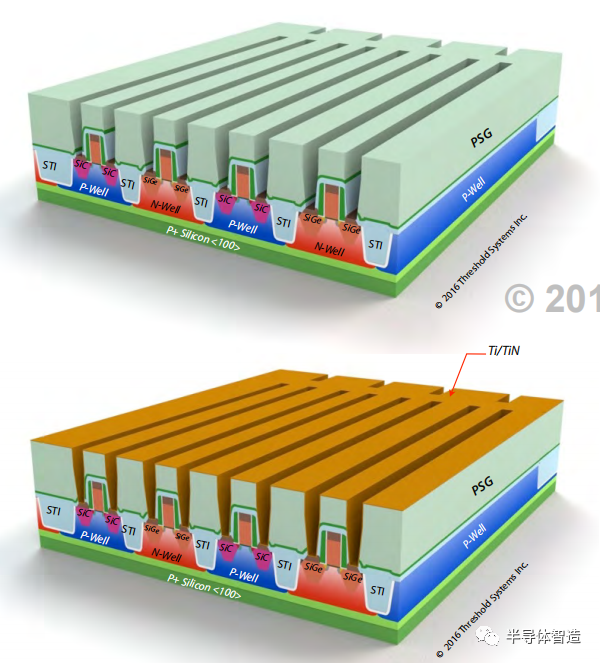

47.Hard Mask Strip & TiN Deposition

接下来,通过离子金属等离子体物理气相沉积(IMP PVD)沉积约60Å的钛(一层胶黏层)。随后通过IMP PVD沉积约30Å的钛氮化物(一层屏蔽层)。在沉积后,钛氮化物进行重新溅射,以增强接触孔内的侧壁覆盖。

晶圆随后在RTA中加热,使钛/钛氮化物发生反应并设置胶黏层的电阻。

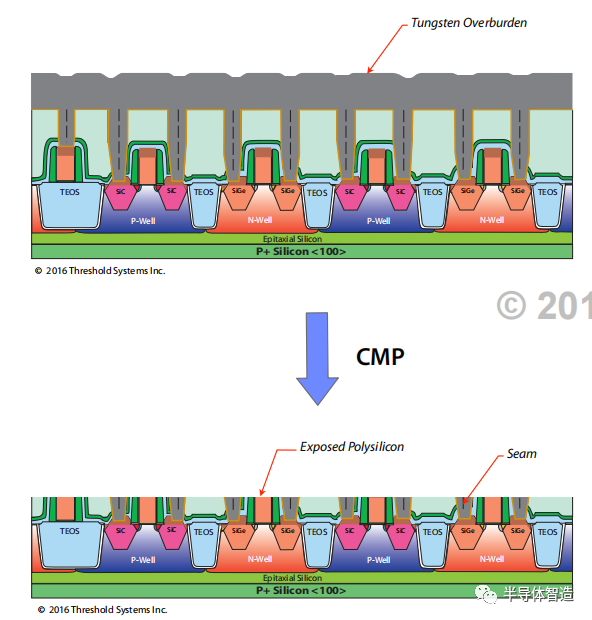

48.Tungsten Deposition & Polish-Back

接下来,沉积一层钨种子层,衬里接触孔的内壁,并确保对整个钨沉积层进行均匀覆盖。

最后,通过化学气相沉积(CVD)沉积约2,500Å的钨。

晶圆再次通过CMP工艺进行抛光。在这个过程中,去除多余的钨层,并将钨沟槽抛光至PSG层的顶部。

接下来,进行氧化缓冲处理,以使PSG氧化物表面光滑,并确保PSG表面与钨沟槽顶部共面。

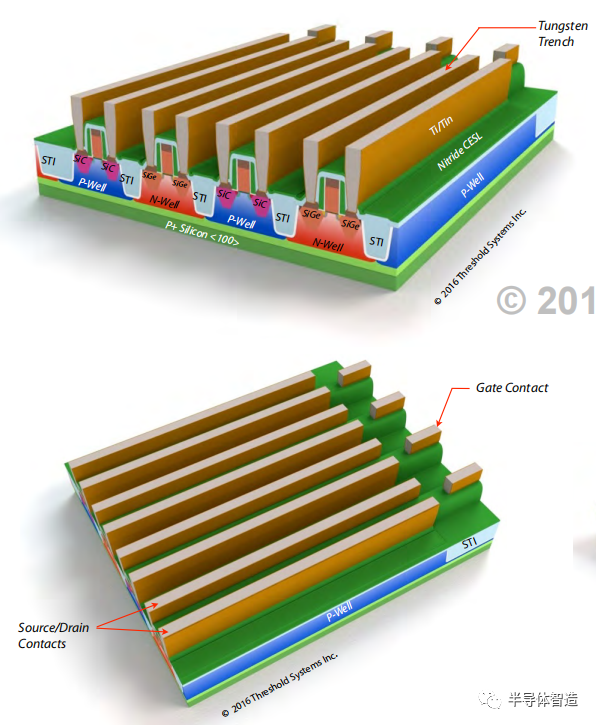

49.Trench Contacts (Alternate Scheme)

图示展示了如果去除PSG氧化物,钨沟槽将会呈现的样子。清晰可见的是钨沟槽,上覆有Ti/TiN,与源漏区域和栅极电极进行电接触。

当然,这些视图在实际生产设备中是不可见的。

Plug Polish Back/Tungsten Trenches

将钨填充物抛光至与栅极顶部共面的操作是一项新的技术,首次在32纳米工艺节点引入。较短的钨填充物具有较低的接触电阻。这一特性与NMOS和PMOS晶体管的抬高源漏区域结合,确保接触电阻保持在可接受的范围内。

完全消除钨填充物并采用铜填充物是困难的,因为将铜带入源漏区域会带来极高的风险。

50.Plug Polish Back

抛光回退的填充物最初的形成方式与标准填充物相同。在沉积Ti/TiN屏障金属后,再沉积一层钨种子层,然后进行2,500Å的钨的CVD沉积。

随后,将过剩的钨层抛光回退,直到填充物变得非常短,与栅极顶部共面。

51.Polished Back Trench Contacts

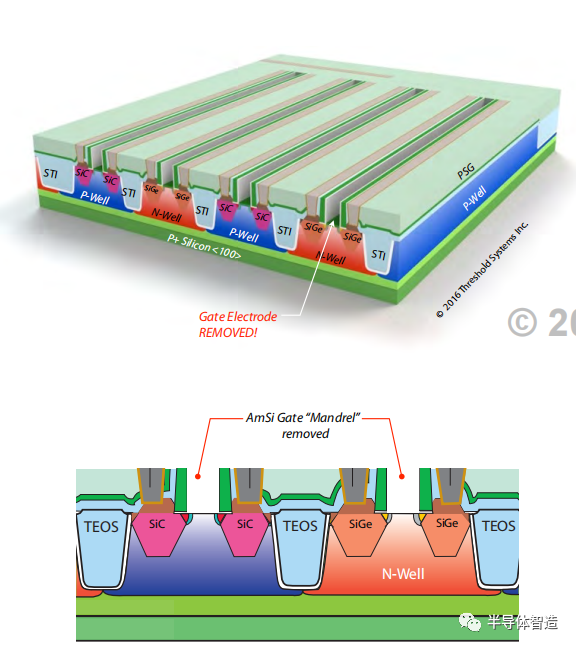

52.Gate Electrode Removal

栅极电极的去除:

一旦栅极顶部被打开,掺杂的非晶硅栅骨架将被刻蚀去除。因此,栅极电极被称为"牺牲电极"。它的唯一目的是作为一个占位符,通常被称为"骨架"。

这次刻蚀还会去除在栅腔壁上生长的氧化物偏移间隔层,以及栅腔底部的氧化物刻蚀停止层。

栅极骨架的去除:

下图显示了在CMP抛光打开栅极顶部和刻蚀掉牺牲性非晶硅栅骨架后的CMOS结构的横截面图。

这次刻蚀还会去除在栅腔壁上生长的氧化物偏移间隔层,以及栅腔底部的氧化物刻蚀停止层。

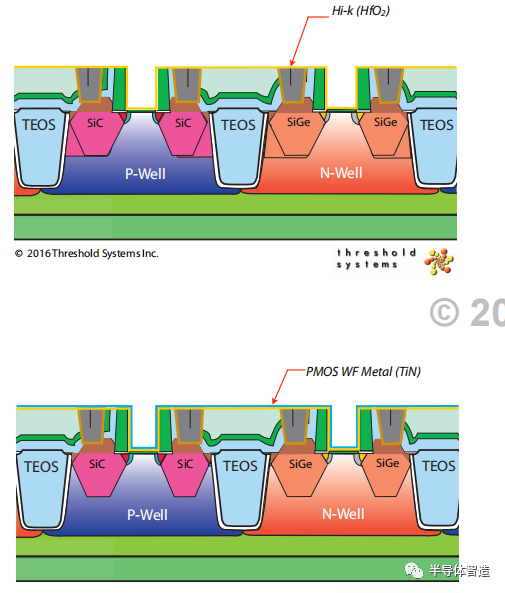

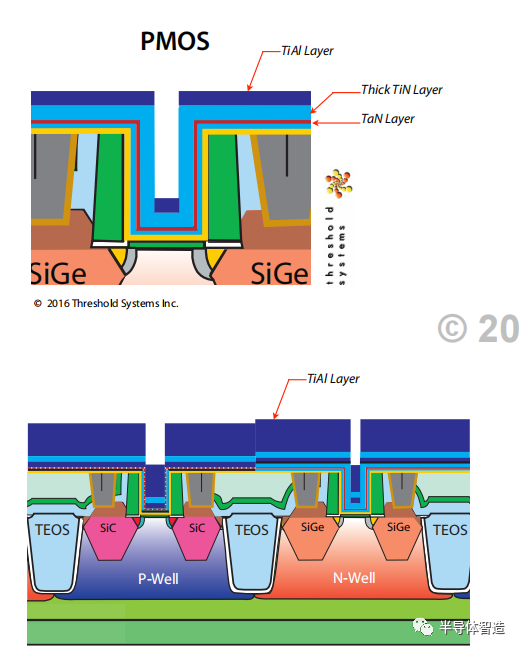

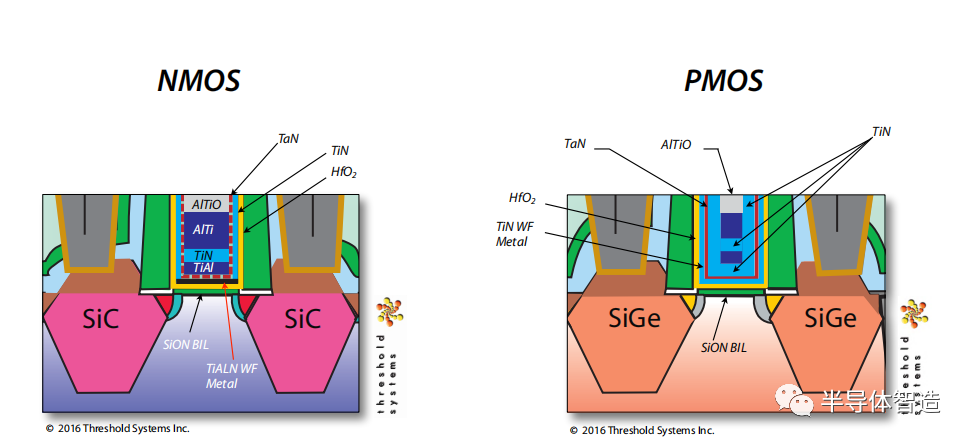

53.Hi-K Dielectric & PMOS WF Metal Deposition

高介电常数材料的沉积:

接下来,使用原子层沉积(ALD)技术沉积一层约18埃厚的氧化铪(HfO2)薄膜。

PMOS WF金属沉积:

接下来,使用物理气相沉积(PVD)技术沉积薄的PMOS金属栅电极。

它由薄的2.0纳米钛氮化物(TiN)层通过PVD沉积而成。这是PMOS工作函数(WF)金属。它是一层填充PMOS和NMOS腔隙并包覆在晶圆表面的钛氮化物。

在沉积后,再次进行喷溅,以确保栅腔内侧壁获得良好的覆盖。

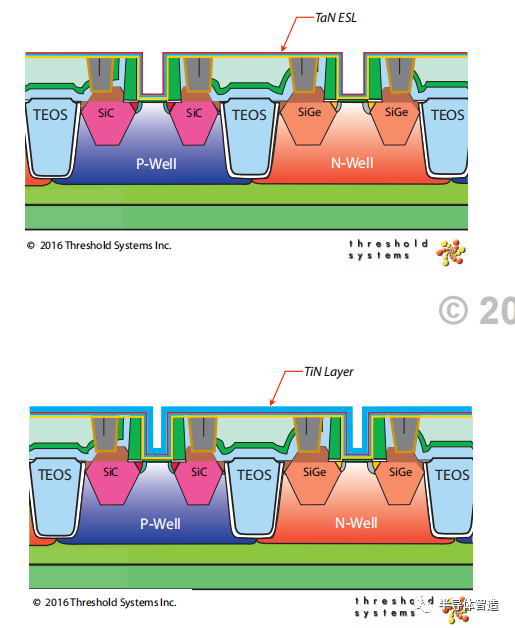

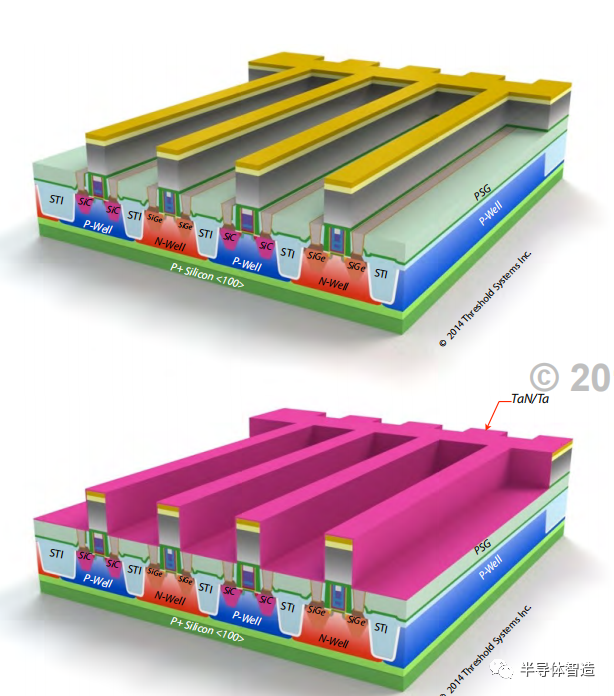

54.TaN & TiN Metal Deposition

TaN刻蚀停止层的沉积:

使用物理气相沉积(PVD)技术沉积约1.0纳米厚的TaN层。这层将作为刻蚀停止层(ESL)使用。

TiN层的沉积:

使用物理气相沉积(PVD)技术沉积约5.0纳米厚的TiN层。这是栅极堆栈中的第一层补充金属,为栅极堆栈底部提供应变和电接触。

对TiN进行再溅射以确保栅腔内侧壁得到良好的覆盖。

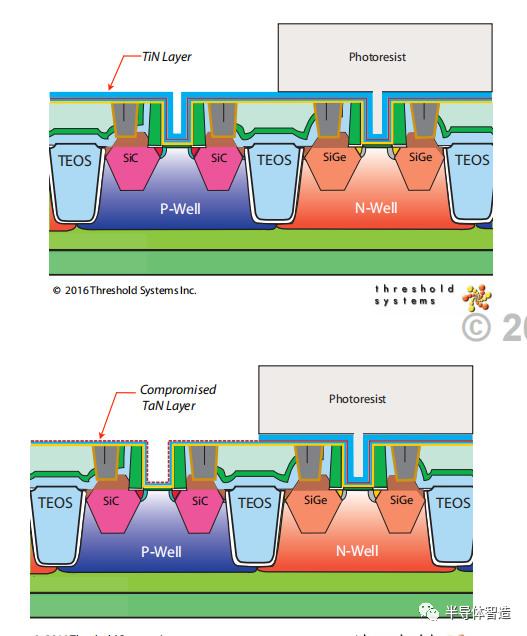

55.PMOS Metal Patterning & Etch

TiN层的光刻胶图案形成:

先进行光刻胶的涂布和图案形成。它仅保护PMOS区域,并暴露出NMOS区域上的TiN层。

TiN层的刻蚀:

暴露的TiN层被刻蚀去除。TaN层作为刻蚀停止层,阻止了该刻蚀过程。如上所示,非常薄的(<10Å)TaN层的完整性会受到刻蚀过程的损害。

TaN层的完整性被损害是有益的,因为在后续的过程中,在NMOS晶体管的底层TiN层中扩散铝,以形成NMOS TiAlN工作函数金属。

56.Photoresist Strip & TiAl Deposition

去除光刻胶并清洁晶圆。

TiAl层的沉积:

使用物理气相沉积(PVD)技术沉积4.8纳米薄的钛铝层。PVD过程被调整为仅在水平表面沉积(这很容易实现,因为必须对PVD过程进行微调才能在垂直表面沉积)。

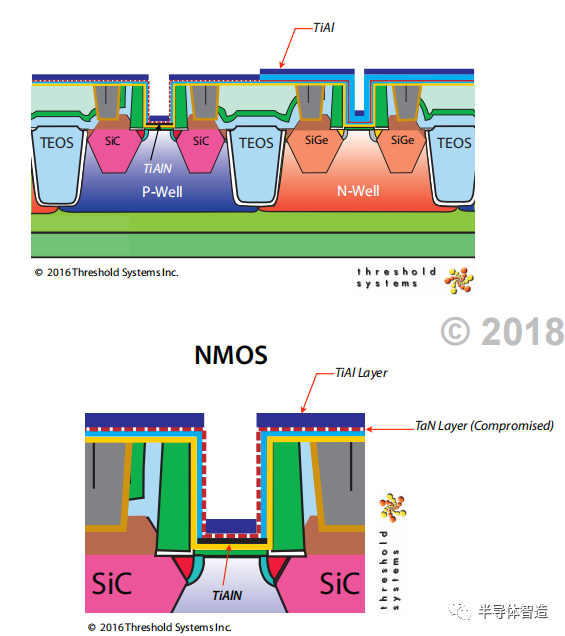

57.TiAl Anneal & NMOS WF Metal Formation

退火处理:

随后进行退火处理,使得仅在NMOS区域中的TiAl中的铝元素通过TaN屏障进行扩散。这将在Hi-k介质上形成位于顶部的TiAlN NMOS工作函数金属。

退火处理:

引发TiAlN工作函数金属形成的退火处理在400ºC以下的温度下进行。在这个温度下,铝的扩散性很强,并且由于在NMOS器件中将其与底层TiN隔离的TaN之前受到损害(它被用作蚀刻停止层),铝自由地扩散到TiN并形成所需的TiAlN,即NMOS工作函数金属。

58.TiAl Backfifill Deposition

退火处理:

在形成NMOS工作函数金属的退火处理过程中,厚的覆盖层TiN层(在NMOS晶体管中不存在)和未经损害的TaN层阻止铝元素扩散到TiN PMOS工作函数金属中。因此,TiN PMOS工作函数金属不会变成TiAlN,而是保持为所需的TiN。

AlTi层的沉积:

通过物理气相沉积(PVD)沉积两层较厚的铝钛层(11.0纳米+7.0纳米)。PVD过程被调整为只在水平表面上进行沉积。

这种金属层作为从栅极顶部到底部的电接触。

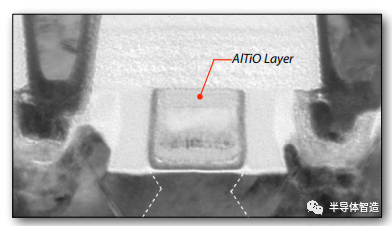

59.Metal Polish-Back

CMP抛光:

通过化学机械抛光(CMP),对金属层进行抛光,使其与晶体管栅极的顶部平齐。

在CMP过程中,AlTi的最上层被氧化形成AlTiO。

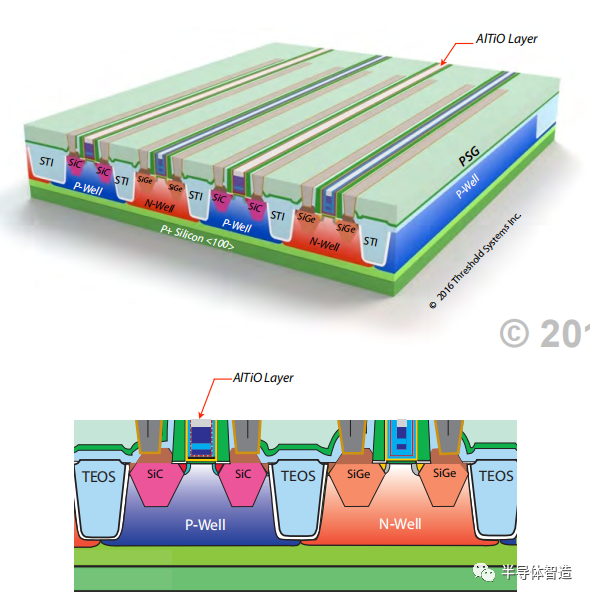

Replacement Gate Anatomy

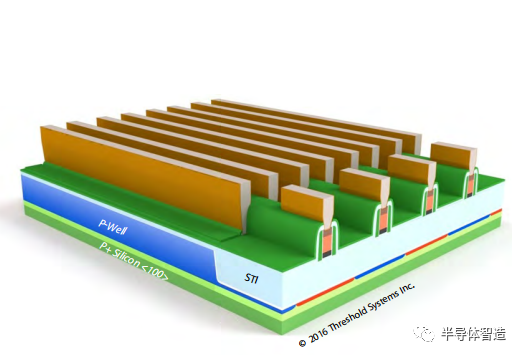

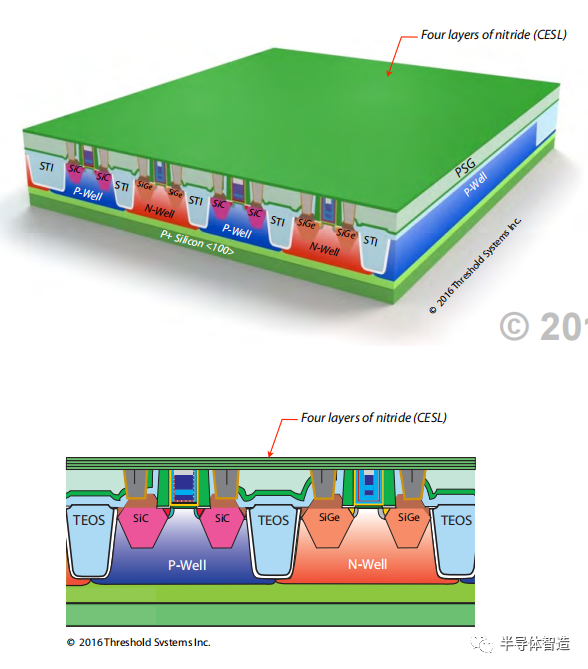

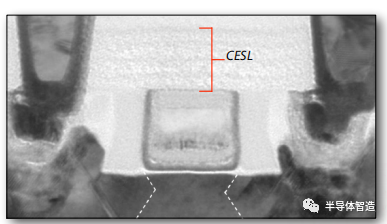

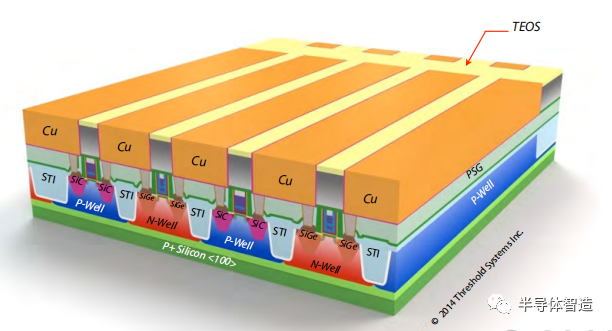

60.Nitride CESL Deposition

接触刻蚀停止层(CESL):

接下来,在晶圆表面沉积几层硅氮化物。这将密封晶体管的顶部,并作为接下来制造的接触沟槽的刻蚀停止层。

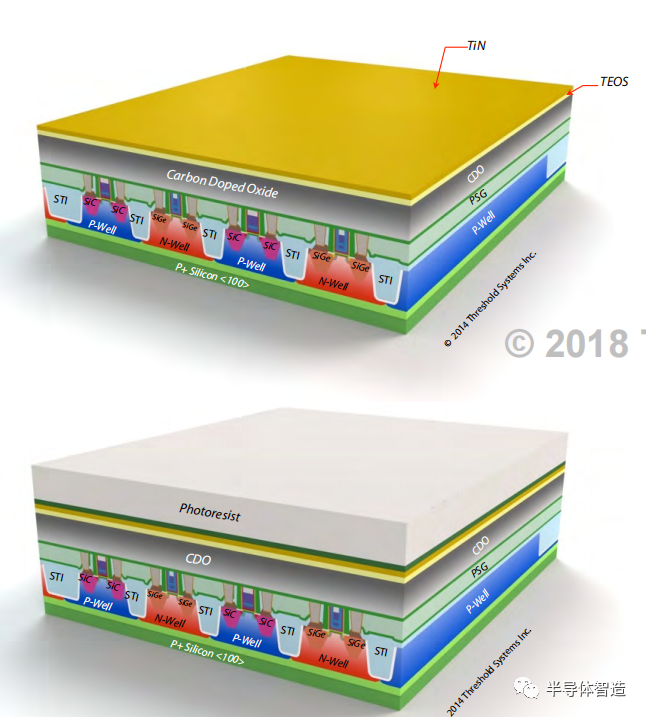

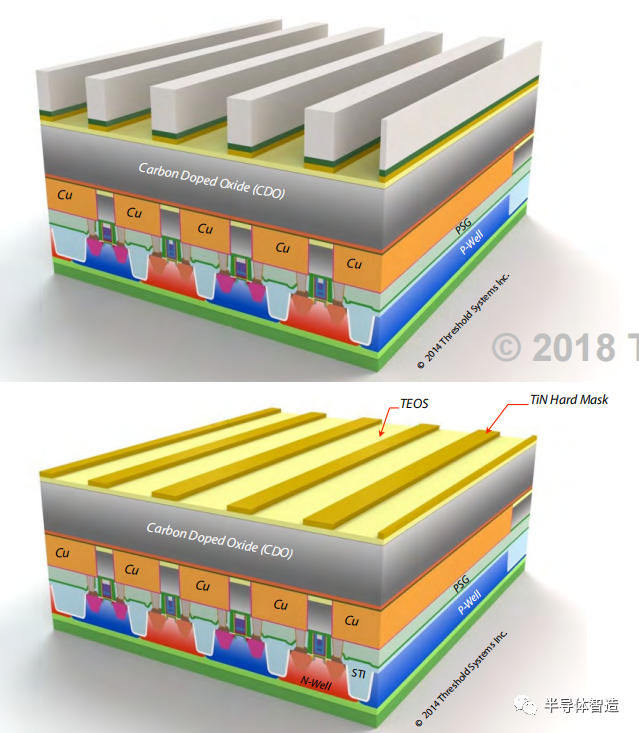

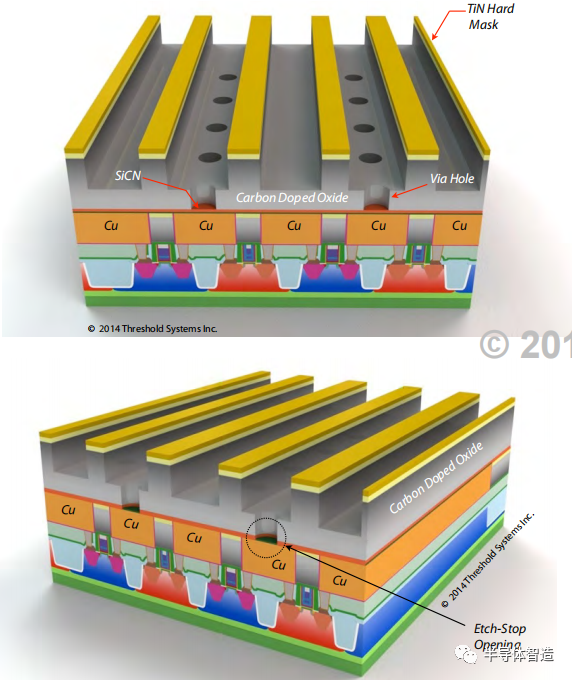

61.CDO/TEOS/ TiN Deposition

第一层互连电介质(ILD)被沉积。它由约1,000Å的掺碳氧化物(CDO)层组成,在沉积后进行紫外固化以去除多孔剂并降低其介电常数。

接着沉积一个400Å的TEOS CMP停止层,然后是一个300Å的钛氮(TiN)硬面模,接下来进行曝光显影。

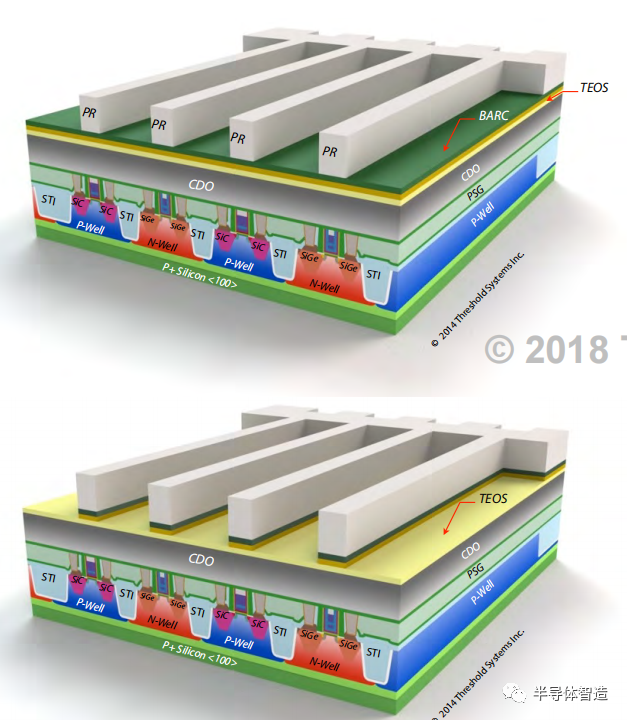

62.TiN Hard Mask Patterning & Etch

然后对TiN硬掩模部分进行刻蚀。刻蚀停止在TEOS层上。

63.Photoresist Strip & Metal-1 Trench Etch

利用TiN作为模板,进行高度各向异性刻蚀,穿过TEOS和CDO层,定义金属1(Metal-1)的沟槽。刻蚀停止在硅氮(SiN)蚀刻阻挡层上。

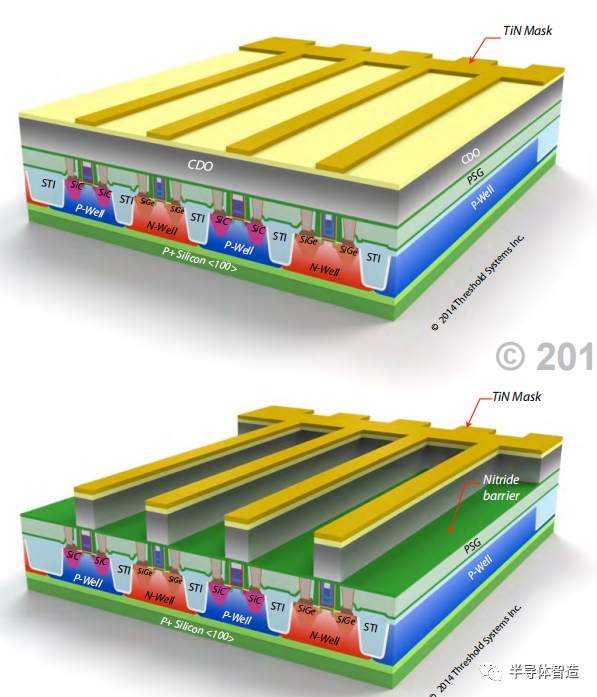

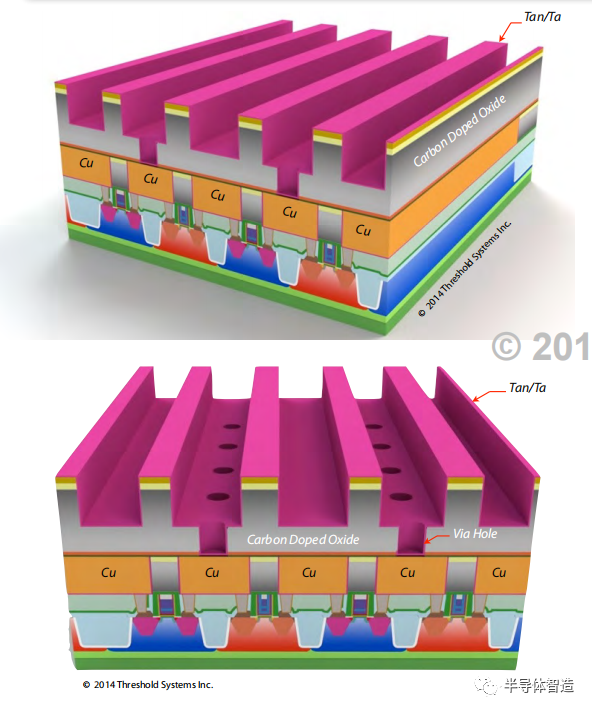

64.Nitride Barrier Opening TaN/Ta Deposition

然后继续刻蚀打开沟槽底部的SiN刻蚀阻挡层。接下来,采用IMP PVD工艺沉积80 Å的钽氮(TaN)层,然后是30 Å的钽(Ta)层。这两种金属作为屏障,将尚未沉积的铜限制在沟槽内。在钽和钽氮操作之后,进行重新溅射步骤,以确保良好的侧壁覆盖。

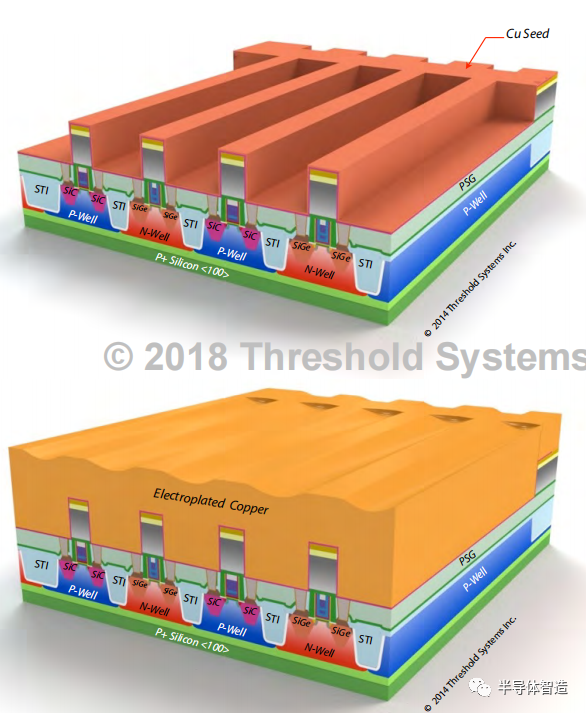

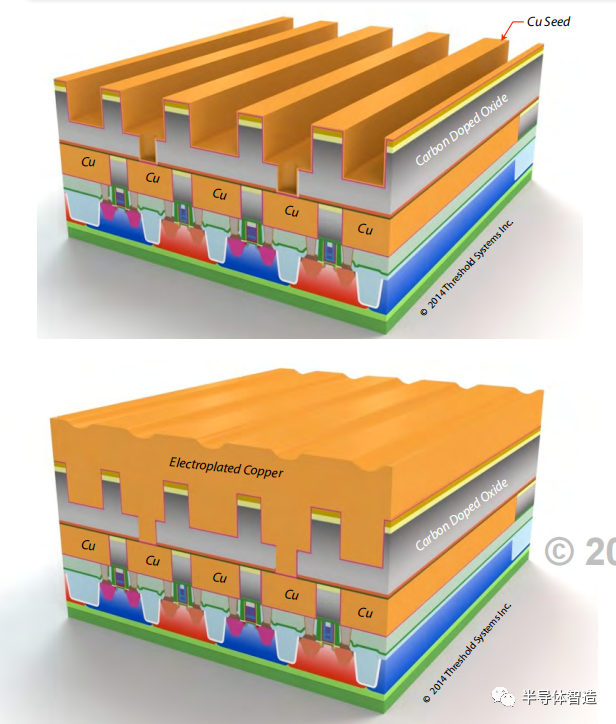

65.Copper Seed & Copper Bulk Deposition

在不破坏真空状态下,沉积了300Å的铜种子层,覆盖了晶圆的整个表面,包括沟槽的内部。

铜种子层的存在是为了确保均匀、无空洞的大面积铜沉积,并且是电镀过程的必要前提条件。

接下来,采用电化学沉积方法,在其上沉积了6,000 Å的大量铜。

在沉积完成后,使用形成气体(forming gas)将铜退火,在300ºC的温度下保持90秒,以定型其晶粒结构并降低其电阻。

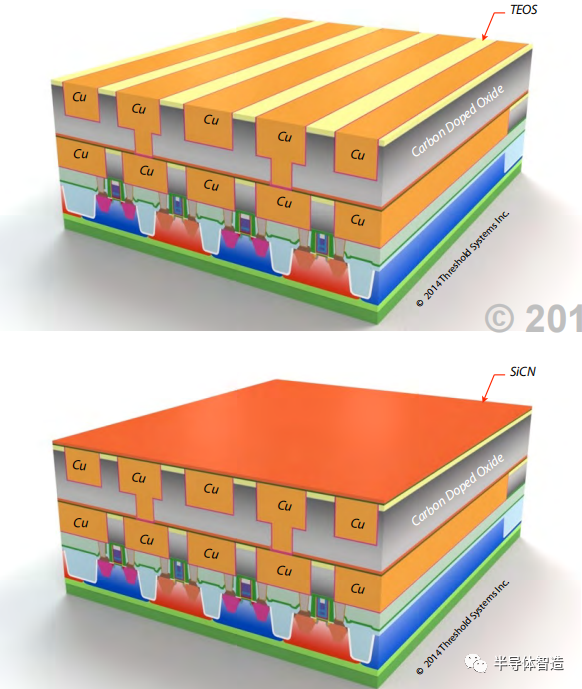

66.Copper-Ta/TaN-TEOS CMP

使用CMP(化学机械抛光)将铜抛光回去。这个抛光过程也会去除TEOS表面上的钽。较软的TEOS作为CMP过程的抛光停止层。

接下来,进行氧化物抛光操作,以平滑TEOS氧化物的表面,并确保TEOS表面与铜线顶部在同一平面上。

在每次CMP操作之后,对晶圆进行清洁处理。

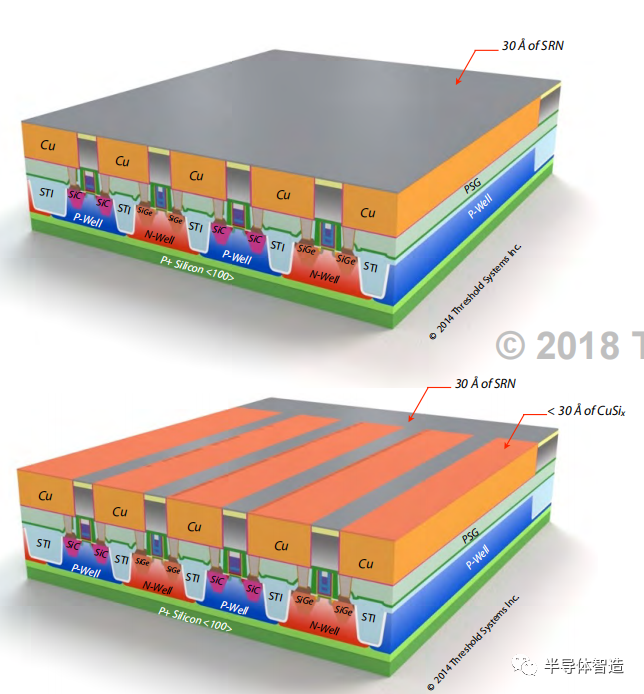

67.Copper Sealing

在晶圆上沉积了一个薄的30Å的富硅氮化物(SRN)层。富硅氮化物(SRN)层与铜金属反应,形成了铜硅化物(CuSix)。

68.Copper Sealing & Barrier Deposition

然后,对CuSix进行氮化处理,将其转化为SiN膜,沉积了一个300Å的SiCN刻蚀停止层,以密封第一层金属的顶部。现在,第一层金属中的铜被Ta/TaN包围在五个侧面,并由SiCN封顶。

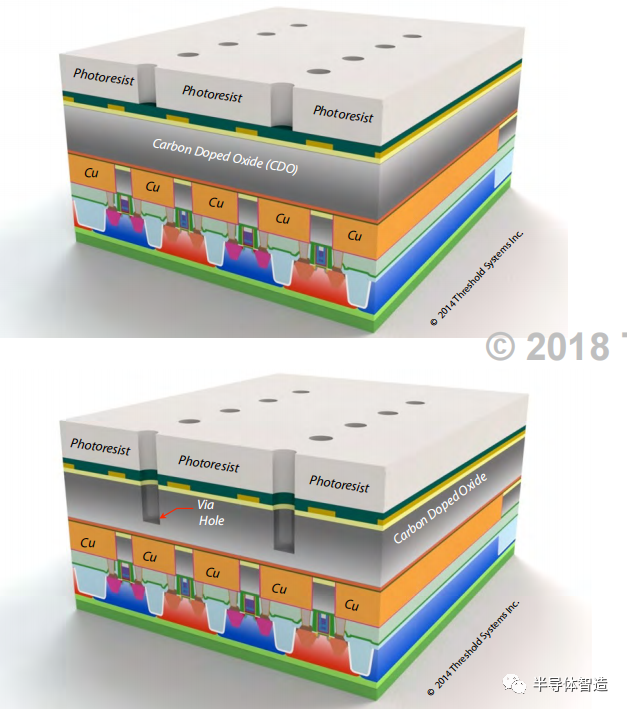

69.ILD-2 Deposition

接下来,沉积了7,000 Å的低介电常数SiCOH,并进行紫外烘烤以去除孔原和降低介电材料的介电常数。然后,沉积了400 Å的TEOS(抛光停止层),接着是300Å的TiN硬掩膜和300Å的BARC层以及一层光刻胶。然后对光刻胶进行图案化处理。

70.TiN Hard Mask Etch & PR Strip

71.Via Photo & Via Partial Etch

通过高度各向异性刻蚀工艺,对通孔进行部分刻蚀。但未完全刻蚀至SiCN刻蚀停止层。

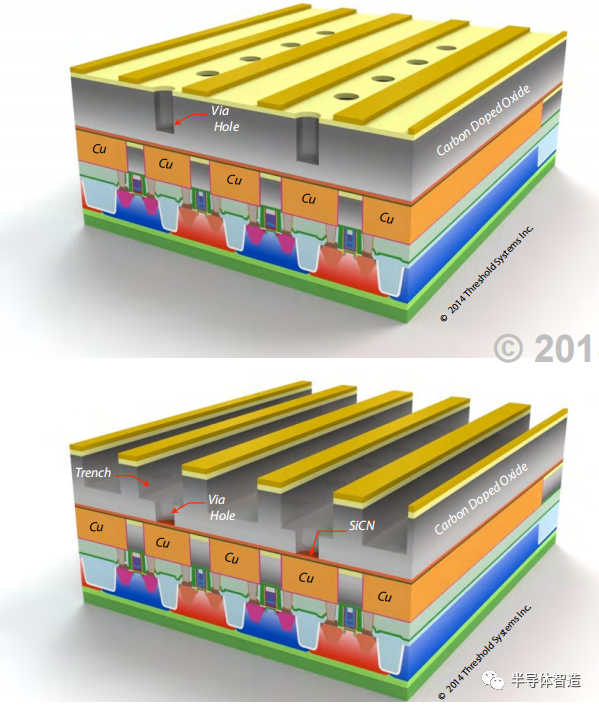

72.Photoresist Strip & Trench Etch

73.SiCN Barrier Opening

Dual Damascene结构的正视图显示了沟槽和众多的通孔。请注意,通孔底部的SiCN屏障尚未穿孔。使用刻蚀工艺,打开通孔底部的SiCN屏蔽层,并暴露出底部的铜线。这是一个非常关键的步骤。如果刻蚀过于激烈,铜将喷射到未受保护的Dual Damascene结构中。如果刻蚀过轻,SiCN屏障将无法完全去除,导致通孔电阻增加。

74.TaN/Ta Barrier

接下来,使用IMP PVD方法沉积大约80 Å的TaN层,然后沉积大约30 Å的Ta层。这两种金属作为屏障,将尚未沉积的铜限制在沟槽中。在TaN和Ta操作之后进行再溅射处理。

Dual Damascene结构的正视图显示了覆盖着TaN/Ta的沟槽和众多的通孔。

与接触孔类似,通孔非常微小且难以填充屏障金属。然而,对于通孔来说,这个问题尤为重要,因为它们必须持续衬覆TaN/Ta,以便将稍后填充的铜封装其中。任何TaN/Ta屏障金属中的不连续性都会导致铜原子泄漏出通孔,造成晶体管污染。

专用的TaN/TaN离子化PVD工具结合溅射操作,确保实现适当的屏障覆盖。

75.Cu Seed Deposition & Electroplated Copper

在晶圆上沉积约300Å的铜种子层,覆盖沟槽的内部。

铜种子层的作用是确保完全贴合且无空隙的铜块沉积(后续操作),同时也是电镀过程的必要前提条件。接下来,使用电化学沉积法沉积大约6,000 Å的铜块。

沉积完成后,将铜在300℃的成形气体中退火90秒,以确定晶粒尺寸。

76.Copper CMP Polish & Final Seal

使用CMP技术对铜进行抛光,在沉积相同的SRN层后,将其转化为CuSi,然后转化为SiN,接着在第二层金属的顶部沉积一个300Å的SiCN层来封闭。第二层金属(及其通孔)现在被TaN/Ta围绕在五个侧面,并在顶部被SiCN封装。

需要注意的是,在这种Dual Damascene中,光刻胶从未接触过低介电常数介质。类似地定义了另外七个层的金属沟槽和通孔。

-

半导体

+关注

关注

339文章

31236浏览量

266500 -

晶片

+关注

关注

1文章

413浏览量

33002 -

22nm

+关注

关注

0文章

51浏览量

18593 -

工艺流程

+关注

关注

7文章

118浏览量

16874 -

FinFET

+关注

关注

12文章

262浏览量

92363

原文标题:22nm Planar Process Flow介绍

文章出处:【微信号:光刻人的世界,微信公众号:光刻人的世界】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

透视IVB核芯 22nm工艺3D技术终极揭秘

22nm技术节点的FinFET制造工艺流程

锐成芯微宣布在22nm工艺上推出双模蓝牙射频IP

Intel 22nm光刻工艺背后的故事

台积电又跳过22nm工艺 改而直上20nm

Arasan宣布用于台积公司22nm工艺技术的eMMC PHY IP立即可用

北斗22nm芯片用途是什么?

22nm和28nm芯片性能差异

22nm芯片是什么年代的技术?

Trench工艺和平面工艺MOSFET的区别在哪呢?

Trench工艺和平面工艺MOS的区别

22nm平面工艺流程介绍

22nm平面工艺流程介绍

评论