前言:

最近加的群里面有些萌新在进行讨论FIFO的深度的时候,觉得 FIFO的深度计算比较难以理解 。所以特出漫谈FIFO系列,会涉及到FIFO的深度计算、同步/异步FIFO的设计等。

引言:

考虑如下的场景,是我们小学或者初中的时候学过的一个问题:

场景一:

如上图所示,假设入水口的 进水量 2m³/h ,出水口的 出水量1m³/h ,假设水池容量10m³,开始的时候水池没有水,水池多久会满?

答:水池容量 / (进水量 - 出水量) = 10 /(2 - 1) = 10 h

上面我们可以得出,对于进水量比出水量多的情况下,无论水池容量大小是多少, 水池在一些时间之后会溢出 。

所以这也反映了,我们在IC设计中,对于 FIFO这个蓄水池 ,输入数据的个数一直大于输出数据的个数, FIFO总会溢出产生问题 。

场景二:

如上图所示,假设入水口的 进水量 2m³/h ,出水口的 出水量1m³/h ,但是本场景和场景二不同的地方是:入水口的进水时间是一天24h中的任意8小时进水。出水口是半天12h中的任意2小时出水。

问水池会溢出吗?可以设计水池的深度让水池不要溢出吗?

(1)对于一天的进水量来说,2 *8 = 16m³ ,对于一天的出水量来说,2 *2 = 4m³ , 进水量 - 出水量 = 12 m³,所以水池会溢出。

(2)因为 输入数据的个数一直大于输出数据的个数 (在当前的时间)。所以无论设计多深的深度,水池都会溢出。

场景三 :

如上图所示,假设入水口的时钟是按照 分钟来进行间隔 ,对于入水口,每10分钟流入8m³的水,对于出水口来说,每1.2分钟流出1m³的水。

问水池会溢出吗?可以设计水池的深度让水池不要溢出吗?

(1)对于入水口来说,10分钟8立方米 所以12分钟9.6m³,对于出水口12分钟10m³。所以通过 设定水池的深度可以让水池不会溢出 。因为总体而言流出的水流是大于流入的水流。

概念1:back to back

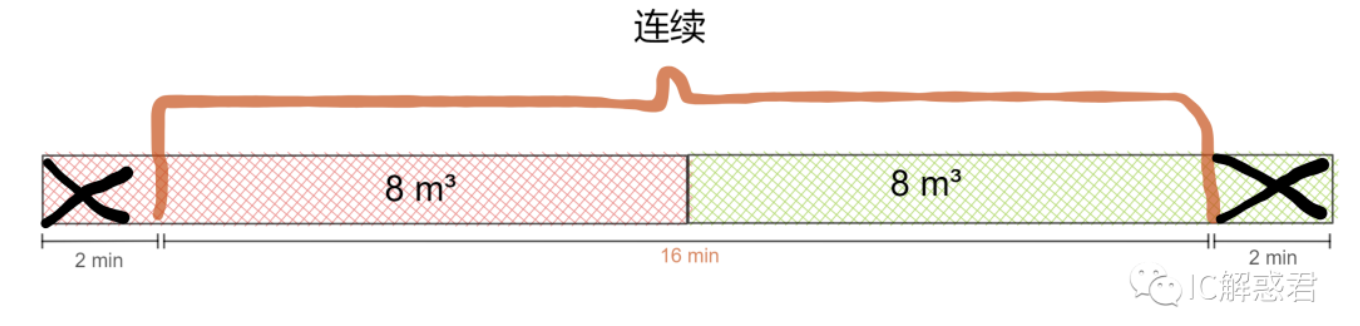

对于入水口来说有一种情况是需要注意的。这种情况如下图:

在一次 完整的20分钟之内 ,前面两分钟没有进水,最后的两分钟没有进水,进水的时间集中在20分钟内的 连续16分钟内 ,所以这段时间对于水池来说压力最大,因为水池设计的深度如果不考虑这个可能就会溢出,(这也就是所谓的流(水)量密集)

(2)考虑到概念1再回答场景三的第二个问题:水池的深度应该设计为:

**[1] **16m³ / 16 min = 进水量的效率

[2] 1m³ / 1.2min = 出水量的效率

**[3] ** 水池的深度 = (进水量效率 - 出水量效率) * **16 min ** = (16 /6 )m³

在计算水池深度我们可以得出 结论 :

所谓水池的深度在计算的时候,就是进水量在背靠背这段时间内,进水的所有量,减去背靠背这段时间内出水口的出水量,在这背靠背的时间内,入水的量减去出水的量,就是内部的水池应该承受的水量。

正文:

FIFO计算问题:

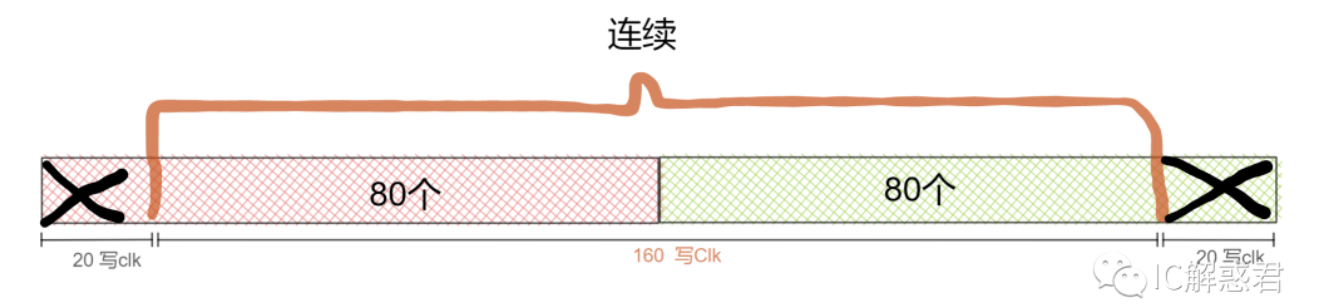

(1)假设FIFO的写时钟为100MHZ,读时钟为80Mhz,在FIFO输入侧,每100个写时钟,写入80个数据,在读数据侧,每个时钟读出一个数据,问FIFO设置为多少FIFO不会溢出??

[1] 在输入数据背靠背的情况下,进入( input**)FIFO的数据量:**

进入FIFO的数据量:160个 消耗的时间:160 个 写时钟

[2] 在输入数据背靠背的时间内,输出( output )端口输出的数据量 :

(1)因为输入输出端口的时钟频率不同,所以先把输入数据背靠背的时间换算到输出数据端口的时钟个数:(160 *(1/100MHZ) * / * (1/80MHZ)=128读时钟周期

(2)则输出端口在背靠背输入的时间**内输出的数据:128 *1 = 128个读数据

[3] 则FIFO的深度为:

160 (输入) - 128 (这段时间内的输出) = 32 (内部水池FIFO应该存的)

(2)假设FIFO的写时钟为wclk,读时钟为rclk,在FIFO输入侧,每B个写时钟,写入A个数据,在读数据侧,每Y个时钟读出X个数据,问FIFO设置为多少FIFO不会溢出??

[1] 在输入数据背靠背的情况下,进入( input**)FIFO的数据量:**

进入FIFO的数据量:2A , 消耗的时间:2A * (1 / wclk)

**[2] 在输入数据背靠背的时间内,输出( output )端口输出的数据量:

** (1)因为输入输出端口的时钟频率不同,所以先把输入数据背靠背的时间换算到输出数据端口的时钟个数:**

读时钟周期个数 :(2A * (1 / wclk))* / (1 / rclk)

(2)则输出端口在背靠背输入的时间内输出的数据:

读的数据个数: (2A* (1 / wclk) / (1 / rclk) ** * (X / Y)

[3] 则FIFO的深度为:

输入数据背靠背时间内的输入数据 减去输入数据背靠背时间内的输出数据

2A - [(2A * (1 / wclk)) ** / (1 / rclk)] ** * (X / Y)

-

IC设计

+关注

关注

38文章

1295浏览量

103900 -

fifo

+关注

关注

3文章

387浏览量

43635 -

时钟源

+关注

关注

0文章

93浏览量

15956

发布评论请先 登录

相关推荐

求助,FPGA fifo深度不够怎么办?

FIFO深度怎么设计

【教程】“最恶劣”的FIFO深度计算

谈一谈对穿越频率的理解

谈一谈对穿越频率的理解

谈一谈嵌入式开发怎么入门的

谈一谈嵌入式操作系统一些需要注意的点

谈一谈DALI的具体应用

LabVIEW FPGA模块实现FIFO深度设定

基于LabVIEW FPGA模块程序设计特点的FIFO深度设定详解

谈一谈FIFO的深度

谈一谈FIFO的深度

评论