2018 年,汽车行业“缺芯”潮来得猝不及防,而后波及所有电子元器件品类,自此汽车电子“一芯难求”成为街头巷尾热议的话题。今天,我们看到经过几年的上游扩产,叠加近期汽车终端市场的不景气因素,缺芯现象得到明显缓解,仅剩下少部分主控芯片依旧维持长交付周期的状态。

1

汽车电动化、智能化下的增量市场相当可观

回顾过去,真的只是电子供应链市场周期性波动带来的“缺芯”问题吗?回答是否定的,究其最深层的原因,还是汽车电动化、智能化趋势下电子电气架构变革带来的增量市场上升速度太快,导致车规级芯片市场供不应求,从而产生“缺芯+涨价”的应激反应。

汽车芯片主要分为功能芯片、功率器件和传感器三大类。在传统燃油车中,平均芯片搭载量约为 500-600 颗/辆,而随着前面提到的汽车电动化、智能化的演进,平均芯片搭载量已提升至 1000 颗/辆,在新能源车中更是超过了 2000 颗/辆,未来随着电车智能化的升级,还有望提升至 3000 颗/辆,甚至更多。

2

商业价值最大化L2/L2+是短期内的行业共识

作为汽车智能化的核心,近年来自动驾驶技术的发展非常迅速。当前,部分汽车厂商已经推出了具备 L2 级别自动驾驶功能的车型,比如特斯拉 ModelS、广汽新能源 AionS、小鹏 G3、蔚来 ES8、一汽大众探岳、长安 CS75、WEYVV6、吉利缤瑞等。

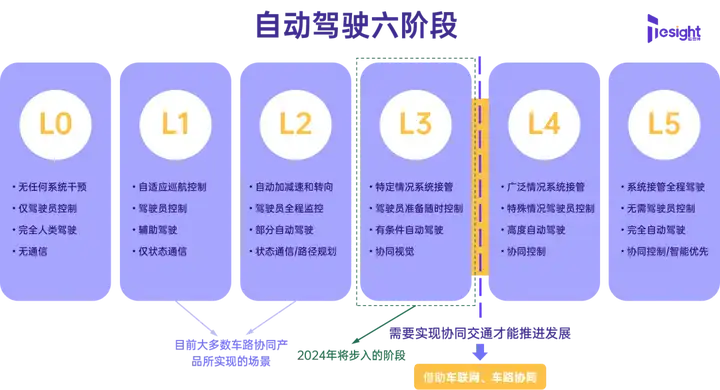

那么,到底什么是 L2 级别自动驾驶呢?事实上,市面上有两套自动驾驶分级标准,分别是 2014 年国际汽车工程师学会(SAE)首发的《SAE J3016 推荐实践:道路机动车辆驾驶自动化系统相关术语的分类和定义》,简称《SAE 驾驶自动化分级》;以及 2021 年我国国家市场监督管理总局出台的《汽车驾驶自动化分级》国家标准(标准号:GB/T 40429-2021)。两者的区别在于国家市场监督管理总局、国家标准化管理委员会将 L1 至 L2 级别统称为辅助驾驶,L3 至 L5 级别统则称为自动驾驶。下面,我们以国际标准为例来具体介绍一下。

在《SAE 驾驶自动化分级》标准中自动驾驶被分为 L0 级~L5 级

1

L0 级:无自动化,纯人工驾驶;

2

L2 级:部分自动化,虽然自动驾驶系统能够完成某些驾驶任务,但驾驶者仍需专心于路况,当系统出现差错时需要人为进行纠正,常配有自适应巡航系统、主动车道保持系统、自动刹车辅助系统和自动泊车系统等;

3

L3 级:有条件自动化,某些特定场景下的自动驾驶,车辆自动驾驶系统的优先级高于驾驶员,但是驾驶员可以通过紧急按钮随时取得车辆的控制权,如交通拥堵路段的自动跟车行驶、远程倒车入库等,以在公用路面上完成 L3 级别的自动驾驶车辆奥迪 A8 为例,其搭载了 24 个感应器和 41 种驾驶輔助系统软件;

4

L4 级:高度自动化,在规定的道路和环境中,车辆自动驾驶系统能够自主完成所有的驾驶操作,具备完全处理紧急情况的能力,驾驶员可以做自己想做的事情,如果出了事,责任将全部归属厂商,方向盘、油门、刹车等装置也或被取消;

5

L5 级:完全自动化,在所有道路和条件下,自动驾驶系统都能够完成驾驶任务,应对任何工况,驾驶员全程无需干预,此时也不再有驾驶舱的概念,汽车更像是一个智能机器人。

事实上,在 2022 年之前,全球汽车产业链上的企业对目标场景并没有那么清晰,所以总希望通过算力抬升来实现硬件冗余,而今天当自动驾驶往高阶发展,从 L2 开始逼近 L3,甚至再往上走,技术和产品批量落地面临的最大挑战是需求侧的承受能力,这正在倒逼车厂进行新一轮的成本管控下的系统优化。通过实践证明,这两年 L2、L2+级别的自动驾驶将成为车厂标配,这一趋势已形成行业共识。

3

自动驾驶技术演进下“大芯片”成为标配

随着自动驾驶技术的不断演进,不仅车载芯片的数量在逐步增加,在跨域集中式和中央计算式架构中,大芯片正在成为标配,芯片设计的复杂性急剧升高。

2014 年~2018 年间仍以分布式 E/E 架构为主,跨域集中式架构刚起步,主流玩家 Mobileye、英伟达和瑞萨、TI 等传统 MCU 厂商的上车智驾芯片算力大都在 10TOPS 以下,如牢牢占据 L1~L2 级别视觉 ADAS 芯片市场的 Mobileye EyeQ3/Q4 的算力仅为 0.256TOPS 和 2.5TOPS。

不过也有特殊的,比如 2016 年搭载于特斯拉 HW2.0 平台的英伟达 Tegra Parker SoC 算力就提高到了 24TOPS,同时把 GPU 路线的自动驾驶 SoC 正式推向市场。

2019 年~2023 年间跨域集中式架构发展提速,英伟达开始引领高算力市场,相关电子供应链结构同步发生转变,除了英伟达外,特斯拉自研 FSD 芯片崛起,国产品牌地平线、黑芝麻、芯驰等抓住国产替代窗口开始发力。此时,智驾芯片面向应用场景和汽车终端产品定位出现算力需求分化,行业形成共识,L2/L2+级别自动驾驶在短期内更具商业落地价值,纷纷发力抢占市场。

值得一提的是,在 L2/L2+级别的中高算力自动驾驶市场中,算力需求已经达到了 30 TOPS~1000 TOPS 这个范围,比如 2020 年英伟达发布的针对 L2 级别市场的 Xavier 芯片,已上车小鹏 P7/P5 等车型,算力为 30TOPS;2022 年地平线发布的 J5 芯片,已上车理想、比亚迪、蔚来旗下阿尔卑斯、哪吒等车型,算力为 128TOPS;同年英伟达又针对 L2+级别高阶辅助驾驶车型推出 Orin 芯片,成为主机厂合作的王者,算力为 256TOPS。根据业内人士反馈,Orin 芯片的出现给 Mobileye、地平线、高通、黑芝麻智能、寒武纪等自动驾驶芯片企业带来了空前压力。

4

EDA 正在助力汽车芯片厂商实现性能和先发优势

对于这些大芯片设计厂商而言,如何缩减上市时间取得先发优势,在提高算力、安全等级的同时,改善芯片的 PPA(功耗、性能和面积),成为共同的追求目标。

传统的 EDA 工具常使用“经验法则”,需要设计人员根据直觉和经验进行优化,这种建模和仿真技术存在很多局限性,包括:无法从以前的设计中汲取经验,导致生产力受限且设计不够准确;多次迭代导致设计时间增加;HLS 通常需要更多的时间来完成综合;布局和布线取决于设计师的预测/经验,会增加运行时间;就时间和资源而言,制造成本高昂等。与此同时,车规级芯片的质量在很大程度上取决于底层半导体技术和设计规则,因此对 EDA 又提出了更高的要求。

所以对于一颗车规级大芯片而言,为了确保设计的正确性,必须在生产制造前进行大规模的仿真和验证,而芯片的算力规模越大、集成度越高,仿真验证的过程就会越复杂,设计人员需要更快地实现收敛和验证,来降低成本并提高结果质量。同时,传统的随机/自动测试模式生成(ATPG)方案在故障覆盖率方面已经不能满足实际需求。因此,将 AI 和 EDA 融合是大势所趋。

Cadence 作为 EDA 领域的深耕者和领导者,可以提供汽车智能设计所需的全部 EDA 工具、设计流程等,帮助工程师加速自动驾驶设计。同时,通过将 AI/ML 功能融入现有的 EDA 工具中,能够从手动到完全自动化不同等级产生更好、更可预测的结果,助力汽车厂商利用多学科分析和优化(MDAO)技术提高整体设计,从而实现更快速、更优质的结果,系统的精确行为建模也提高了产品保真度和安全性。

下面介绍两个 Cadence 在自动驾驶中所提供的典型解决方案——Cadence Tensilica 处理器 IP、Xcelium ML。

Cadence Tensilica 处理器 IP

Tensilica 处理器 IP 是 Cadence 根据应用需求量身定制的差异化处理器系列 IP,可满足各类 ADAS 硬件加速平台需求,其 DSP 内核 Tensilica ConnX 支持用于 L2 级别自动驾驶下 ADAS 的激光雷达、毫米波雷达中的高性能数据处理,提供性能、功耗和面积的理想组合,同时其 DSP 处理器 Tensilica Vision 与 Tensilica Al 处理器的集成可轻松实现视觉传感器数据处理。

对于汽车芯片厂商来说,在将 Tensilica DSP 产品集成到系统级芯片的同时,可以快速、轻松地进行软硬件划分的探索分析,满足将来算法的演进同时大大降低 CPU,GPU 和 AI 处理器的负载。同时使用 Tensilica Instruction Extension(TIE)语言自动生成处理器扩展和与之匹配的软件工具,并创建特定领域的差异化解决方案。

值得一提的是,搭载 FlexLock 的 Tensilica Xtensa 处理器现已通过车规级安全认证,完全符合汽车安全完整性等级 D 标准,提供 ASIL-D 系统级和 ASIL-D 随机故障防护,适用于功能安全(FuSa)应用,可以帮助更多大芯片设计厂商将安全模块集成到 SoC 中,减少模块设计和验证时间,增加产品先发优势。

以汽车雷达模块中的 SoC 为例,其通常由多个处理元件组成,包括控制器 CPU 和一个或多个DSP 等。当 SoC 中的晶体管出现随机故障时,包括晶体管或其他物理元件磨损并卡在逻辑“0”或“1”处,由于 α 粒子引起的静态故障导致内存位从“0”翻转为“1”等永久性故障,或是由 SoC 中的信号串扰等噪声引起的瞬态故障等,这些故障都可能发生在与处理器紧密耦合的逻辑门或存储器中的处理元件中,最终造成安全问题。

因此,系统设计人员必须设定一个安全目标,即 DSP 中的随机故障不得导致车道标记等物体检测失败。该安全目标将指导设计人员采取适当的安全机制,以便在检测到随机故障时,安全控制器会收到通知并可以采取措施,例如重新初始化 DSP 等。如果 DSP 已经进行处理,则安全控制器负责采取措施确保在 DSP 重新初始化之前/期间达到安全状态。

在这种设计中,位于“安全岛”中的安全控制器可以起到安全关键决策的作用。当然,控制器也可能会出现随机故障,如果控制器检测到 DSP 故障,但控制器采取了错误的操作来响应该故障,从而使系统处于不安全状态,这类故障可能会产生严重后果,这种情况下设计人员就需要采用冗余的设计方法,让两个控制器同步运行,来大大降低此类事件发生的可能性。

综上,为了实现系统级别的安全目标,像雷达模块中的 SoC 这样的处理器设计是非常复杂的,所以芯片设计企业通常会向可靠的第三方购买 IP,来简化设计流程,提高流片的成功率,而 Tensilica 处理器 IP 是个不错的选择。

Xcelium ML

Xcelium Logic Simulation 是 Cadence 为 IP 和系统级芯片验证收敛提供的一款高速的仿真器,可为SystemVerilog、VHDL、SystemC、e、UVM、混合信号、低功耗和 X 态传播(X-propagation)提供业内优异的核心引擎性能,从而加快验证吞吐量。

其中,Xcelium Machine Learning(ML)App 利用专有的机器学习技术来缩短回归时间,可从以往的回归运行中学习并指导 Xcelium 随机引擎,在实现相同覆盖率的前提下大幅度减少仿真回归周期,或者产生特定覆盖点的激励触发更多的 bug 来提高验证质量。

同时,Cadence 对特定领域还提供了相应的 App,包括混合信号、基于机器学习的测试压缩和功能安全,可以帮助汽车芯片设计团队尽早实现对 IP 和系统级芯片(SoC)设计的验证收敛,非常适合 Level 2+级以上 SoC 设计。

“

瑞萨电子汽车 SoC 业务部杰出工程师Tatsuya Kamei对此表示

“将Xcelium Machine Learning(ML)App纳入验证流程,有助于我们在紧迫的期限内,通过更少的回归测试来加速完成覆盖率的收敛任务,同时最大限度地提高验证性能和整体验证效率。”

而在这段表述的背后,是瑞萨电子借助 Verisium AI-Driven 验证平台,整体调试效率提高了 6 倍,整体随机验证回归缩短了 66%;以及依托 Xcelium ML App,实现了回归用例 2.2 倍压缩和 100%覆盖率收敛的事实。

此外值得一提的是,瑞萨电子在不断使用机器学习进行回归迭代过程中,在实现 100% 覆盖率的前提下,将工作量减少了 3.6 倍。

瑞萨电子利用机器学习大大减少回归运行次数(从 3774 次减少到 1168 次),成功在规定时间内实现产品上市。除了节省资源、时间和加速覆盖率收敛外,Xcelium ML Apps 还为瑞萨电子节省了约 27 个工时。

写在最后

汽车产业的变革还在继续,芯片和电子系统的重要性只会越来越高。不可否认的是,在克服未知挑战的路上缺少不了整个产业链的通力合作,而 EDA 和 IP 将是贡献者链路上重要的一环。

-

Cadence

+关注

关注

65文章

933浏览量

142605

原文标题:从 L1~L5 自动驾驶芯片发生了哪些变化?

文章出处:【微信号:gh_fca7f1c2678a,微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

L3级自动驾驶即将全面商用,众车企蓄势待发

佑驾创新成功交付L4级自动驾驶小巴项目

FPGA在自动驾驶领域有哪些优势?

FPGA在自动驾驶领域有哪些应用?

Mobileye引领自动驾驶新纪元:L4级无人驾驶系统在德国成功路测

BK1661 全集成的单芯片 L1 频段 GNSS 解决方案

BK1662 单芯片L1/L5双频GNSS解决方案

驶向L3级自动驾驶:车路协同

从 L1~L5 自动驾驶芯片发生了哪些变化?

从 L1~L5 自动驾驶芯片发生了哪些变化?

评论