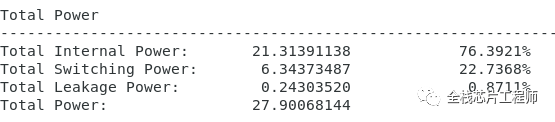

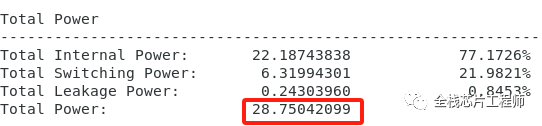

低功耗设计前,功耗为27.9mW。

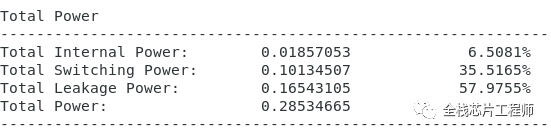

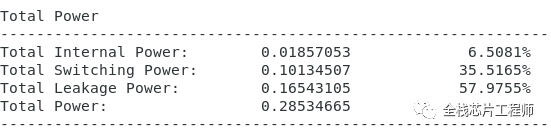

低功耗设计后,功耗为0.285mW,功耗降低98.9%!

(一)低功耗lowper debug

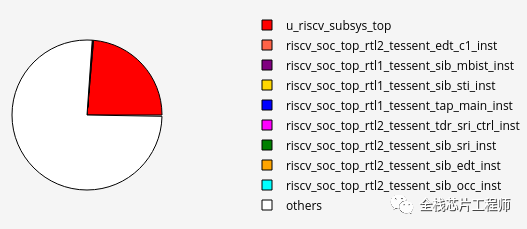

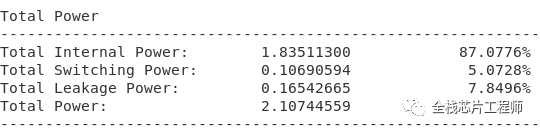

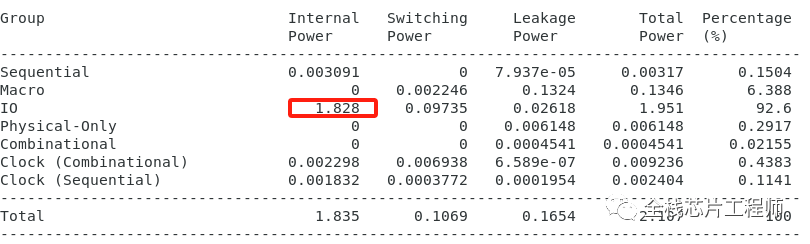

在低功耗P&R完成后,低功耗静态功耗为2.107mW,下图可以看到Internal Power为1.8mW占据了87%的比例,那么这1.8mW的功耗来自哪里?

小编首先联想到的就是时钟IO,进一步查看报告,可以看到就是IO的Internal功耗。

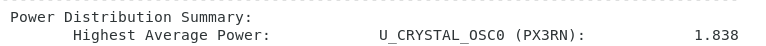

Summary也可以看到这个时钟IO PAD功耗占据了1.838mW。

按照低功耗的架构设计,U_CRYSTAL_OSC0的时钟应该关闭,且该IO PAD应该关电,那么Voltus功耗分析怎么做呢?欢迎加入景芯SoC全流程设计训练营实战吧。

修改后的功耗为:

如果不采用低功耗设计,芯片待机状态下功耗将是27.9mW,嵌入式设备时不可接受的,景芯SoC的全流程学员会深有体会,低功耗设计的重要性可见一斑!

(二)低功耗low power确认

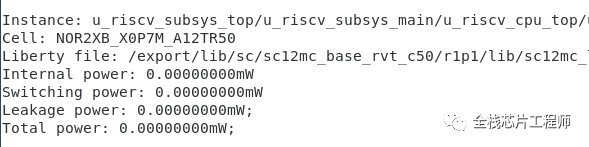

选中一个power gating domain(shut down domain)的STD CELL作为report对象,domain关电后,report_instance_power,发现其功耗确实为0。是不是很好玩?

审核编辑:刘清

-

低功耗设计

+关注

关注

0文章

80浏览量

16177

原文标题:芯片功耗从28mW降到0.28mW

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

实用手机充电器解决方案(30mW待机功耗)

ADS1284在测试功耗的时候发现,打开和关闭AD采集,整个系统的功耗相差四五十mW,怎么解决?

cogobuy降低功耗的措施

无负载功耗仅为150mW-PMP6710技术参数及设计

Block RAM的功耗始终为0mW

电源选择,功耗是3W待机时候100mw以内

滤波放大器如何降低功耗

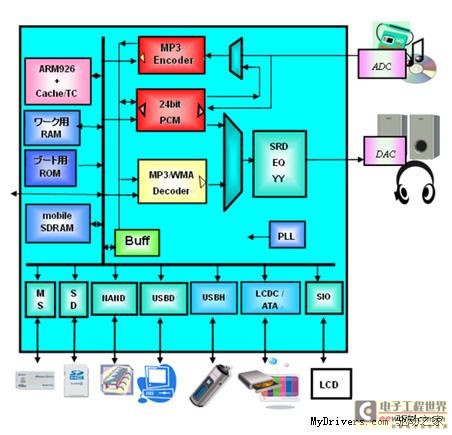

5mW 三洋推全球最低功耗音频处理芯片

AD9834: 20 mW功耗、2.3 V至5.5 V、75 MHz的完整DDS

请问芯片功耗如何从28mw降低到21mw呢?

芯片功耗从28mW降到0.28mW 功耗降低98.9%!

芯片功耗从28mW降到0.28mW 功耗降低98.9%!

评论