LVDS(low-voltage differential signaling)即所谓的低压差分信号,它是一种小振幅差分信号技术,使用非常低的幅度信号(250~450mV)通过一对平行的PCB走线或者平衡电缆进行数据的传输,该逻辑是为了用于替代发射级耦合逻辑(ECL)或者正反射级耦合逻辑(PECL)的低功耗逻辑。其主要的应用场景是高速背板、电缆和板到板数据传输和时钟分配,以及单个PCB内的通信链路。

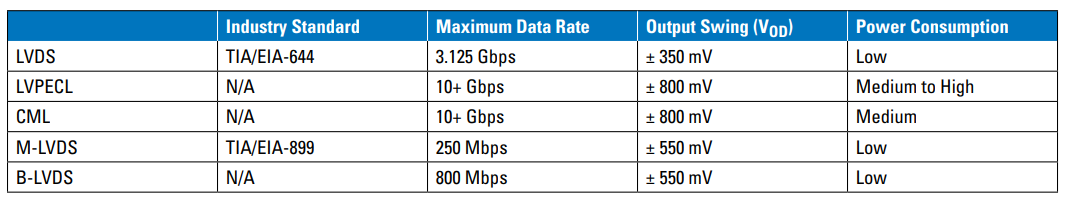

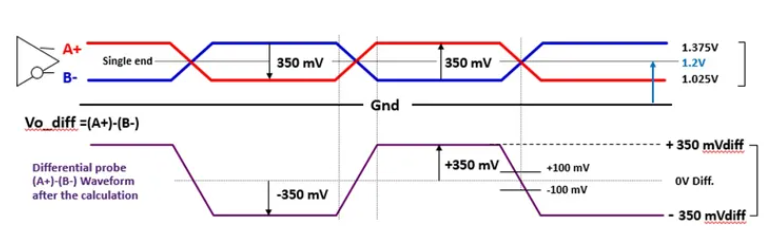

LVDS在两条平行的差分信号线上流经的电流以及电压振幅相反,噪声信号同时耦合到两条线上,而接收端只关心两个信号的差值,于是噪声被抵消。由于两条信号线周围的电磁场也相互抵消,所以差分信号传输比单线信号传输的电磁辐射要小的多。此外,该传输标准采用的是电流模式驱动输出,不会产生振铃和信号切换所带来的尖峰信号,具有良好的EMI特性,由于LVDS差分信号技术降低了对噪声的关注,所以可以采用较低的信号电压幅度,这个特性非常重要,它使得提高数据传输速率和降低功耗成为可能(如下表,对几种高速接口的速率进行对比),低驱动振幅意味着数据可以更快的翻转,由于驱动器是恒流源的模式,功耗几乎不会随着频率也改变,而且单路的功耗非常低。

因此,采用这种技术后,只要保证一对平行传输线的长度足够一致,并且在接收端提供良好的端接阻抗,以减小反射信号的产生,就可以提供非常高的数据传输速率。

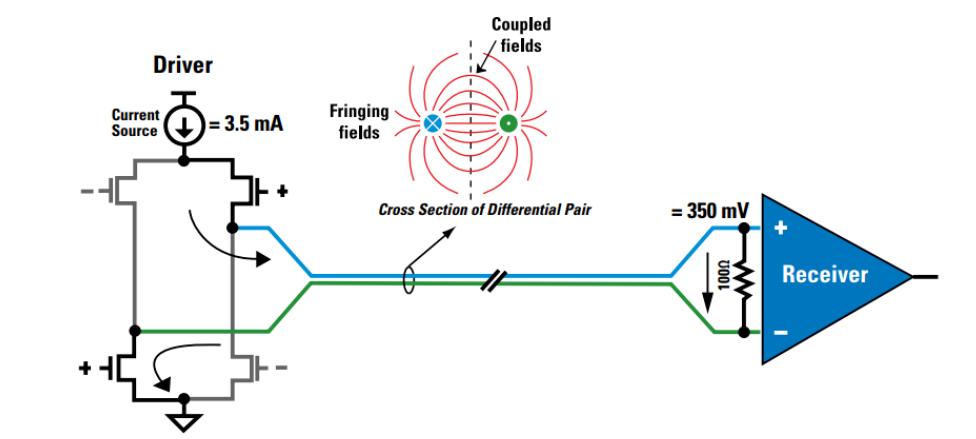

如上图所示为LVDS的工作原理示意图,其驱动器由一个恒流源(通常为 3.5mA)驱动一对差分信号线组成。在接收端有一个高的直流输入阻抗(几乎不会消耗电流),所以几乎全部的驱动电流将流经 100Ω的终端电阻在接收器输入端产生约 350mV 的电压。当驱动状态反转时,流经电阻的电流方向改变,于是在接收端产生一个有效的"0"或"1"逻辑状态。LVDS 技术特点包括:

1、高速传输能力,LVDS的传输能力最高可以达到2Gbps;

2、低电压、低功耗,LVDS采用CMOS工艺实现,静态功耗比较低;

3、低噪声辐射;

4、采用差分传输模式,有着比较强的抗干扰能力;

LVDS比传统的单端信号拓扑结构(比如LVTTL/LVCMOS)有许多优点,主要优点是EMI(电磁干扰)减小,更快的数据速率,更远的扩展传输距离等。

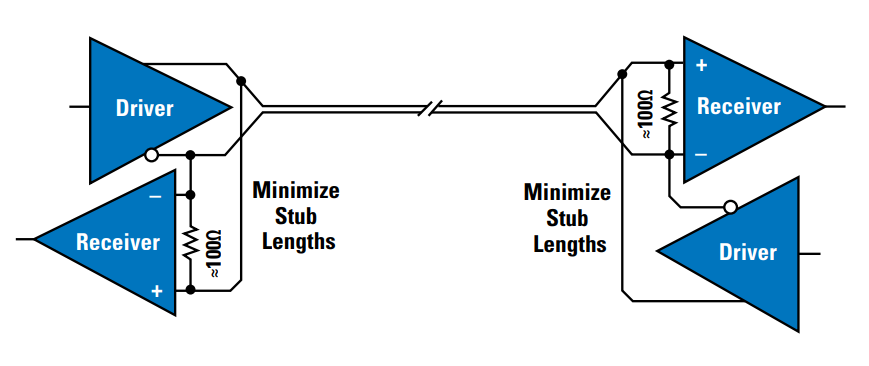

此外,从LVDS的结构原理上分析,一对差分信号线只能进行一个方向的数据传输,也就是说LVDS是一种单工通信接口,但是我们常见的接口比如 USB接口也只用了一对差分线,为什么可以双向传输呢?原因很简单,是因为LVDS使用了两对驱动器和接收器组合而成,如下图所示,所以LVDS本质上是一种半双工通信。

在实际应用过程中,LVDS的TX和RX根据不同的共模、摆幅,有不同的端接方案,甚至需要对接不同的逻辑,比如LVDS逻辑作为TX,CML逻辑为RX,需要设计其端接电路,下面详细讲解LVDS的端接方案。

1、直流耦合

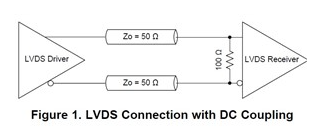

直流耦合比较简单,在接收端跨接一个100的差分端接电阻即可,该端接电路应该尽量靠近接收器放置,以在接收端产生差分电压,并且作为匹配传输线阻抗,可以减小反射问题。

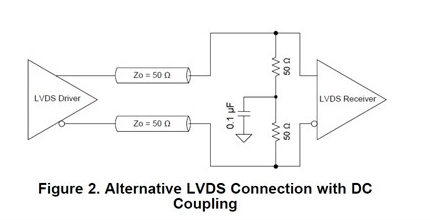

另一种端接方案如图2所示。它使用两个电阻分流端接,并且中间使用一个电容到地的端接方法。该电容器可滤除共模噪声并有助于抑制传输线产生偏差(这可能是由于差分线不匹配或驱动输出产生偏差)。电容器的值取决于工作频率,就像把它看作交流分量短路。0.1 µF的电容值对于大多数高数据速率(1 Mbps及更高)已足够。

2、交流耦合

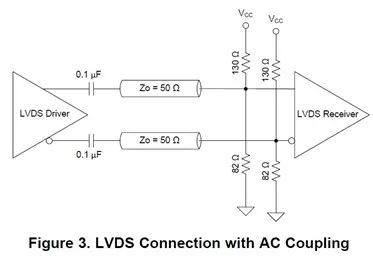

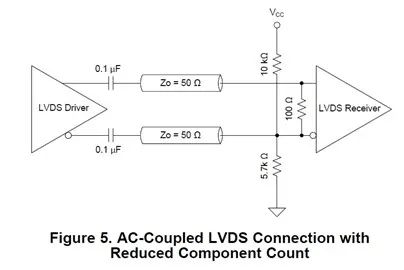

图3所示为交流耦合配置下的端接。 请注意:对于交流耦合,需要对传输的数据进行直流平衡(例如,使用8b/10b编码)这是一个很容易被忽视的问题,比如一些LVDS逻辑的serdes,AC耦合时,DC不平衡,会引起传输误码率变差问题 。

图3中,接收器输入端的电阻网络将DC共模恢复到1.2 V(假设Vcc = 3.3 V),这处在标准LVDS接收器的输入共模范围的中间值。此外,电阻器网络在接收器的输入端提供100Ω端接。如果在LVDS接收器中集成了端接电阻,则应选择更大的电阻值,以免改变接收器输入端的有效端接电阻。建议的上拉值为10kΩ,下拉值为5.7kΩ。交流耦合电容的值取决于工作频率,因为它隔离直流分量,但是看起来就像是交流分量短路。0.1 µF的电容值对于高数据速率(1 Mbps及更高)已足够。

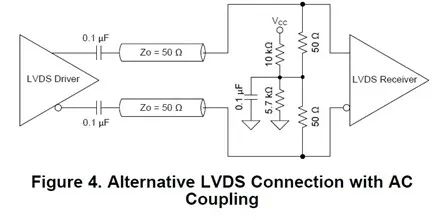

图 4所示为另一种电路。该电路除偏置电阻网络外,还使用分流端接和中间加电容到地的方法。该电容器可滤除共模噪声并有助于减少传输线偏差。与图3中的电路相比,该电路的另一个优点是功耗更低。

图5所示为图3中电路的另一种变型。其仅使用一对电阻在负输入端子上提供偏置。正输入端子还将通过100-Ω端接获得共模电压。这种方法的优点是减少了零器件的数量。缺点是正负输入端之间存在一定的偏差。

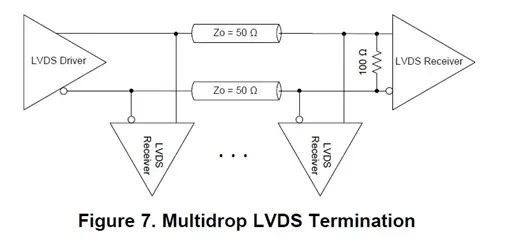

多支路LVDS端接

在多支路配置中使用LVDS收发器时,仅需要在最远接收器的输入端上端接100ohm匹配电阻,如图7所示。

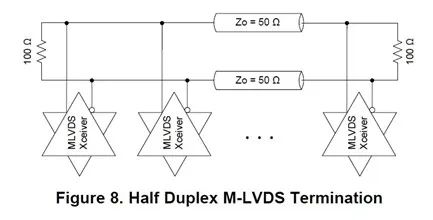

在半双工多点配置中 ,需要在总线两端进行端接,如图8所示。不必将端接置于靠近接收器的位置,而是将其置于总线两端的最远点。

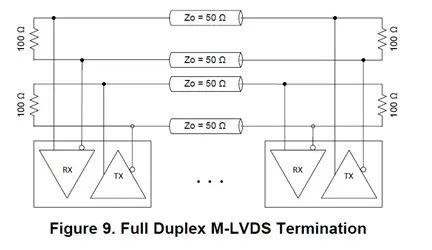

如果使用诸如全双工M-LVDS收发器 ,则使用两个差分对,每个差分对在连接两端都需要两个端接,如图9所示。

除了上述LVDS对接LVDS之外,LVDS还可以和其它逻辑进行通信,我们将在下一篇文章中详细讲解。

-

接口

+关注

关注

33文章

9603浏览量

157654 -

lvds

+关注

关注

2文章

1244浏览量

70253 -

低压差分信号

+关注

关注

0文章

14浏览量

9798 -

PCB

+关注

关注

1文章

2357浏览量

13204

发布评论请先 登录

LVDS的工作原理和特点

LVDS的工作原理和特点

评论