最近参与之前做的一款芯片的回片测试,回片测试结果不太友好,这不又忙着找问题,于是各种测试肯定是少不了的。就说这测试,没想到就被一个小小的电感给摩擦了。具体是咋回事呢,下面咱慢慢聊。

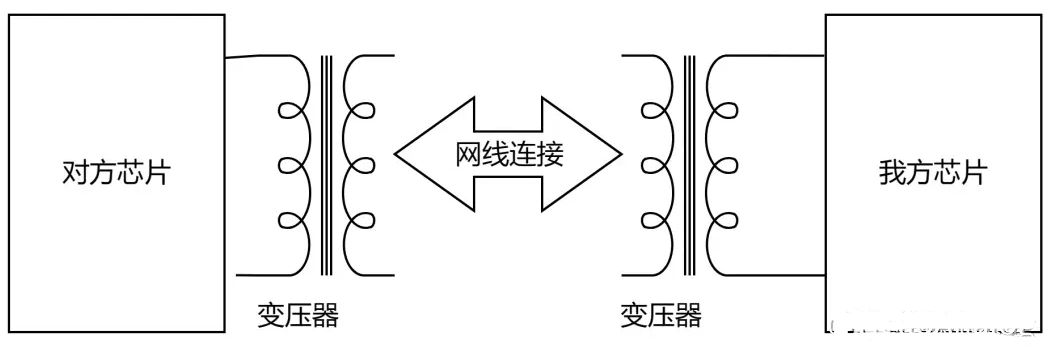

首先这款芯片常见的连接方式如下图,可以进行数据通信,使用网线连接。还必须得有变压器。变压器是啥,这玩意简单理解就是两个线圈互相耦合呀,初级侧和次级侧线圈就是个电感L啊。请记住这个等效的L,我就是被这个小东西给摩擦的。

图1:双芯片通信连接示意图

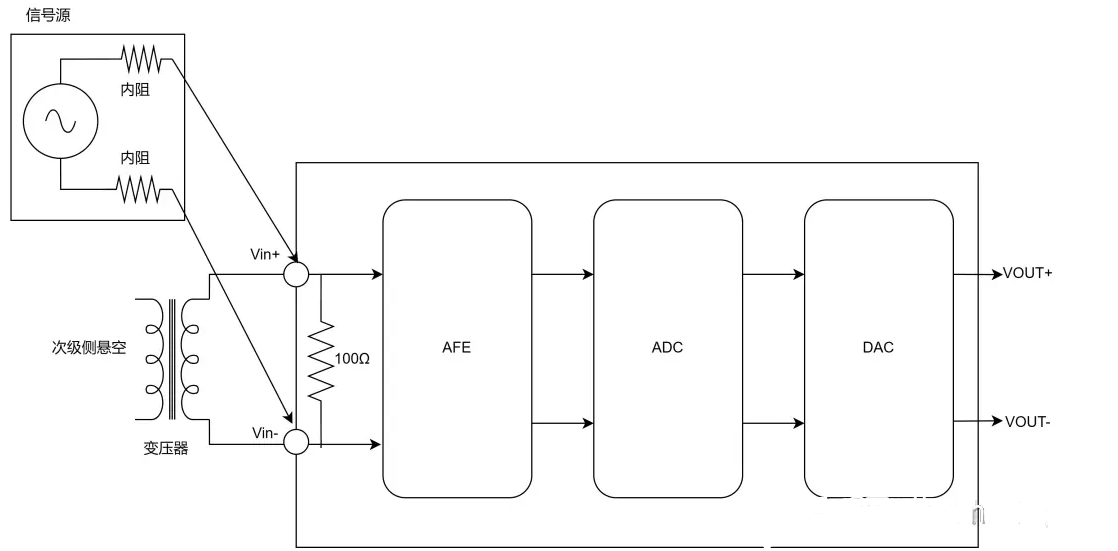

说到我们要测的东西,可以看下下面的测试框图。芯片接收信号端口(Vin+和Vin-)进去有两大电路;AFE和ADC。AFE是进行信号处理的,比如改变个增益,提供点均衡能力啥的,ADC更不用多说了,实现模数转换的。图上这个DAC是芯片内部设计用来进行测试的,它可以将ADC的量化结果转换为模拟波形从端口输出(也就是图上的VOUT+和VOUT-)。可以通过波形观察ADC的转换是否有明显错误。说到这里,不得不说,芯片可测性设计是真重要啊,真乃保命脱嫌疑的重要工具,下次一定专门写一篇可测性相关的文章(flag就立在这里了)

图2:芯片接收测试示意图

测试过程是这样的:我们拔掉网线,保证变压器次级侧悬空,从外面用信号发生器给Vin+-输入一个正弦信号,为了避免内部电路有限带宽对信号造成衰减,我们将信号频率设置在了10KHz~5MHz范围,固定输入摆幅为500mV。该频率范围远小于前级电路的-3dB带宽,不用担心信号衰减问题,DAC电路的输出为VOUT+和VOUT-,这两个引脚是芯片引脚,因此可以用于观测输出信号。

通过示波器观测,出现了奇怪的现象,我们看图3。因为给的信号频率都不高,相对一个125MSPS的ADC而言,算是很低频的输入了。然而奇怪的是,频率从10KHz开始不断变大,输出幅度不断变大,当频率大于某个拐点之后,输出幅度才稳定了下来。这很奇怪,正常应该是在10KHz~5MHz这个频率范围内,幅度不应该变化呀。

图3:频率从10KHz~5M观测到的波形现象

但你看这个测试到的现象,频率小,幅度小,频率大,幅度大,表现多么像一个高通滤波器的特性啊!沿着这个思路,我们继续往下思考。我们知道,ADC和DAC本身是没有这种特性的,于是我们返回去用示波器观察了输入信号,果然,输入信号表现出了和图3一样的现象:在频率变大的时候幅度也会变大。好吧,现在算是知道了问题出在输入信号上,可这现象也太怪了,毕竟端口上没有串联电容,那这种高通特性是如何形成的呢?

思考漫无头绪的时候,只得返回去查查板子,看端口那里到底有什么特殊的地方。看来看去,发现端口只接了变压器,但其另一端是悬空的,总不能是它影响的吧?我们下意识觉得不能,因为“悬空”两个字确实有魔力,能让你下意识地将“悬空”和“没有影响”等效起来。所以那个下午又是没有进展的半天。要说找到原因,还是在晚饭后,重新梳理下午的测试现象的时候,才意识到变压器是会影响信号的。以前是陷入了思维惯性里面,没有联想到其实电感L和R在当前这个测试里是有可能造成高通特性的。图2变压器的初级侧可以等效成一个电感,并挪动一下相关器件的位置,最后用图画出来,如下图4所示:

可以看到,输入阻抗是由L和R并联贡献的,我们知道L的交流阻抗是频率越小,阻抗越小,因此Rin的曲线应该是如下图所示的样子。

图3:Rin随频率变化趋势

输出电压是信号源内阻和RL的分压,这也就意味着输出电压会随着频率的变大而变大。这在原理上是说的通的。那么实际是不是我们分析的这样呢?于是我们拆除板子上的变压器重新进行测试,发现信号的高通特性消失了。说明我们的分析是对的,奈斯!

小结:

平常遇到的滤波网络多是电容电阻型的网络,电感参与的拓扑属实少见,这个例子里的特殊之处是变压器一侧事实上充当了电感的角色,而对于连接到输入端口的这一侧而言,不管另一侧是否悬空,都会对输入阻抗造成影响。

审核编辑:黄飞

-

变压器

+关注

关注

159文章

7503浏览量

135754 -

线圈

+关注

关注

14文章

1832浏览量

44521 -

电感

+关注

关注

54文章

6145浏览量

102483 -

数据通信

+关注

关注

2文章

432浏览量

33793 -

信号发生器

+关注

关注

28文章

1478浏览量

108838

发布评论请先 登录

相关推荐

一个模拟工程师被一个小小电感给摩擦了?

一个模拟工程师被一个小小电感给摩擦了?

评论