阻抗匹配在高速串行传输系统中,有着非常广泛的应用,目前主要有以下几类实现方法,根据阻抗匹配的位置:

(1)PCB板上阻抗匹配

(2)片上阻抗匹配

在PCB上靠近芯片的位置直接端接阻抗匹配和片上阻抗匹配,可以达到很高的精度和稳定性,但是需要占用很大的面积,而且随着系统复杂度的增加,多处都会用到阻抗匹配,这时就需要在片上去集成阻抗匹配电阻。而根据电阻本身的性质,可以分为无源电阻和有源电阻,这种分类属于片上阻抗匹配的范畴。无源电阻通常采用的是多晶硅电阻,可以将多晶硅直接放到终端作为匹配电阻,多晶硅具有很好的线性度和温度特性,且电容负载小,但是去缺点就是精度不高。以TSMC 65nm工艺为例,其精度仅为1±30%,但是高速串行接口对匹配电阻的精度要求却非常高,因此无论是从PVT的角度,还是从多晶硅电阻本身的精度来说,都需要对其进行精确校准。

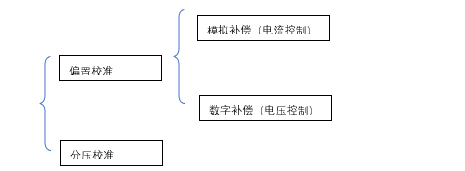

当前主要的校准方法分为下面几类:

偏置校准,主要是通过芯片内部的电流镜向外部精密校准电阻和内部校准电阻BLOCK灌电流,通过产生的偏置电压来调节需要校准的电阻模块,调节的方法也可以分为两类:模拟电流控制和数字电压控制。

模拟电流控制是通过模拟偏置电压控制Vgs电压,进而控制流过输出驱动器transistor的电流,其缺陷很明显,对干扰和噪声很明显;而数字电压控制,是通过电压来打开或者关闭并联的输出驱动器,对噪声具有很好的抑制性,也很容易进行数字化。

I/O端接阻抗校准电路如图1所示:包括模拟和数字两个部分,此外在芯片外部有200ohm的高精度电阻(也可以设计为其它阻抗,比如1.8K等),在芯片内部有一个集成的参考 电流镜电流源源 (提供3.25mA的DC电流),该电流镜有3条支路,分别给TX、RX和外部REXT校准电阻,而每个支路的开关是由CMOS传输门(TG)实现的(在忽略失配的情况下,电流镜的电流假定完全一致)。详细的电流镜和开关电路如下图所示:

校准电路,实际上校准的是TX和RX校准电路的replica blocks(后面统一称为复制块),所谓复制,指的就是的复制实际上的TX/RX的input/output端接匹配电路,有一点差异就是, 复制块需要校准的阻值和片外精密校准电阻并不一定相等,在此案例中,复制块目标校准电阻值为200ohm。

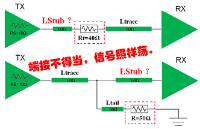

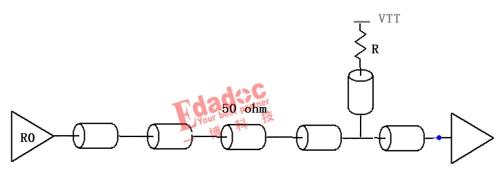

如上图所示,显示了一个简单的TX到RX的link架构:TX 输出端接电阻和输出buffer,传输线(50ohm)和RX端的input端接电阻模块,而普通的接口,TX只有1个buffer,RX只有一个差分运放。

在校准过程中,TX/RX端的端接电阻,会从校准电路已经校准完成后的寄存器中中获得复制块的二进制校准代码,然后在TX/RX的端接电路中设置50ohm的阻抗。因为复制块的牧宝校准阻抗是高速Link端接阻抗的4倍,因此会在校准代码的基础上进行处理,设置在TX/RX端接电阻阵列中,从而产生50ohm的阻抗。

如上图所示,复制块电路中,包含不同阻值的GROUP,每个GROUP都有并联的电阻和控制MOS(可以在截止或者三极管区域工作),每个电阻都可以通过MOS的开关进行控制(使用来自逻辑块的二进制代码),每个GROUP的阻值都是下一个的两倍,在此方案就有7个GROUP,第一个电阻最小(32X),第六个只有1个电阻(X)。

MSB[5]的二进制代码连接到最小的电阻GROUP(32X),LSB[5]就连接到了最大的电阻GROUP,为了避免Rcal的电阻过大,因此增加了一组最小的GREOUP(R=64X)。

校准电路在各种PVT条件下,提供了200ohm的恒定电阻,但是通常电阻变化范围可以达到±50ohm,所以在典型情况下,至少需要150~250ohm的电阻校准范围,这一条件被用于选择每个replica模块的电阻值。

在本文提出的解决方案中,常开的GROUP的阻值为300ohm(64X=300ohm),因此当二进制代码为0的时候(Vcal=000000),总阻值就是300ohm,而当所有的GROUP都打开时(Vcal=000000),总阻值为150ohm。

对于中间的输入二进制代码,在典型的情况下,具有200ohm左右的复制模块电阻是非常重要的。

TX和RX复制块的校准原理基本都是一样的,但是有个小差异:TX的输出端接电阻block是驱动电路的一部分,上拉和下拉路径上有两个transistor,第一个transistor用于数据输入,第二transistor则被TX复制块的二进制代码进行控制,因此对TX电路,只有下拉电路被用在复制块中,在校准完成之后,二进制代码也会被用在TX上拉电路中。事实上,TX的复制快每个电阻都可以表示为两个NMOS管加上一个电阻串联,如下图所示:

第一个transitor接收二进制代码,第二个晶体管被拉高并且常开,RX复制模块的单电阻块被表示为NMOS晶体管(二进制输入)和电阻串联连接。

I/O端接电阻校准电路有如下几个部分组成:

(1)逻辑控制模块;

(2)多路复用器;

(3)比较器;

逻辑控制模块用于提供所有的数字信号,比如校准代码(Vcal)、开关信号(Vswitch)用于控制电流开关、多路复用器、和复位信号去写数据/复位寄存器(寄存器用于保存校准代码),比较器用于比较复制块的校准电压和外部参考电压,输出电压(Vcomp)作为逻辑模块的输入。

校准过程如上表所示,从RX开始,一个3-bit的信号(由逻辑模块产生),用于控制电流开关,切到RX mode(这意味着没有电流通过TX 复制块),电流通过RX复制块和外部校准电阻,Vswitch信号会控制多路复用器并将其路径打开,

将RX复制块的电压送到比较器中;在下个阶段逻辑控制模块,开始增加6-bit的校准代码(Vcal)并改变RX复制块的阻抗,精确校准依赖于校准bit位(bit位越多,校准的就越精确),校准复制块时,将从最高值(vcal=000000)开始,此时复制块的阻值大约是300ohm,在校准结束后,复制块的阻值最小,因为所有的电阻blocks都是打开,并且是并联状态(Vcal=111111)。阻值也会落到150ohm,校准step将会有63步。

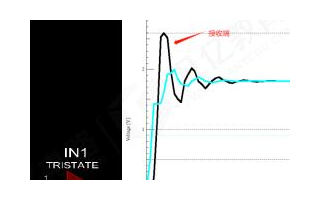

Nstep=2^n-1

Vext是校准电阻的正相输入(外部压降是200*Iref),RX复制模块的电流也是恒定的(等于Iref),但是其实际阻抗在校准期间是在减小的,因此RX复制块的压降也在减小,同时,当复制块的压降达到外部参考电压时(Vact=Vext),比较器的输出会从0切到1(Vcomp=1),此时逻辑模块将会停止减小校准码(Vcal),并将固定的校准码存储在寄存器中,这个校准码将会从寄存器中传输给真正的输入端接模块,提供固定的50ohm电阻(RX复制块的1/4)。

-

芯片

+关注

关注

456文章

50892浏览量

424316 -

阻抗匹配

+关注

关注

14文章

353浏览量

30824 -

电流源

+关注

关注

4文章

384浏览量

29319 -

PCB

+关注

关注

1文章

1810浏览量

13204

发布评论请先 登录

相关推荐

传输线在阻抗匹配时串联端接电阻为什么要靠近发送端

端接电阻没选对,DDR颗粒白费?

在电路中电阻的两端并联一个电容或电容一端接电阻一端接地分别有什么作用

不加端接电阻的快乐,你们绝对想象不到!

探究电阻布局对端接效果的影响

不加端接电阻的快乐,你们绝对想象不到

改进的LDO稳压器吸收PECL端接电流

探究电阻布局对端接效果的影响

详解芯片端接电阻校准方法

详解芯片端接电阻校准方法

评论