增加3D(三维)NAND闪存密度的方法正在发生变化。这是因为支持传统高密度技术的基本技术预计将在不久的将来达到其极限。2025 年至 2030 年间,新的基础技术的引入和转化很可能会变得更加普遍。

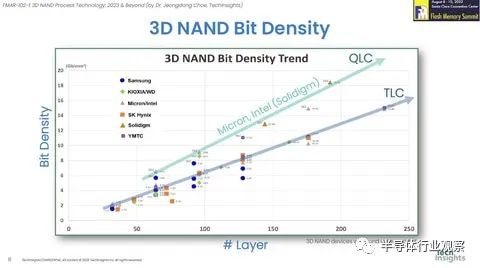

自2013年3D NAND闪存开始商业化生产以来,存储密度以每年1.41倍左右的速度持续提升。从国际会议 ISSCC 上展示的原型硅芯片来看,2014 年存储密度为每平方毫米 0.93 Gbit,但 2024 年将达到每平方毫米 28.5 Gbit。简单对比一下,10年间存储密度增加了30.6倍。

提高3D NAND闪存存储密度的四项基本技术

迄今为止,3D NAND闪存的存储密度主要通过采用四种基本技术(方法)来提高。它们是“高层建筑”、“多值转换”、“布局改变(存储单元阵列和CMOS外围电路的单片堆叠)”和“小型化(缩短横向尺寸)” 。

2013年宣布开发和商业化时,3D NAND的层数为24层,从今天的角度来看,这似乎很小。尽管如此,当时的制造极其困难,业内人士传言,第二年决定开始商业化生产的三星电子的制造良率还不到一半。

之后,堆栈的数量迅速增加。四年后,即 2017 年,这个数字翻了两番,达到 96 个。八年后,即2022年,达到了238层,大约增加了10倍,而次年,即2023年,则突破了300层。

由于增强型多级存储器,存储器密度是平面 NAND 的 1.5 至 2 倍

简单对比一下,“高层”对存储密度的贡献“10年大约是10倍”。然而,正如已经提到的,实际上,这个数字在10年内增加了大约30倍。其余三倍的提升都是通过其他基础技术实现的。

一个代表性的例子是“多值”。平面(2D)NAND闪存中开始引入的多级存储一直以2位/单元(MLC)方法为主,而3位/单元(TLC)方法仍然处于边缘地位。除了3D NAND闪存的第一个原型是MLC之外,TLC从一开始就成为主流。与平面NAND闪存相比,存储密度提高了1.5倍。

3D NAND闪存进一步发展了多级存储技术,并将4bit/cell(QLC)方法投入实际应用。这相当于平面 NAND 闪存 (MLC) 存储密度的两倍,是现有 3D NAND 闪存 (TLC) 存储密度的 1.33 倍。

改变布局的巨大威力

我们能够确认,通过“高层建筑”和“多值(强化)”,存储密度将增加10倍×2倍(最大)或20倍。当您达到“30 倍”时,剩下的就是“1.5 倍”。这就是第三个基本技术“布局改变(存储单元阵列和 CMOS 外围电路的单片堆叠)”发挥作用的地方。

这个想法很简单:在布局更改之前,存储单元阵列和 CMOS 外围电路并排布局在硅芯片上。存储单元阵列的底部有一块硅基板,但里面没有内置任何电路。可以说,这里已经变成了一块“空地”。

通过在该空余空间中形成CMOS外围电路,将减少硅面积。当然,可以通过仅在存储单元阵列下方形成一些而非全部CMOS外围电路来增加存储密度。换句话说,存储密度的提高速度是由布局决定的。

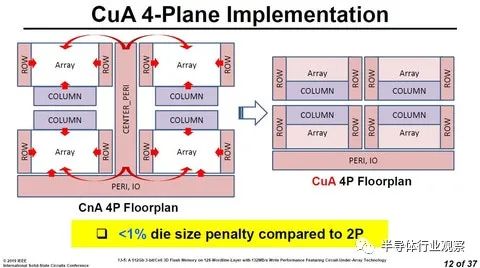

例如,东芝存储器(现Kioxia)与西部数据(以下简称WD)联合开发团队在2019年国际会议ISSCC上公布的3D NAND闪存,其存储单元阵列具有两个平面(划分数)除了将平面数量从1个增加到4个之外,大部分CMOS外围电路都形成在存储单元阵列正下方的硅衬底上。

注意,增加平面分割的数量的目的是为了提高操作速度或者缓解操作速度的下降。

增加平面划分的数量会增加行(ROW)解码器和列(COLUMN)解码器的数量并增加硅面积。东芝内存-WD联盟表示,从2个平面改为4个平面将使硅芯片面积增加15%。

如果将CMOS外围电路直接布置在存储单元阵列下方,则硅芯片面积的增加可以保持在仅1%。简单计算一下,存储密度提升了12%左右。

使用传统技术的高密度限制

随着存储密度的增加,这些传统技术在技术上变得更加困难。开发下一代 3D NAND 闪存就像攀登永无止境的斜坡,随着进步,斜率也会越来越大。

各大NAND Flash公司自开发以来,经过反复的换代,目前的世代已经达到了第6代至第8代。斜坡已经变得相当陡峭,公司正在认真寻找替代路线(基本技术)。

让我们简要讨论一下每项基本技术的问题。

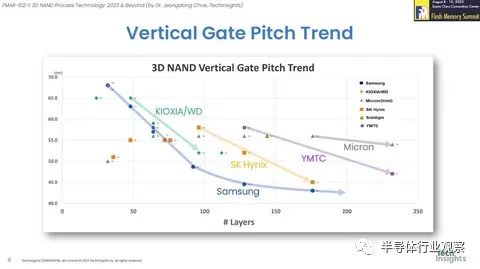

第一步是“高层建筑”。由于字线提取区域的扩大而导致效率降低,由于层数增加(垂直划分存储单元阵列的单元,也称为甲板或插头)而导致对准难度增加,工艺步骤数量增加以及字线变细。其中包括字线电阻的增加(一种缓解高层结构导致的存储器通孔深宽比增加的方法)、上下相邻单元之间的电干扰增加以及字线数量的减少。每个单元的电荷(电子)。

接下来我们来说说“多层次”的局限性。多级存储技术有一个固有的弱点,即随着位数的增加,效率下降,技术难度迅速增加。

从 1 位/单元 (SLC) 到 2 位/单元 (MLC) 的转变原则上使存储密度加倍。在随后从 MLC 到 3 位/单元 (TLC) 的转变中,存储密度的增长率大幅降低至 1.5 倍。从TLC到4bit/cell(QLC)的过渡中,存储密度的增加率更低,为1.33倍。

另一方面,阈值电压阶跃的数量每 1 位加倍。TLC 有 8 个步骤(7 个步骤,不包括擦除),QLC 有 16 个步骤(15 个步骤,不包括擦除)。如果写入(编程)电压范围相同,则增加 1 位将使阈值电压裕度减少一半。尽管QLC已经商业化生产,但PLC的实际应用仍不清楚。

接下来是“布局变更(存储单元阵列和CMOS外围电路的单片堆叠)”。这种方法有两个主要缺点。一是一旦在一代引入,即使在下一代引入,效果也保持不变。其次,由于存储单元阵列是在形成CMOS外围电路之后制造的,所以在存储单元阵列工艺期间施加的热处理降低了CMOS外围电路的性能。换句话说,存在运行速度降低的风险。

CMOS外围电路的性能下降和存储单元阵列的热处理温度之间存在折衷关系。外围电路和单元阵列的性能很难同时优化。此外,更高结构的进步可能会进一步恶化由于存储单元阵列的热处理而导致的外围电路的性能恶化。

最后一步是小型化。当垂直沟道(存储器通孔)做得更薄时,沟道电阻会增加。这导致单元晶体管的性能下降。垂直通道的直径只能减小到一定程度。

突破高密度极限的基础技术候选组

解决上述限制和问题的基本技术已经被提出,并且研究和开发正在进行中。下面我们来介绍其中的一些。

将“超越高层建筑极限”的候选基础技术包括将字线金属从目前的钨(W)改为电阻率较低的金属(缓解字线电阻的增加),以及垂直沟道材料。由现在的多晶硅改为单晶硅(缓解沟道电阻的增加),将电荷俘获栅极绝缘膜由现在的氮氧化物膜改为铁电膜(不依赖于电子数量的介电膜) ). 除了目前存储单元阵列各层(甲板、插头)之间的单片连接外,还将引入混合(晶圆键合)(缓解工艺难度的增加)。

将“超越多值技术极限”的基本技术候选包括将单元晶体管的存储方法从当前的电荷陷阱技术改为浮动栅极技术(缓解阈值电压裕度降低)(增加将5-位/单元(PLC)系统投入实用)。

混合堆叠是一种候选基本技术,“超越了布局变化的限制(存储单元阵列和CMOS外围电路的单片堆叠)”。存储单元阵列和CMOS外围电路形成在不同的晶片上,并且将晶片接合在一起。这样做的优点是可以优化存储单元阵列和CMOS外围电路工艺。随着每个输入/输出引脚的传输速率超过 5 GT/s,引入混合堆叠的可能性就会增加。

拥有替代技术的候选者非常重要,即使它们不完整,以防当前技术达到其极限。3D NAND闪存的高密度尚未达到极限。通过改进新的基本技术,甚至可以达到 1,000 层。这完全取决于你能在多大程度上投入你的资源。

审核编辑:汤梓红

-

芯片

+关注

关注

454文章

50677浏览量

423005 -

闪存

+关注

关注

16文章

1782浏览量

114881 -

NAND

+关注

关注

16文章

1680浏览量

136106 -

3D

+关注

关注

9文章

2872浏览量

107455 -

存储器

+关注

关注

38文章

7481浏览量

163751

原文标题:3D NAND,如何发展?

文章出处:【微信号:芯长征科技,微信公众号:芯长征科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

提高3D NAND闪存存储密度的四项基本技术

提高3D NAND闪存存储密度的四项基本技术

评论