结终端技术(Junction Termination Technology,JTT):

结终端技术是通过缓解或者避免电场集中效应而提高耐压的技术。(器件耐压一般由表面击穿电压决定)

横向功率集成器件的结终端技术:

一类是在主结附近引入电荷,利用电荷产生的附加电场来调制电场,降低主结的电场峰值,并扩展耗尽区宽度,从而获得优化的电场分布,此类技术通常用平面工艺,常见的包括场板及结终端扩展。

另一类是去除曲率大,电场集中的结面部分,如采用刻蚀去除电场集中的半导体区域,或者刻槽并填充绝缘介质,将高电场转移至临界击穿电场更高的绝缘介质中,从而提高击穿电压,称为沟槽终端技术。

设计与制造中常常将两种以上的结终端技术组合使用,形成复合终端技术以提高耐压并缩小终端面积,同时提高器件的可靠性。

.1场板技术(Field Plate,FP)

场板技术工艺相对简单且工艺兼容性好,是目前最重要和最常用的结终端技术之一。

基本原理:引入电荷产生附加电场,减小原来的电场峰值,同时使耗尽层扩展。

广义的场板可分为三类:

1.金属场板,金属覆盖于半导体表面的绝缘介质上且一端接固定电位,如接源的源场板,接栅的栅场板,接漏的漏场板。

2.浮空场板,其未与电极相连,无固定电势,处于浮空的状态

3.阻性场板,也称电阻场板,通常采用半绝缘多晶硅(Semi-Insulating Polycrystalline Silicon,SIPOS),其两端分别与器件的两个电极相连,因为场板本身不绝缘且两端存在电势差,在阻性场板两端之间就有电流流过,从而在电流流过的方向形成压降,调整器件表面电场分布。

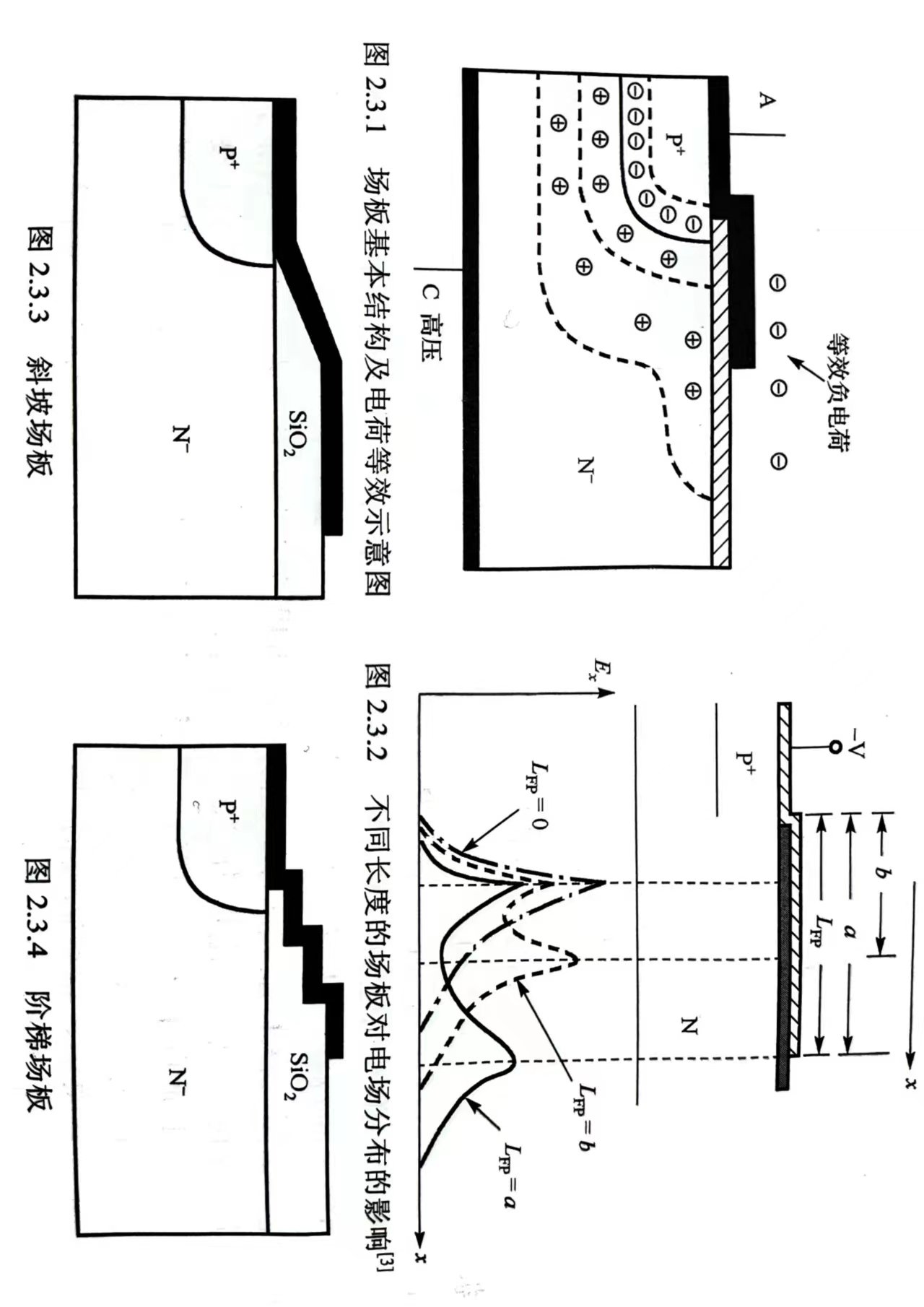

场板的作用是通过将一部分原本由N耗尽区正电荷指向表面出P+耗尽区负电荷的电场线转向场板,从而降低主结处的电场峰值,缓解电场集中的现象,同时展宽耗尽区,如图.1虚线所示。这种作用可以等效在半导体表面之上增加了一层负电荷,N区正电荷发出电力线部分终止于表面的负电荷,保证电通量不变。这些负电荷会产生垂直于硅层表面的电场以及平行于半导体表面两个方向的电场。在场板下方多数区域内,这些负电荷产生的横向电场相互抵消;在场板靠近主结的位置,该电场削弱原来的主结电场峰值。但在场板末端,横向电场于来源于主结的电场相互加强,产生一个额外的电场峰。

场板的作用通常由场氧厚度和场板的长度决定。厚则削弱其降低主结峰场作用;薄则因场板末端新的电场尖峰而发生击穿。

图.2给出在相同的反偏电压下,具有不同场板长度的PN结的表面电场分布,场板越场,峰值越小。实际应用,需要合理设计。

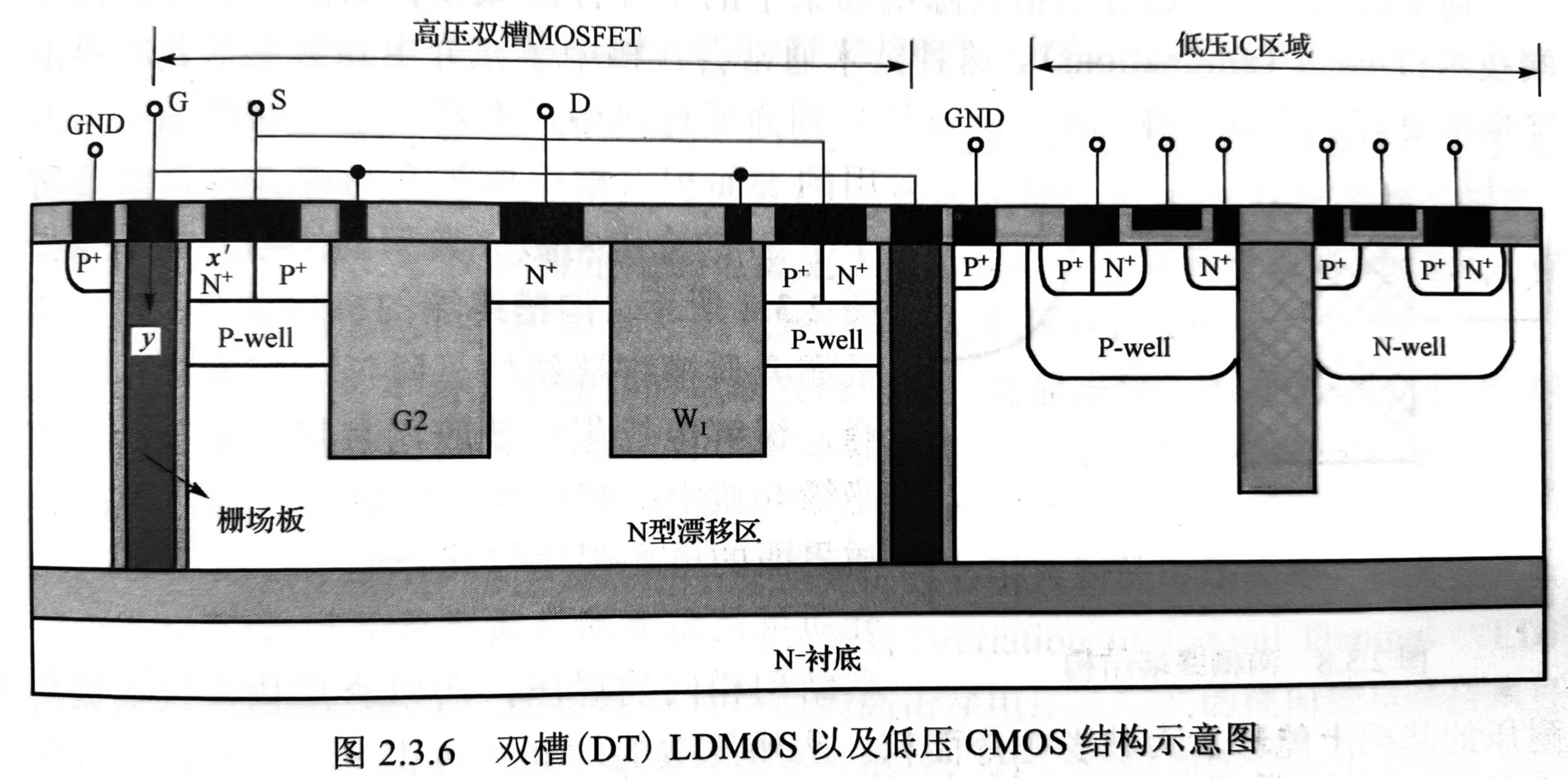

场板下横向电场分量随距离按如下指数规律下降:Ex∝exp(-0.6x/tfox),其中tfox是场氧化层厚度,x轴的原点在主结面,其正方向为沿表面远离主结的方向。如果tfox随x的增加而增加,场板上的横向电场分布会更趋于均匀,这种场板称为斜坡场板,如图.3所示。

斜坡场板或能花费更小的终端面积获得缓解表面的尖峰电场。然斜坡场板的工艺实现相对困难,折中方案是图.4所示的阶梯场板。

在常规平面LDMOS中,阻断状态下只有处于低电位的栅场板或者源场板才具有对N型漂移区的辅助耗尽作用。

漏场板由于连接最高电位,不具有对N型漂移区的辅助耗尽作用。平面结构中,场板只能产生局部耗尽作用。

若要扩展场板的耗尽区域,只能水平延申场板长度,然而缩短栅场板与漏场板的距离对器件的耐压有较大影响。

采用纵向场板结构,使场板成为从表面延伸至体内的负电荷中心,在漂移区内产生横向附加电场,使得部分电力线横向终止于场板。

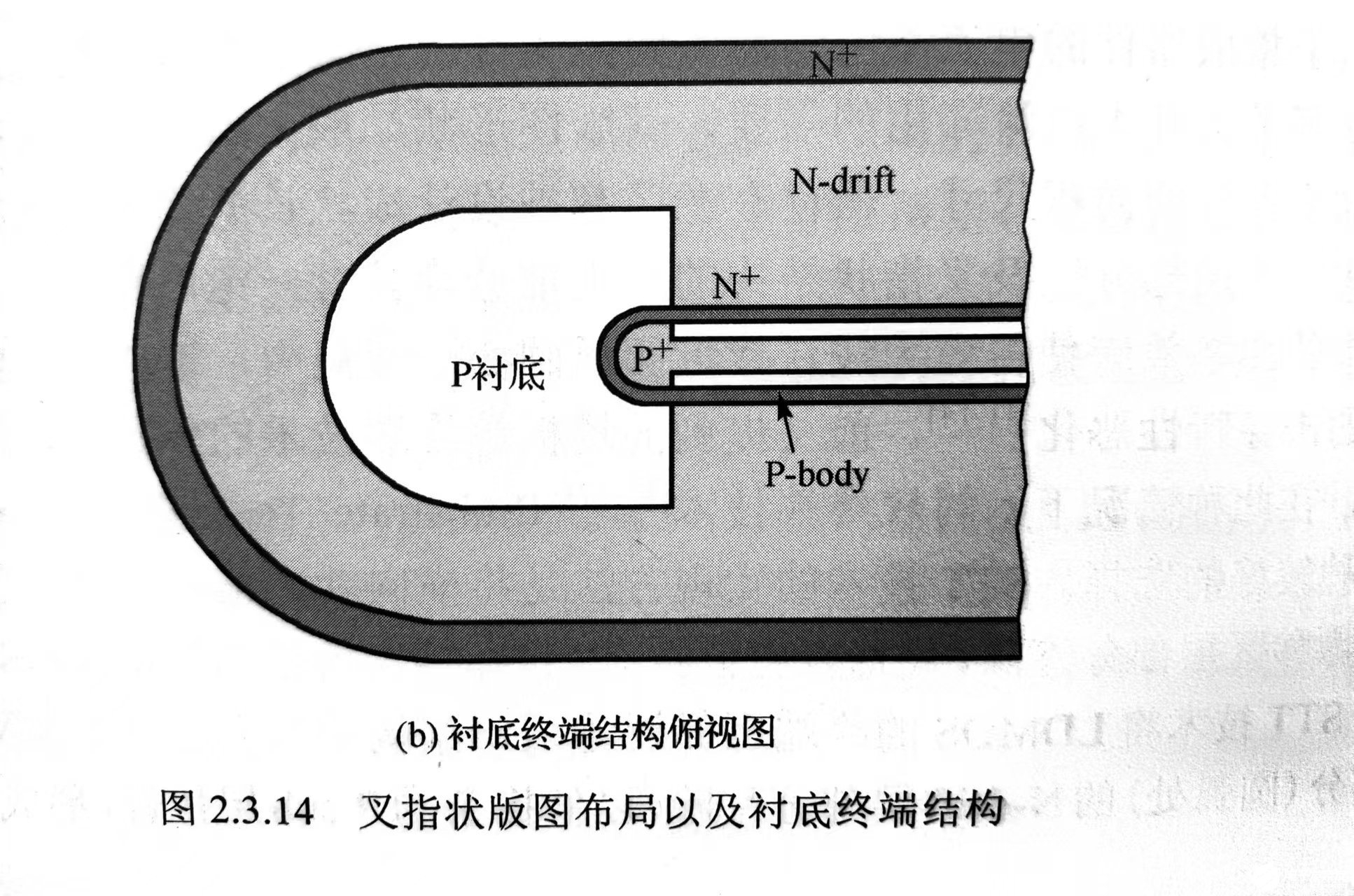

图.6给出一种带有双槽的横向功率MOSFET器件,其采用了隔离型纵向场板技术。

槽栅从表面延伸至埋氧层,形成纵向的MIS结构,在阻断状态下相当于纵向场板,缓解了P-well处的电场集中,且形成多维度辅助耗尽,提高漂移区的优化浓度。通过在漂移区内引入介质槽,等效折叠漂移区,相同尺寸下提高击穿电压。

此外,纵向栅场板在阻断状态能有效屏蔽来自高压区的电力线,起到隔离的效果。

.2沟槽终端技术(Trench Terminations)

(上文提及的介质槽)刻槽能去除电场集中的半导体区域以提高耐压,即沟槽终端技术。这种技术通常会在槽中填充介电系数更低且临界击穿电场更高的介质材料。(所填介质的介电常数通常小于Si的介电常数。)

将高电场转移到介质材料中,有利于缩小结终端结构占用的表面积。

沟槽终端机理:

1.主结紧靠介质槽终端结构,降低了结面处电场尖峰,缓解电场集中效应,将高电场转移到绝缘介质中。

2.根据高斯定理,垂直于硅介质界面的电场强度与其介电系数成正比,低K介质可使更窄的介质槽承受于较宽Si平面终端结构相同的耐压,所以介质槽终端在提高耐压的基础上能大大节省芯片面积。(性能由槽宽、槽深、及介质k值决定,也就是说耐高压的配置是槽窄,槽深,高k值)。

.3结终端扩展技术(Junction Termination Extension,JTE)

结终端扩展技术是在主结边缘的轻掺杂侧再掺杂,即引入附加电荷。其机理在于通过优化漂移区的表面电场分布,从而提高器件击穿电压。

.4衬底终端技术(Substrate Termination Technology,STT)

集成器件的电流流向均为横向,器件的电流能力和面积息息相关。

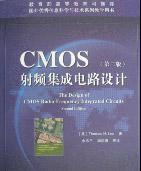

基于横向功率开关器件大电流应用的需要,版图一般为跑道形或叉指状结构;为了缩小器件的面积尺寸,器件有源区都被设计成狭长的细条形结构,因此再跑道结构的弯道部分以及叉指状结构的指尖部分都具有一定曲率半径。

圆弧形结构带来的曲率效应使得电力线在接近圆弧圆心一端集中,造成极大的峰值电场,使得器件的击穿特性恶化。(前面提到的技术不能有效解决此问题)

STT技术可以,其实现方法是将横向功率器件的终端区靠近曲率圆心处的漂移区层部分移除,代替以更低掺杂的异质层。

就横向功率MOSFET器件而言,通过STT技术将LDMOS的终端区靠近跑道结构的弯道部分以及叉指状结构的指尖部分(圆弧处)的N-drift层部分移除,代替以低掺杂的P-sub层代替,形成了一个由P-sub层和N-drift漂移区组成的耐压结构。

该变化使得高掺杂的P-body/N-drift结的曲率半径增加,从而改善器件的击穿电压。从工艺角度来看,这种方法不需要增加额外的掩膜版次,也不占用大面积区域。不过引入之后,一定程度牺牲了正向电流能力。

审核编辑:黄飞

-

集成电路

+关注

关注

5389文章

11567浏览量

362163 -

MOSFET

+关注

关注

147文章

7192浏览量

213559 -

功率器件

+关注

关注

41文章

1773浏览量

90493 -

LDMOS

+关注

关注

2文章

77浏览量

25287 -

开关器件

+关注

关注

1文章

191浏览量

16894

发布评论请先 登录

相关推荐

功率集成电路设计之结终端技术

功率集成电路设计之结终端技术

评论