1 简介

锁相环是一种 反馈系统 ,其中电压控制振荡器和相位比较器相互连接,使得振荡器频率(相位)可以准确跟踪施加的频率或相位调制信号的频率。锁相环可用来从固定的低频信号生成稳定的输出频率信号。首批锁相环由法国工程师De Bellescize 在20世纪30年代初实现。然而,直到20世纪60年代中期,集成式PLL成为一种成本相对较低的元件之后,锁相环才得到市场的广泛认可。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

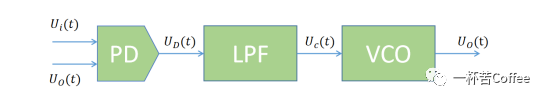

2 锁相环基本组成

锁相环一般由 鉴相器(PD) 、 环路滤波器(LPF) 、 电压控制振荡器(VCO )组成。其功能如下:

- 鉴相器 :又称为相位比较器,其主要功能是检测输入信号和输出信号的相位差,并将检测的相位差转换为电压信号。

- 环路滤波器 :主要功能是滤除鉴相器输出的高频分量。

- 电压控制振荡器:根据鉴相器产生的信号,对输出信号的频率和相位进行调整。

3 锁相环基本原理

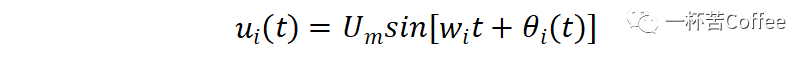

锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器。外部输入的信号分为:

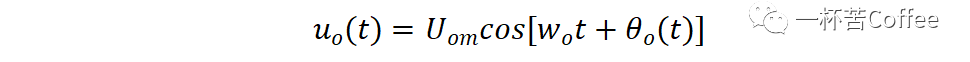

电压控制振荡器的输出信号为:

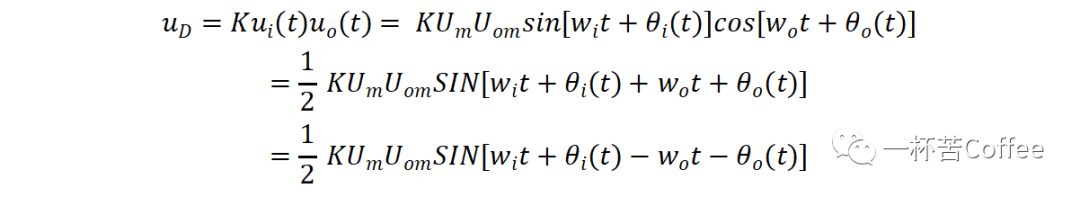

其中,ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。则模拟乘法器的输出电压为:

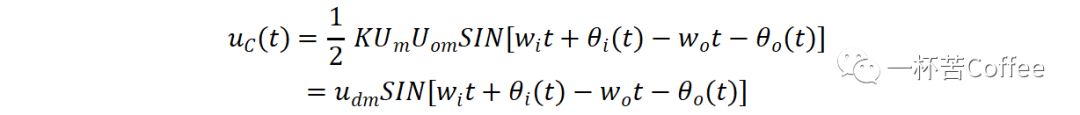

使用LPF将上式中的高频分两级滤除,剩下低频分量作为电压控制振荡器的输入控制电压,则

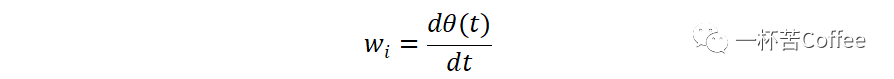

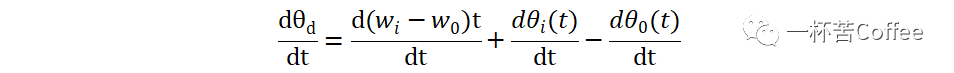

式中的为输入信号的瞬时振荡角频率,和分别为输入信号和输出信号的瞬时相位,根据相量的关系可得瞬时频率和瞬时相位的关系为:

那么,

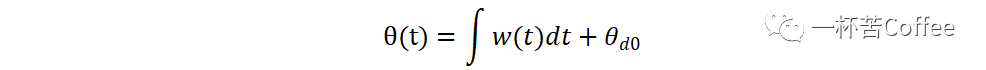

瞬时相位为:

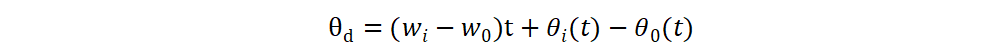

对两边同时积分,可得频差的关系为:

上式等于零,说明锁相环进入相位锁定的状态,此时输出和输入信号的频率和相位保持恒定不变的状态,为恒定值。当上式不等于零时,说明锁相环的相位还未锁定,输入信号和输出信号的频率不等,随时间而变。

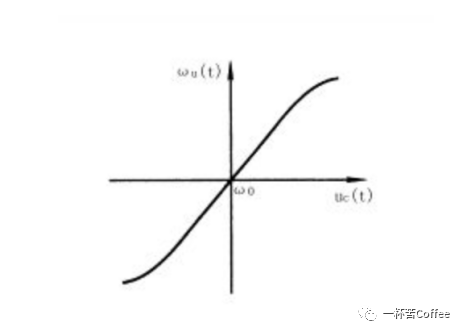

因压控振荡器的压控特性如图8-4-3所示,该特性说明压控振荡器的振荡频率ωu以ω0为中心,随输入信号电压的变化而变化。该特性的表达式为

上式说明当uc(t)随时间而变时,压控振荡器的振荡频率ωu也随时间而变,锁相环进入“频率牵引”,自动跟踪捕捉输入信号的频率,使锁相环进入锁定的状态,并保持ω0=ωi的状态不变。

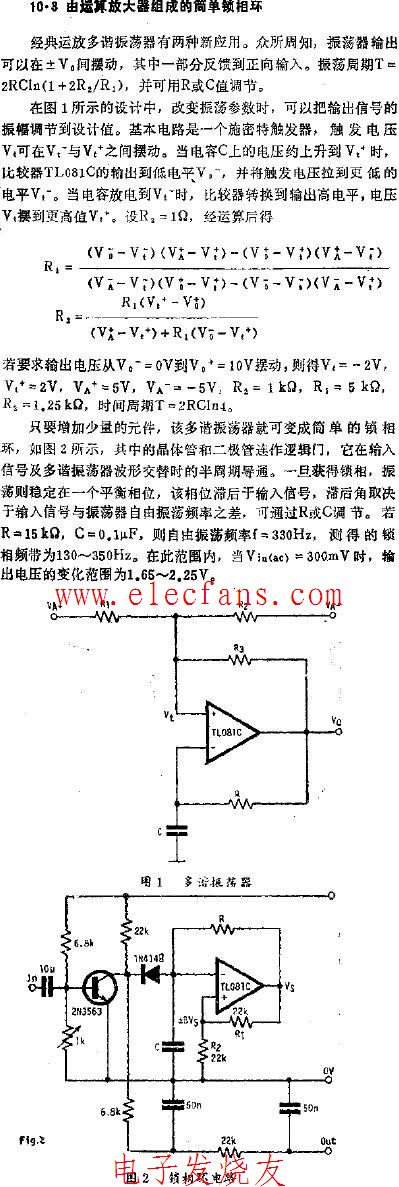

4 锁相环的电路设计

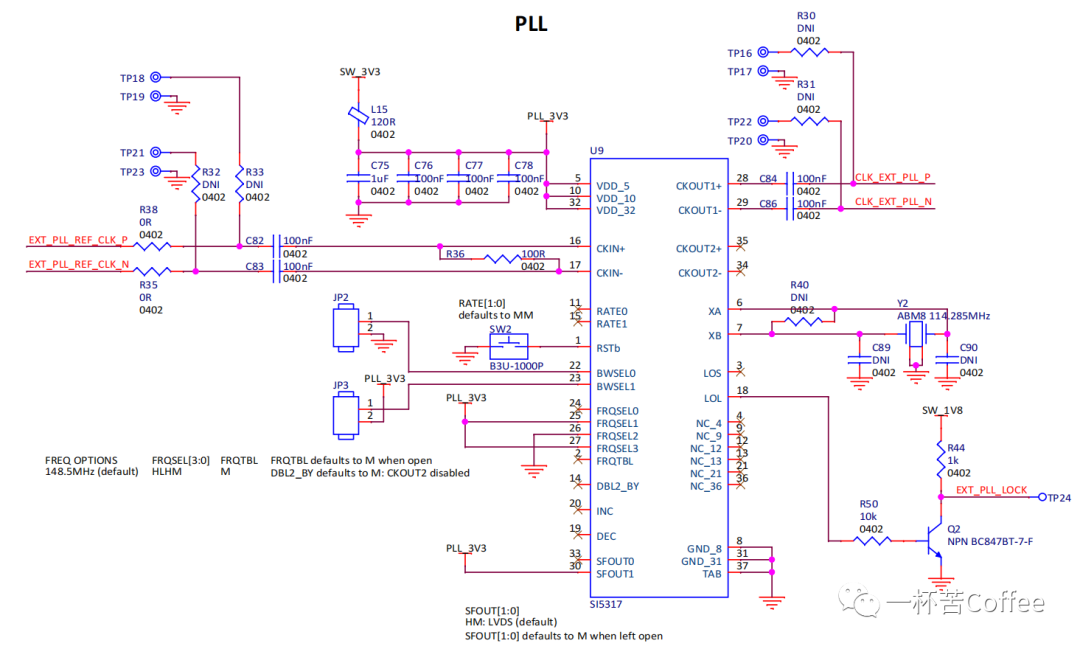

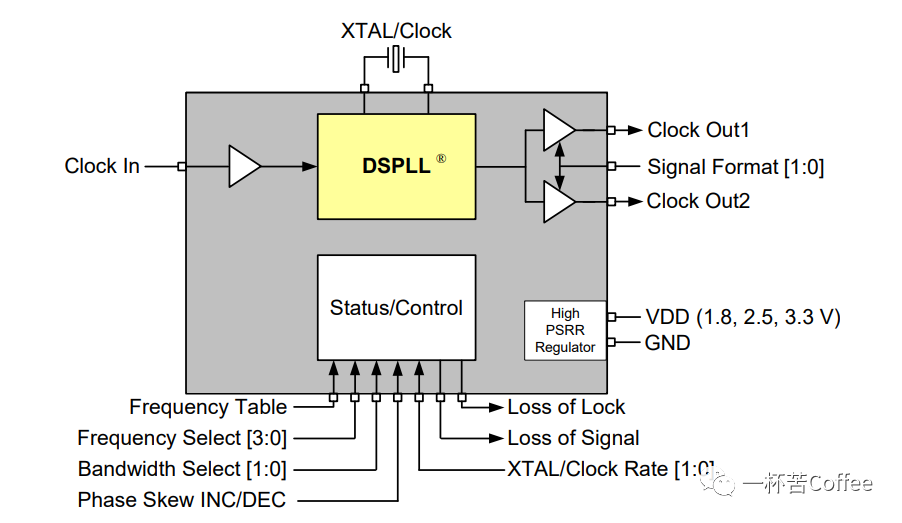

SI5317D-C-GM采用单电源供电,供电电压支持 1.8V、2.5V、3.3V 。输入/输出频率范围: 1-711MHz 。

其内部功能框图见下:

可见,支持单时钟输入,两个输出时钟。

5 锁相环的应用

锁相环在调制和解调中的应用

为了实现信息的远距离传输,在发信端通常采用调制的方法对信号进行调制,收信端接收到信号后必须进行解调才能恢复原信号。

所谓的调制就是用携带信息的输入信号ui来控制载波信号uc的参数,使载波信号的某一个参数随输入信号的变化而变化。载波信号的参数有幅度、频率和位相,所以,调制有调幅(AM)、调频(FM)和调相(PM)三种。

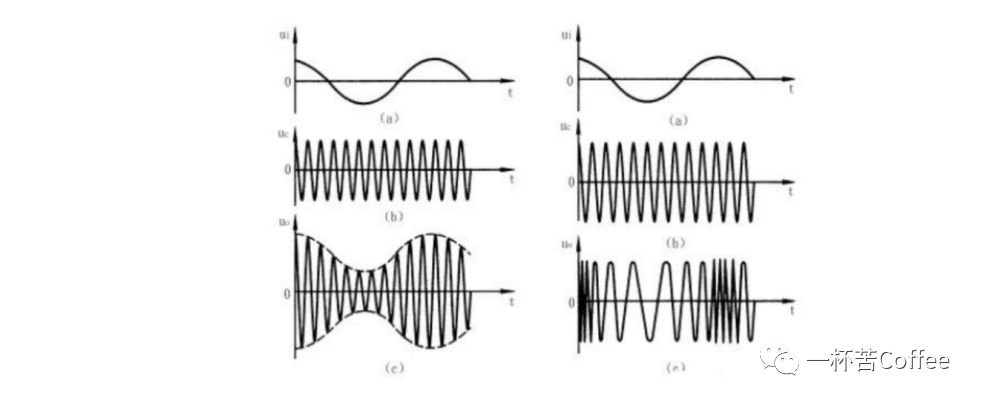

调幅波的特点是频率与载波信号的频率相等,幅度随输入信号幅度的变化而变化;调频波的特点是幅度与载波信号的幅度相等,频率随输入信号幅度的变化而变化;调相波的特点是幅度与载波信号的幅度相等,相位随输入信号幅度的变化而变化。调幅波和调频波的示意图如图所示:

上图的(a)是输入信号,又称为调制信号;图(b)是载波信号,图(c)是调幅波和调频波信号。

注意 :解调是调制的逆过程,它可将调制波uo还原成原信号ui。

锁相环在调频和解调电路中的应用

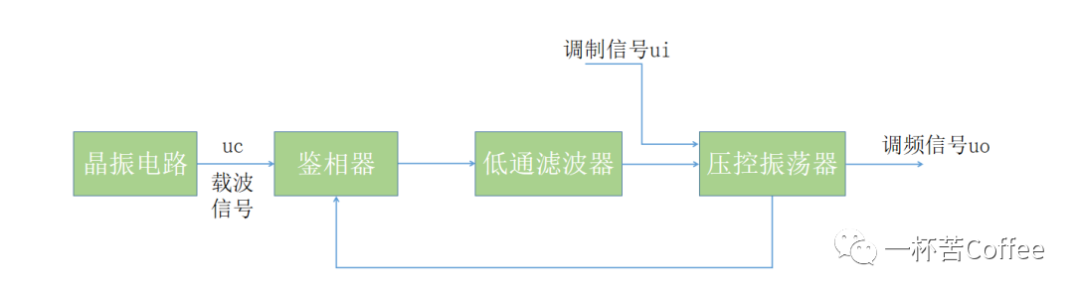

调频波的特点是频率随调制信号幅度的变化而变化。由图可知,压控振荡器的振荡频率取决于输入电压的幅度。当载波信号的频率与锁相环的固有振荡频率ω0相等时,压控振荡器输出信号的频率将保持ω0不变。若压控振荡器的输入信号除了有锁相环低通滤波器输出的信号uc外,还有调制信号ui,则压控振荡器输出信号的频率就是以ω0为中心,随调制信号幅度的变化而变化的调频波信号。由此可得调频电路可利用锁相环来组成,由锁相环组成的调频电路组成框图如图所示:

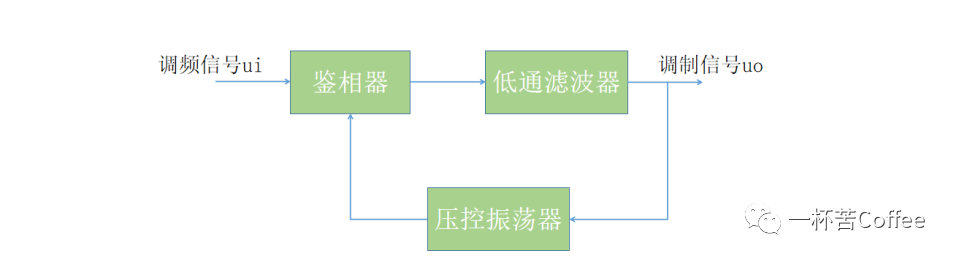

若输入FM信号时,让环路通带足够宽,使信号调制频谱落在带宽之内,这时压控振荡器的频率跟踪输入调制的变化,如图6.1所示。对于锁相环的详细分析可参阅有关锁相技术的书籍。在此仅说明锁相环鉴频原理。可以简单地认为压控振荡器频率与输入信号频率之间的跟踪误差可以忽略。因此任何瞬时,压控振荡器的频率ωv(t)与FM波的瞬时频率ωFM(t)相等。

锁相环在频率合成电路中的应用

在现代电子技术中,为了得到高精度的振荡频率,通常采用石英晶体振荡器。但石英晶体振荡器的频率不容易改变,利用锁相环、倍频、分频等频率合成技术,可以获得多频率、高稳定的振荡信号输出。

输出信号频率比晶振信号频率大的称为锁相倍频器电路;输出信号频率比晶振信号频率小的称为锁相分频器电路。锁相倍频和锁相分频电路的组成框图如图所示:

图中的N大于1时,为分频电路;N小于1时,为倍频电路。

-

锁相环

+关注

关注

36文章

637浏览量

91307 -

振荡器

+关注

关注

28文章

4195浏览量

143186 -

电路设计

+关注

关注

6746文章

2800浏览量

220324 -

比较器

+关注

关注

14文章

1936浏览量

112105 -

pll

+关注

关注

6文章

991浏览量

138395

发布评论请先 登录

求助:锁相环(PLL)电路设计与应用; 日本人写的

【下载】《锁相环电路设计与应用》

电荷泵锁相环电路锁定检测的基本原理,影响锁相环数字锁定电路的关键因子是什么?

基于0.25um CMOS工艺的锁相环电路设计

锁相环(PLL)电路设计与应用

硬件电路设计之锁相环电路设计

硬件电路设计之锁相环电路设计

评论