1芯片生产及缺陷介绍

1.1芯片制造流程

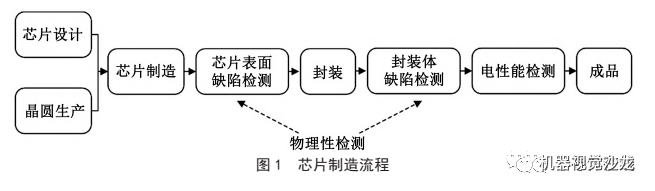

芯片生产需要经历数道工序,其中各工艺流程环环相扣。芯片生产对材料、环境、工艺参数等敏感,每个环节都有可能产生缺陷。因此,了解制造工艺流程,是进行芯片表面缺陷检测研究的前提。芯片生产线主要包括芯片设计、制造、封装和检测 4 大环节,流程如图 1 所示。

芯片检测主要分为物理性检测和电性能检测。物理性检测主要可分为封装前的芯片表面缺陷检测和封装后的封装体缺陷检测。电性能检测是在不同的电压、温度和湿度等条件下进行温度、电气和速度测试,目的是检测芯片的性能是否达标。本研究主要聚焦于半导体芯片的物理性缺陷检测。

1.2芯片缺陷介绍

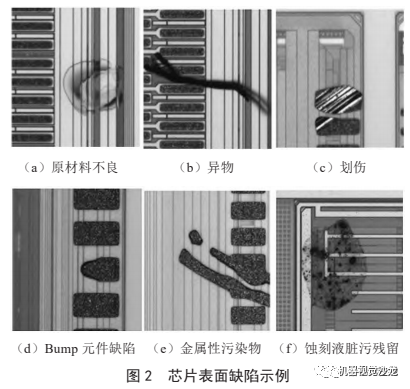

封装前,上述数道工艺的操作控制、工艺参数、环境等因素都会对芯片质量产生一定的影响,产生的缺陷表现出类别多样、形态各异、背景复杂等特点。芯片制造过程中产生的表面缺陷示例如图 2 所示,大致可划分为原材料不良、异物、划伤、Bump 元件缺陷(凸起、错位或缺失)、金属性污染物和蚀刻液脏污残留。此外,芯片制造过程中还会产生如蚀刻锈斑、电镀过多、异色和金属线损坏等小样本缺陷。

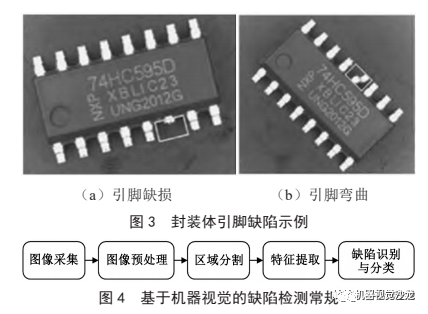

封装后的封装体缺陷包括印刷缺陷和引脚缺陷。封装体表面印刷符号表明了其名称、规格、型号和性能等信息,是辨识芯片的重要依据。清晰的符号是高质量芯片的内在需求。实际生产中常存在的印刷缺陷包括错字、偏移、漏印、多印、模糊、倾斜、位移、断字、双层印和无字等。引脚缺陷包括引脚缺失、引脚破损和引脚弯曲等。缺陷示例如图 3 所示。

2芯片缺陷检测方法

2.1机器视觉缺陷检测方法

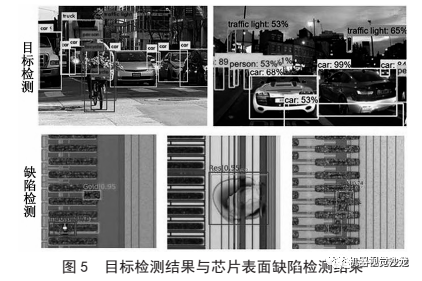

机器视觉方法基本检测流程,如图 4 所示。随着机器视觉相关技术逐渐受到重视,多种基于人工设计特征的特征选择算法和模式识别分类算法被应用于表面缺陷检测领域。

2.1.1芯片表面缺陷检测

针对封装前的芯片表面缺陷检测,戴敬等通过改进多重中值滤波算法,采用插影法、归一化互相关的模板匹配等方法实现晶圆表面缺陷检测。SU 等通过对封装芯片的表面施加超声波激发并结合测振仪提取了时域和频域特征,引入遗传算法进行特征选择,最后采用 BP(Back Propagation)神经网络进行分类识别。陈凯提取集成电路芯片表面的几何特征、纹理特征和灰度特征缺陷特征,在特征降维后输入基于改进的萤火虫算法的支持向量机实现缺陷识别。付纯鹤等提取芯片表面缺陷的 Hu 不变矩特征和局部二值模式(Local Binary Pattern,LBP)特征,通过反向传播神经网络(Back Propagation Neural Network,BPNN)进行学习,最后采用最近邻算法分类缺陷。

2.1.2封装体缺陷检测

针对封装后的封装体存在的印刷缺陷,张静平提出了一种动态缩小图像检测区域的加权模板匹配算法,以判断 QFN 芯片表面字符的缺陷。FABIO 等结合卷积神经网络、k 均值聚类算法和 k 近邻分类算法,识别食品包装盒上的符号模糊和符号缺失,对芯片封装体存在的印刷缺陷检测具有参考意义 。

针对封装后的封装体存在的引脚缺陷,巢渊提取缺陷的几何、灰度、纹理特征,提出基于广义反向粒子群与引力搜索混合算法和高斯核支持向量机 RBFSVM 分类缺陷。刘琛等提出一种基于方位环境特征的点模式匹配定位算法,快速准确定位芯片并识别引脚缺陷。陈文凤等设计了一套基于 ARM-DSP 双核结构的集成芯片引脚缺陷自动检测系统。

为检测 SOP 芯片引脚缺陷,李本红等采用灰度跃变检测引脚中点、中点直线拟合和引脚间距统计等方法,实现对 SOP 芯片引脚缺陷的自动检测 ;李绎铃以连通像素区域标记法为主要算法,提出基于模板匹配的引脚缺陷识别算法 ;金贺楠通过图像矩来对SOP 芯片的整体位置进行定位,同时结合基于 TwoPass 的连通域分方法来完善芯片引脚外观检测 。

以上特征提取结合分类器的方法可以较好地实现缺陷检测,但同时特征提取存在主观性、局限性问题和复杂化问题等,需要依赖经验和专业知识,有针对性地依据产品表面缺陷特性提取和选择特征。随着芯片愈加集成化和光刻工艺愈加复杂,产生的缺陷往往类型繁多、特征复杂、背景多变和位置随机,传统的机器视觉技术难以充分且有效地提取到缺陷特征,效率低下,已难堪重任。

2.2深度学习缺陷检测方法

近年来,以卷积神经网络为代表的深度学习模型在计算机视觉领域成功应用,给表面缺陷检测带来了新的启发。不少学者将目标检测相关算法应用于各种工业场景的表面缺陷检测。

对缺陷模式认知的不同,深度学习模型可以划分为有监督学习、无监督学习和弱监督半监督等。有监督检测方法体现在利用标记了标签(包括类别、矩形框或逐像素等)的缺陷图像输入到网络中进行训练,更关注缺陷特征。无监督检测方法通常只需要正常无缺陷样本进行网络训练,更关注正常样本特征。

2.2.1有监督方法

(1)芯片表面缺陷检测。针对封装前的芯片表面缺陷检测,周小萌将经典的卷积神经网络 Alexnet应用于识别 IC 芯片外观缺陷。李明将卷积神经网络和类激活映射技术相结合,提出 Laser Chip Net 网络来实现激光芯片缺陷分类识别和缺陷区域定位。

DING 等引入多尺度金字塔网络改进 Faster R-CNN的骨干卷积网络,用于检测 PCB 表面缺陷 。周天宇等提出了一种轻量级卷积神经网络算法 YOLOEfficientnet,应用于载波芯片 COC 缺陷检测 。CHEN 等将生成对抗网络 GAN 与 YOLOv3 算法结合,应用于芯片晶粒的表面缺陷检测。

对 于 LED 芯片的缺陷检测问题:LIN 等提出LEDNet,采用了一种类激活映射技术来定位 LED 芯片缺陷(线瑕疵和划痕)区域 ;刘志提出了 ATSSD,采用深度残差网络 ResNet 作为主干卷积网络,并引入注意力机制和多尺度特征融合方法提取特征,提升了检测精度。

(2)封装体缺陷检测。针对封装后的封装体存在的印刷缺陷和引脚缺陷,唐铭豆等通过选定连通区域和分割算法定位字符,采用改进的 CNN 进行字符识别,最终实现芯片印刷标识检测 。郭晓峰等利用最小外接圆原理定位和校正图像,随后对 ROI 区域进行字符分割,最后进行差分识别。肖磊基于 AlexNet改进得到一种对压敏电阻外观细微缺陷敏感的卷积神经网络模型(CNN4VDR),用于识别压敏电阻主体和针脚的外观缺陷 。

2.2.2无监督方法

有监督学习模型需要大量人工标记数据,但是在工业生产中,部分类型缺陷发生概率低,样本数量少,小样本训练网络模型会导致过拟合问题。此外,还经常生成不可预知的缺陷,难以及时标记。无监督学习方法只需要正常无缺陷样本进行网络训练,具备强大的正常样本分布重建和判别能力,在近年逐渐受到关注。

CHANG 等提出了一种基于自组织神经网络(Self-Organizing Neural Networks,SONN)的晶圆自动检测系统,利用 SONN 的无监督自动聚类的能力,识别晶圆上的缺陷区域 。GHOSH 等提出了一种基于 CNN 的有监督技术和两种基于深度图和引脚纹理的无监督技术,以识别弯曲和腐蚀的芯片引脚缺陷 。罗月童等提出了基于卷积去噪自编码器的芯片表面弱缺陷检测方法。MEI 等提出了一种利用不同高斯金字塔等级的卷积去噪自编码器网络重构图像,使用重构残差图进行缺陷检测。

2.3其他方法

弱监督的方法是指采用图像级别类别标注(弱标签)来获取分割 / 定位级别的检测效果。半监督学习通常会使用大量的未标记数据和少部分有标签的数据,用于表面缺陷检测模型的训练。相对于全监督和无监督方法,虽然目前弱监督和半监督方法在表面缺陷检测中的应用相对较少,但仍具有参考价值。

MARINO 等采用一种基于 PRM 弱监督学习方法来对马铃薯表面缺陷进行分类、定位和分割。ZHAO 等提出一种基于 GAN 的弱监督学习缺陷检测方法,通过 CycleGAN 实现表面缺陷检测 。YU 等提出了一种多重训练的半监督学习方法应用于钢表面缺陷分类,利用 cDCGAN 和 ResNet-18 的多训练融合算法用于未标记样本的类别标签预测及训练。

此外,还有其他方法。例如 :万乃嘉设计了基于领域自适应的芯片字符识别系统 ;饶永明等提出了面向芯片表面符号的结构缺陷的评估方法;主动红外热成像技术被应用于微焊球缺陷检测 和倒装芯片缺陷检测 ;空气耦合超声激励应用于倒装芯片(Flip Chip,FC)缺陷检测 。

3芯片表面缺陷特性分析

当前表面缺陷检测中应用的算法与通用目标检测算法异曲同工,即视表面缺陷为普通目标,忽视了表面缺陷与普通目标之间的差异。下面将对比表面缺陷与普通目标,分析发现表面缺陷存在如下特性。

3.1缺陷与缺陷之间的互斥性

在 目标检测中,同类或是异类目标之间相互交叠的现象非常常见。如何检测相互交叠的目标是目标检测的重难点。如图 5 所示,目标检测结果中“car”“person”“bicycle”目标相互交叠。然而,表面缺陷之间相互交叠的情况并不存在,在某一个位置上有且只有一个缺陷。因此,缺陷检测应该有且只能有一个结果。如图 5 所示,缺陷检测结果中标注框即是冗余结果。

3.2缺陷与缺陷之间存在重要性差异

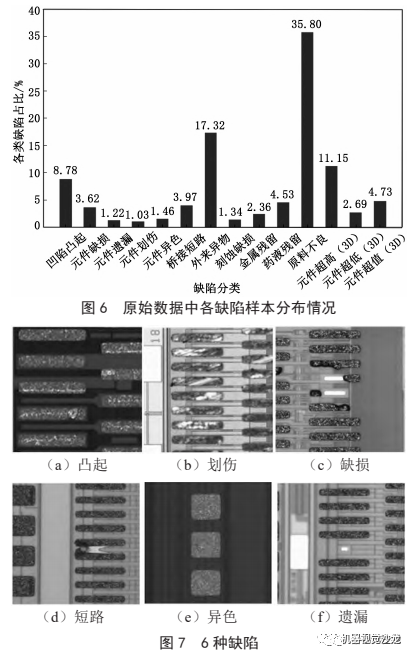

在通用目标检测中,所有目标都是平等的,然而表面缺陷之间存在重要性差异。本研究通过电子显微镜采集了 25 种类别共 181 590 张半导体芯片表面缺陷图像,通过数学统计方法分析发现,其中 14 个类别缺陷样本为主要成分,共 178 953 个样本,占比 98.53%,样本分布如图 6 所示。各类缺陷样本占比各不相同,意味着各类缺陷的发生概率各不相同,即存在着重要性差异,因此表面缺陷检测应合理考虑其差异性。

芯片表面的缺陷并不是孤立存在的,其产生必然会与周围环境相互作用,存在关联性。图 7 展示的 6 种缺陷虽然特征完全不相同,但是存在一个共性,即均与Bump 元件相关。图 7(a)是 Bump 元件上的局部凸起;图 7(b)是 Bump 元件上的划痕 ;图 7(c)是 Bump 元件残缺;图 7(d)是金属物质异常滴漏在 Bump 元件之间,桥接引起短路;图 7(e)是 Bump 元件局部表面颜色异常;图 7(f)是 Bump 元件的漏焊,其具体形态特征可以参考周围 Bump 元件。在分类任务中,Bump 元件可以帮助限定缺陷类别的范围 ;在定位任务中,Bump 元件的位置可以辅助定位回归。

虽然表面缺陷检测技术已经不断从学术研究走向成熟的工业应用,但是依然有一些需要解决的问题。基于以上分析可以发现,由于芯片表面缺陷的独特性质,通用目标检测算法不适合直接应用于芯片表面缺陷检测任务,需要提出新的解决方法。

4结语

对近年来基于传统的机器视觉和基于深度学习的芯片缺陷检测方法进行梳理与分析,介绍对封装前的芯片表面缺陷和封装体存在的印刷缺陷与引脚缺陷检测的相关研究,详细分析了芯片表面缺陷特性,以期为相关研究人员提供参考。

审核编辑:刘清

-

编码器

+关注

关注

45文章

3646浏览量

134687 -

机器视觉

+关注

关注

162文章

4380浏览量

120408 -

GaN

+关注

关注

19文章

1943浏览量

73597 -

半导体芯片

+关注

关注

60文章

919浏览量

70655 -

深度学习

+关注

关注

73文章

5504浏览量

121246

原文标题:【光电智造】芯片缺陷检测综述

文章出处:【微信号:今日光电,微信公众号:今日光电】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

缺陷检测在工业生产中的应用

机器视觉表面缺陷检测技术

[转]产品表面缺陷检测

芯片缺陷检测

表面检测市场案例,SMT缺陷检测

基于LED芯片封装缺陷检测方法研究

机器视觉检测中的外观缺陷检测

基于深度学习的芯片缺陷检测梳理分析

芯片缺陷是什么?芯片缺陷检测做什么?芯片缺陷检测怎么做?

芯片缺陷是什么?芯片缺陷检测做什么?芯片缺陷检测怎么做?

评论