在设计周期中,您可保留多个版本的工程,这些工程使用相同的 IP 和相同的配置。重新运行整个工程会导致每次都要重新生成 IP,很费时间。

在 Vivado工程设置中,您的 IP 存储库允许您将自己的 IP 添加到 Vivado IP 目录中,搭配远程 IP 高速缓存一起使用时,即可显著缩短编译时间。这篇博文解释了具体设置方法。

要求:

在阅读本设计输入之前,请确保您熟悉如何封装 IP 核。如需了解相关信息,请参阅 UG1118 和 QuickTake 视频。

在开始下述步骤前,最好先创建格式化目录结构:

注释:此结构中应有一个顶层的父目录,例如,iprepo,然后是子目录;每个 IP 一个子目录,还有一个子目录对应由 Vivado 创建的远程 IP 高速缓存。

此 IP 必须位于远程 IP 高速缓存的同级目录内。这是因为 Vivado 遇到 component.xml 文件时,就会停止搜索 IP 高速缓存的目录结构,而此文件始终与封装的 IP 目录一起生成。

第 1 步:将所有必需的源文件封装为单个 IP

一般,IP 封装步骤包括以下 3 个步骤,并且封装的 IP 文件一起接受管理。

1. 将 RTL 添加到 Vivado 工程中,并对其进行综合,验证其完整性 。

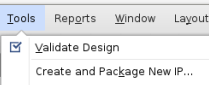

2. 使用 Vivado 中的“Tools”(工具)选项对 RTL 进行封装:

3. 确保基于 ip_repo 目录中的 IP 名称选择一个目录。

第 2 步:验证并生成所有远程高速缓存文件

在这一步中,您需要从已封装的 IP 文件夹中例化已封装的 IP,但不含任何逻辑连接。随后,为存储库中的不同 IP 配置生成网表。

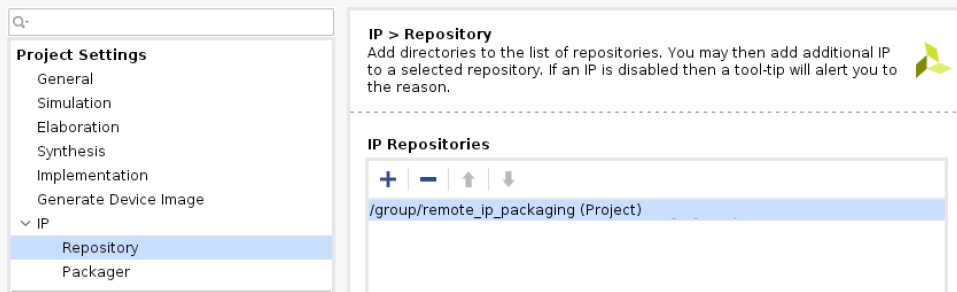

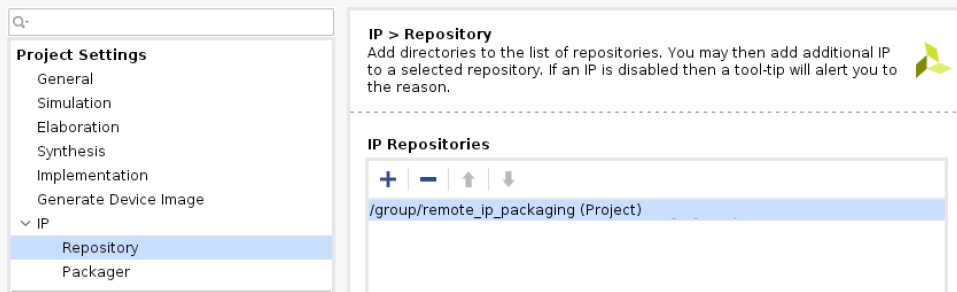

1. 通过工程设置将新创建的用户 IP 存储库添加到 Vivado 工程中:

2. 将该 IP 添加到新创建的 IP integrator 块设计中。 您可选中 IP 并按下 Ctrl-T 键,轻松将此 IP 的所有端口连接到外部端口。或者,您可将其添加到设计中。

3. 如果您的 IP 可配置,请添加多项配置,以便在 IP 高速缓存中填充更多通用配置。

注释:应用此变通方法时存在诸多限制,只要与用户 IP 设置存在任何不匹配,都可能导致重新生成已例化的 IP。

请确保软件构建相匹配

请确保 device part/speed_grade/board name 相匹配

确保 IP 设置与生成此 IP 时的 IP 缓存文件相匹配。鉴于有时参数传播可能导致覆盖用户 IP 上的部分参数,例如,从上游传播的时钟频率会被覆盖,因此应执行检查。

4. 确认设计并审查任何“Error”(错误)和“Critical Warning”(严重警告)

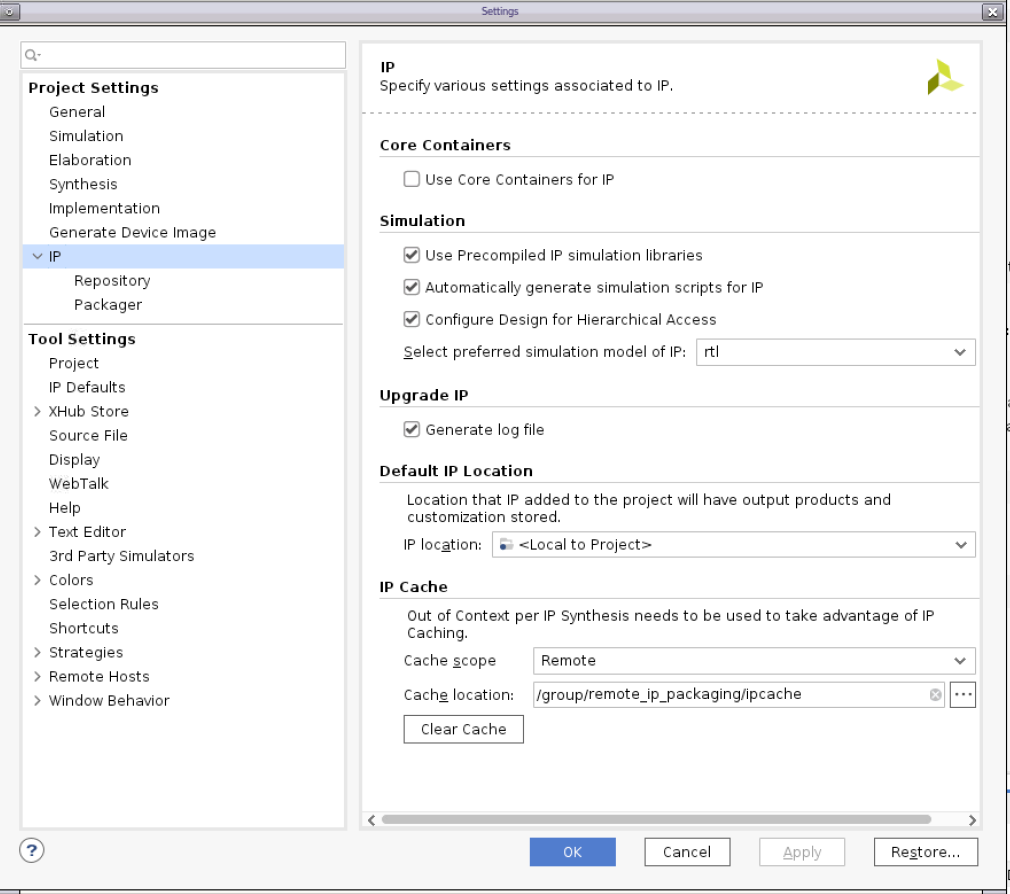

5. 生成设计之前,在 IP Repository 目录下指定远程 IP 存储库,例如,/iprepo/ipcache:

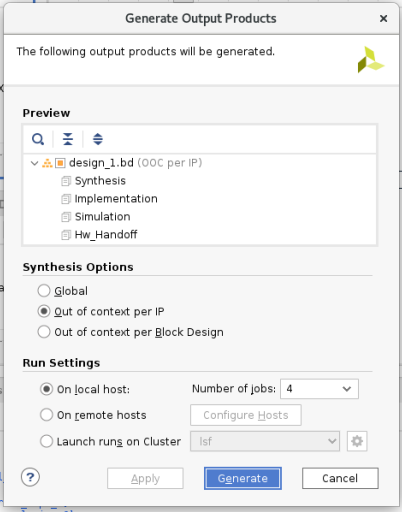

6. 使用默认“Out of context per IP”(非关联按 IP)选项生成块设计:

7. 生成完成后,应显示已填充的远程 IP 高速缓存。

其中将生成新的目录,并以散列代码作为目录名称。

第 3 步:在正式设计中例化 IP,并复用远程 IP 存储库

在工程中使用用户 IP 存储库和 IP 高速缓存:

1. 现在,您只需要指向顶层的 IP 存储库目录,即可同时使用用户 IP 和远程 IP 高速缓存。

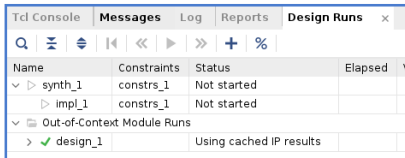

2. 生成设计时,如果使用的器件/开发板和 IP 配置选项未更改,就不会发生重新综合,并且 IP 运行状态将显示“Using cached IP results”(使用缓存的 IP 结果):

建议的版本管理:

请通过脚本封装用户 IP,或创建独立工程来封装 IP。

创建独立工程来例化包含所有不同配置的用户 IP,并生成此 IP,同时导出高速缓存。

在正式工程中采用此 IP,并遵循本文档中的指南进行操作。

审核编辑:汤梓红

-

高速缓存

+关注

关注

0文章

30浏览量

11046 -

编译

+关注

关注

0文章

652浏览量

32800 -

脚本

+关注

关注

1文章

387浏览量

14829 -

Vivado

+关注

关注

19文章

807浏览量

66312

原文标题:节省编译时间系列-为多个 Vivado™ 工程复用远程 IP 高速缓存

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

MRAM高速缓存的组成

高速缓存/海量缓存的设计实现

怎么利用异步FIFO和PLL结构来实现高速缓存?

怎样去实现一种基于DSP和ADC技术高速缓存和海量缓存?

高速缓存Cache介绍

高速缓存(Cache),高速缓存(Cache)原理是什么?

AN1600 - 在PIC32MZ器件上使用L1高速缓存

使用MPLAB Harmony v3基于PIC32MZ MCU在运行时使用高速缓存维护操作处理高速缓存一致性问题

为多个Vivado工程复用远程IP高速缓存

为多个Vivado工程复用远程IP高速缓存

评论