前面讲过电源的阻抗频率特性曲线,也提到了自谐振频率,明确了随频率变化阻抗的变化趋势。我突然有个疑问:电感的感值随着频率如何变化呢?于是就有了今天要讨论的内容。

两个问题

照例,先抛出来2个问题:

问题1:电感的阻抗会随着频率发生变化,那电感的感值随着频率如何变化呢?

问题2:开关电源中电感选型时为什么自谐振频率要大于10倍开关频率?

注意这里说的是问题,而不会之前经常讲的面试题。因为在面试中不太会问这个点,但是这个问题涉及电感器件应用的基本面,有必要单独拎出来讨论下。

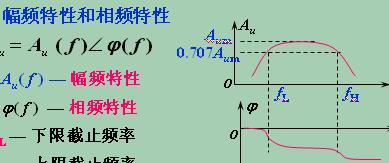

阻抗频率特性

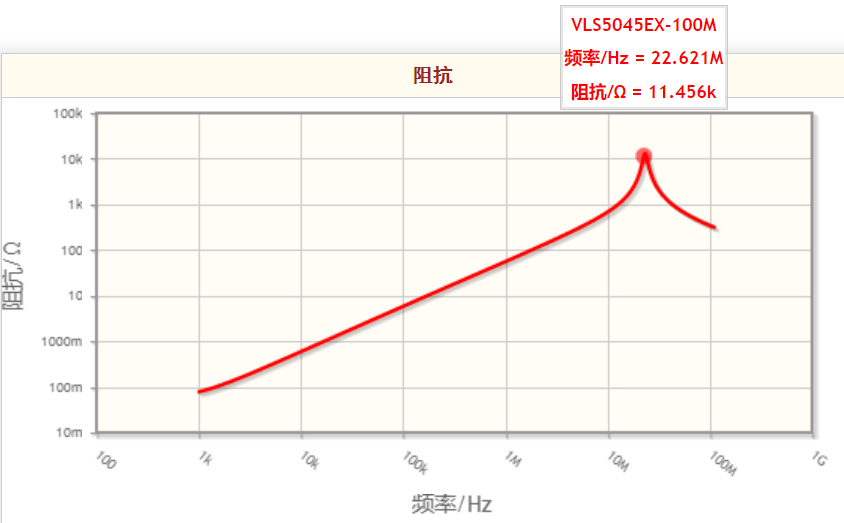

上图为TDK的VLS5045EX-100M的阻抗频率特性曲线,可以看出:

①自谐振频率f0为22MHz;

②当频率

③当频率>f0时,随着频率增高,阻抗Z是降低的,此时电感呈容性。

这些内容比较基础,这里只是简单回顾下,想必屏幕前的你已经比较熟悉了。那电感的感值频率曲线又是怎样的呢?

电感频率特性

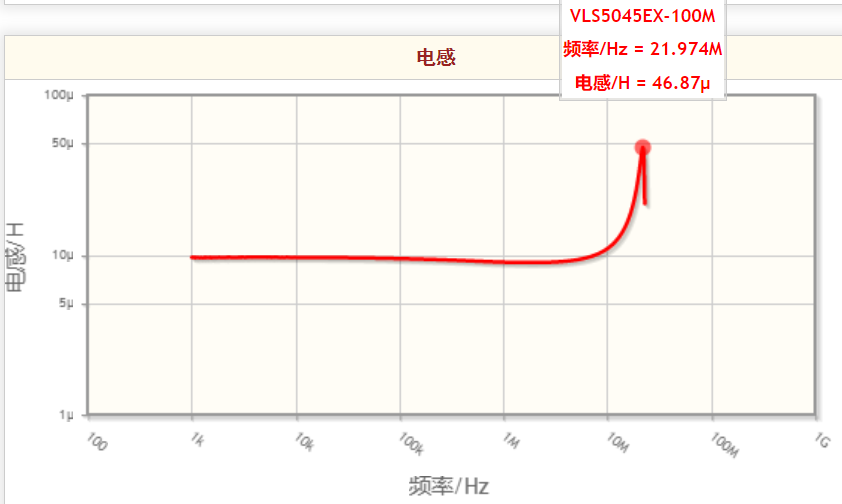

上图为TDK的10uH电感VLS5045EX-100M的电感频率特性曲线,可以看出:

①在自谐振频率点22MHz左右,电感感值达到最大值46.87uH;

②从1kHz~10MHz范围内,电感感值稳定在10uH;

③频率超过自谐振频率后,电感感值开始快速下降。下降到什么程度,在该曲线中未体现出来。

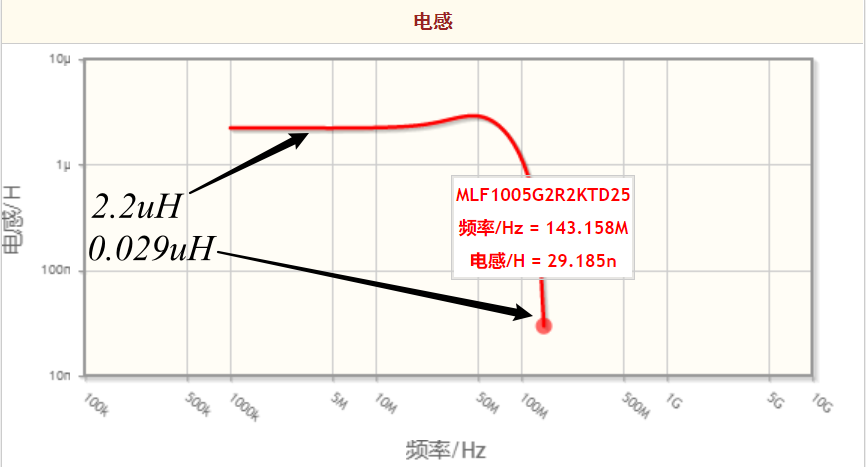

那么我们再看TDK的另外一颗2.2uH的电感MLF1005G2R2KTD25。如下图所示,当频率超过自谐振频率后,感值急剧下降,从2.2uH降到0.029uH,变为原来的1/100!

总结

说到这里,我想你应该可以知道文章开头两个问题的答案。

电感的感值随着频率如何变化?

(前提:暂不考虑温度和电流值的影响)

①当频率

②当频率在f0附近时,电感感值会大于额定感值;

③当频率>f0时,电感感值会急剧下降,甚至变为原来的1/100或者更小。

而在开关电源应用中,一旦开关频率fsw贴近或者超过电感自谐振频率f0,电感感值会增大或者变得非常小,甚至会呈容性,电路设计偏离原有设计逻辑,导致整体功能异常,甚至损耗周围器件。

保证f0>10fsw,就是为了让电感有足够的设计裕量来保证其感值稳定性。

来源: 本文转载自硬件微讲堂

审核编辑:汤梓红

-

电感

+关注

关注

54文章

6161浏览量

102962 -

DC-DC

+关注

关注

30文章

1963浏览量

82377 -

开关频率

+关注

关注

2文章

93浏览量

21541 -

自谐振频率

+关注

关注

0文章

4浏览量

5445

原文标题:DC-DC电感选型时自谐振频率要大于10倍开关频率?

文章出处:【微信号:电子设计联盟,微信公众号:电子设计联盟】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

电容器阻抗/ESR频率特性是指什么

传递函数的频率特性

频率特性分析仪的构成与频率特性分析仪的原理分类

电源的阻抗频率特性和电感频率特性

电源的阻抗频率特性和电感频率特性

评论