一、何为clock gating

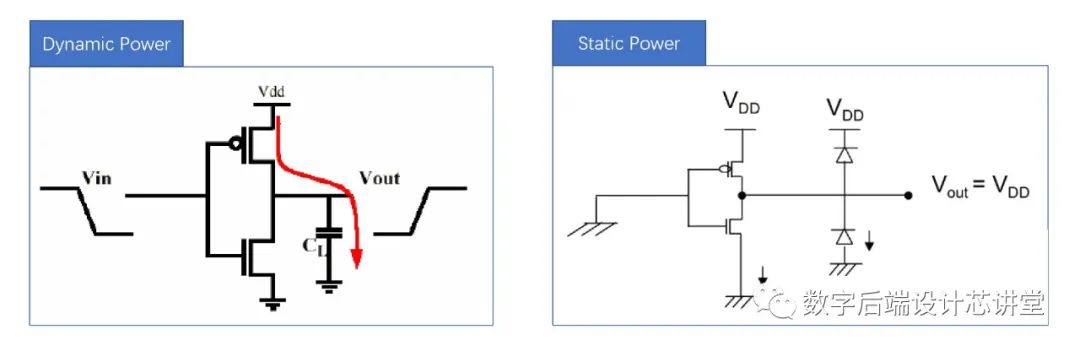

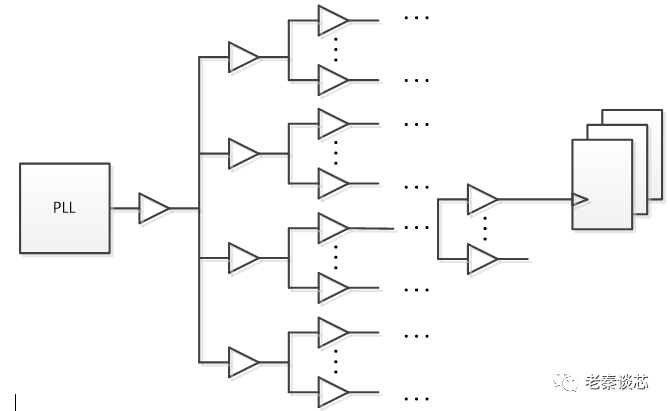

芯片中大部分的动态功耗消耗在时钟网络中。这是由于时钟树上的单元(cells)有较高的翻转率、驱动能力较大且数量较多所导致的。

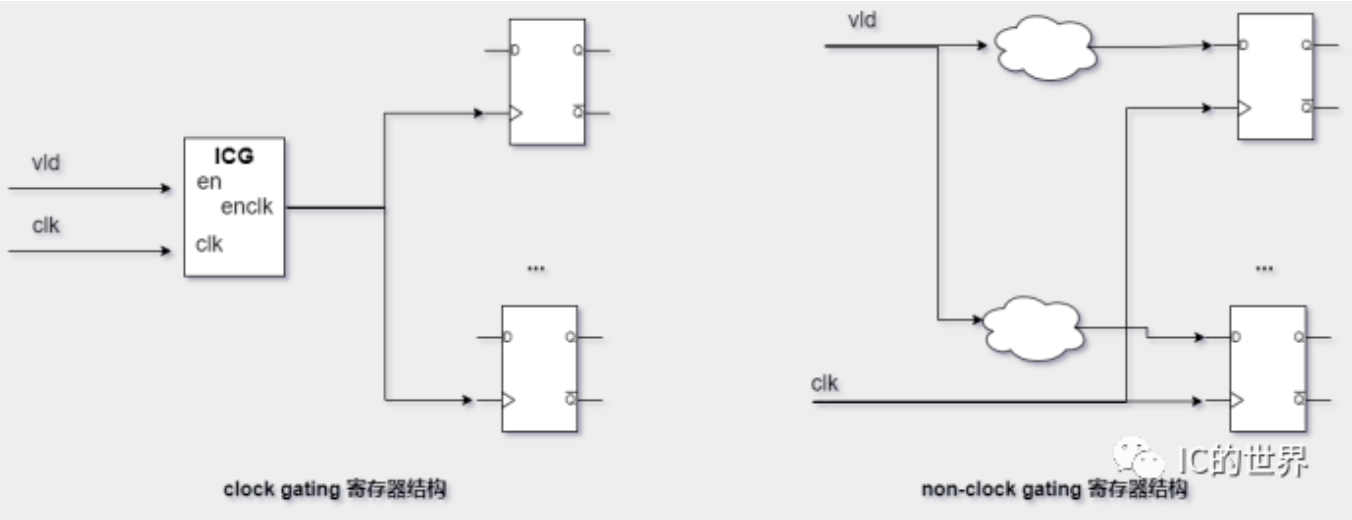

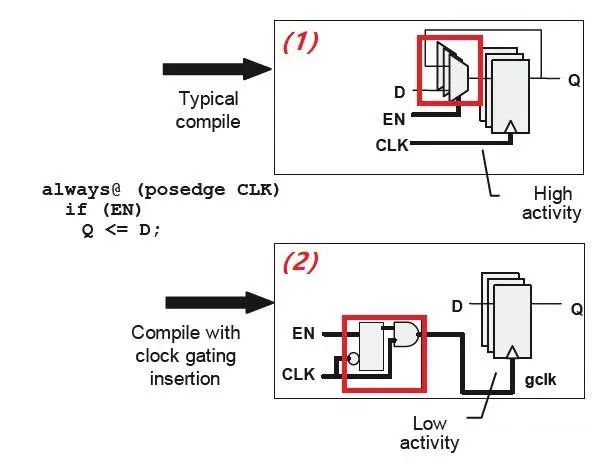

因此,为了有效减小时钟树上的动态功耗,人们引入了门控时钟(clock gating)技术,即用一个控制信号控制时钟的开启,在模块不工作时关闭时钟,在工作时打开时钟,从而降低触发器总的翻转率,达到降低功耗的目的。

插入门控时钟单元来降低芯片功耗的效果主要由单个门控时钟单元所控制的触发器或锁存器的数量决定。

• 新增的clock gating单元本身也会增加功耗和面积;当clock gating单元输出端控制的寄存器数目较少时,可能会导致增加的功耗比时钟翻转降低的动态功耗还要大。控制的寄存器数量越多,效果越明显。在综合的时候,可以设置采用clock gating的最低RegisterBank位数。

• 降低动态功耗和时钟关断的时间比例有关。如果一个模块关断的时间很短,那么加入clock gating就用处不大。

• clock gating的效果取决于其在时钟树的位置,是靠近clock tree的root还是sink。靠近root时,可以控制更多的寄存器,对功耗降低更有效;而靠近sink时,则timing更容易满足。

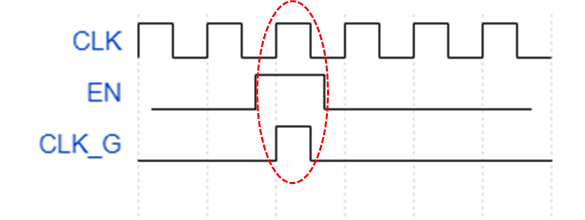

例如,在这个电路中,只有当EN为1时,CLK信号才会重写DFF的数据,否则的话,所有的翻转都是无效的。因此,只需要实现CLK_G的波形即可。

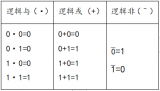

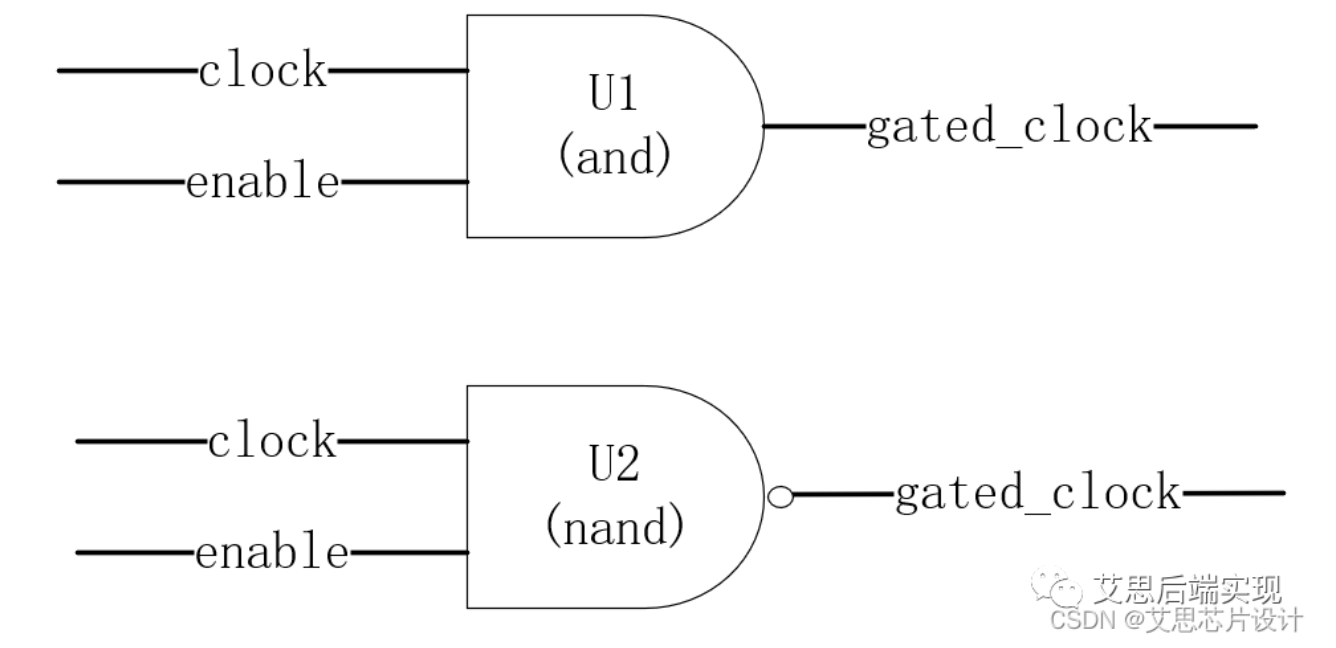

对于简单逻辑门的clock gating,最简单的实现方式是使用AND门或OR门来实现,对CLK信号进行与或运算。

1. AND门clock gating

(1)基本概念

对于AND门的clock gating,即高电平有效的gating,当EN为1时,门控打开,CLK_IN信号可以传递出去;而当EN为0时,门控关闭,CLK_IN信号则无法通过门控传递出去。

如上图所示,对于AND门的clock gating,EN信号的切换必须发生在CLK_IN的低电平区间,否则在输出CLK_OUT时可能会出现glitch,如下图所示。

(2)timing check

1)上升沿触发

在上图中,UAND0/B pin是clock信号,而gating信号则由UDFF0/Q经过组合逻辑后输入到UAND0/A pin中。

在前面的讨论中,我们已经得知,如果EN信号来自上升沿触发的寄存器,则对于setup check来说,要求门控信号在上升沿之前到达;而对于hold来说,则要求门控信号只能在下降沿之后发生变化。

因此,针对上图电路中的UAND0/B pin,CLKA发出的gating信号只能在5 – 10ns的范围内达到,才能满足时序要求。

此时,hold是半周期check,比较难meet;

以下是setup和hold check的timing report:

setup:

hold:

2)下降沿触发

如果使用下降沿触发的寄存器产生EN信号,则对于hold来说是0 cycle check,而对于setup来说则是半周期check。因此,在使用基于AND门的gating时,EN信号通常由下降沿触发的寄存器产生。

如下图所示,即使使用下降沿触发的寄存器产生EN信号,对于基于AND门的gating,gating信号依然需要在5 – 10ns之间到达,以满足时序要求。

setup和hold check的timing report:

setup

hold

2. OR门clock gating

(1)基本概念

对于OR门的clock gating,即低电平有效的gating,当EN为0的时候,门控打开,CLK_IN可以传递出去;当EN为1的时候,门控关闭。

需要注意的是,在实现OR门的clock gating时,EN信号的切换必须发生在CLK_IN的高电平区间,以避免在输出CLK_OUT时出现glitch,如下图所示。

(2)timing check

1)上升沿触发

类似于之前的讨论,如果EN信号来自上升沿触发的寄存器,则对于setup check来说,要求门控信号在下降沿之前到达;对于hold来说,则要求门控信号只能在上升沿之后发生变化。

因此,针对MCLK发出的gating信号,在这种情况下需要在0 – 4ns的范围内到达,才能满足时序要求。

根据上述时序要求,此时hold为0 cycle check,而setup为半周期check。

setup和hold check的timing report:

setup

hold

2)下降沿触发

与之前讨论类似,如果EN信号来自下降沿触发的寄存器,则hold为半周期check,比较难以满足。因此,在基于OR门的gating技术中,建议使用上升沿触发的寄存器来产生EN信号,以确保时序要求的满足。

3. 基于latch的clock gating

根据之前的讨论可知,在基于基本逻辑门的clock gating技术中,EN信号的时间窗口只有半个周期的时间,因此对于一些时序要求较为严格的电路,可能需要使用latch来实现timing borrow,以确保时序的满足。

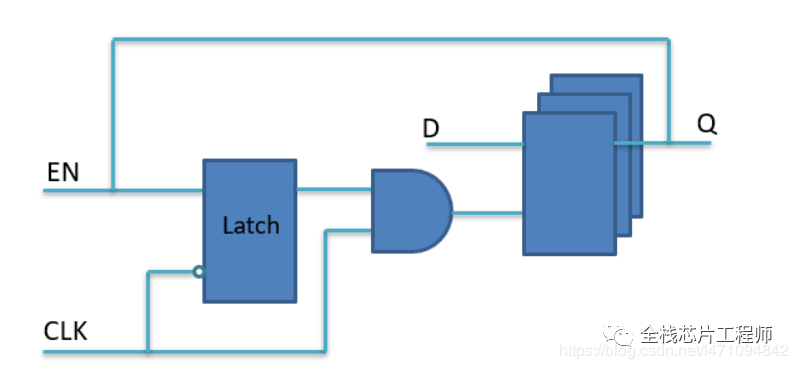

(1) Latch + AND门的gating

如上图所示,在AND门前面加入low-active latch,EN信号来自上升沿触发器。

当时钟信号是低电平时,latch处于透明状态,根据输入更新输出;当时钟信号从低电平变为高电平时,latch会读取数据输入端的输入信号,并将其保存在锁存器内部的状态中;波形图如下:

由于这种latch是低电平有效的,因此在时钟高电平期间,即使EN信号存在glitch(如上图中红色虚线1所示),也不会影响latch的输出EN_Latch。

而在时钟低电平期间,EN信号的glitch会传递到latch的输出(如上图中红色虚线2所示),但由于EN_Latch需要与CLK信号做与运算,此时gating信号CLK_Gated仍然不会受到影响。

如上图所示,无论EN在0-1 ns还是1-2 ns之间变化,CLK_Gated均不受影响,即EN可以在0-2 ns一个周期的时间窗口内到达;此时,hold是0 cycle check,setup是一个周期check;

基于这种结构的clock gating,既可以避免毛刺,同时也避免了EN信号只有半个周期的要求。

(2) Latch + OR门的gating

与Latch + AND门不同的是,需要使用low-active latch,且EN信号来自下降沿触发的寄存器。

4. ICG

(1)分离时钟门控

上述讨论中提到的基于latch的clock gating结构,指的是分离的时钟门控单元,当考虑skew时,依然可能会引入glitch的问题(以latch + AND门为例)。

在下图中,delay是指,当CLK为0的时候,latch透明,数据信号EN要传输到latch的输出端EN_Latch,所经过的一个锁存器的延迟(CLK to latch/Q delay);

CLK一路送到latch,另一路送到AND/B,当latch和AND在layout中相距较远时,此时CLK和CLK_B之间就会有skew存在;

CLK和CLK_B之间的skew会引入到CLK_Gated信号中,并可能导致毛刺问题。如果skew的时间差大于delay,就可能会在CLK_Gated信号中引入毛刺,毛刺的宽度大约为skew-delay。

因此,在物理实现的时候,需要设置net weight,将latch和AND门靠近摆放;并且latch/CK需要设置non-stop pin。

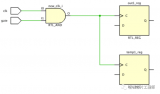

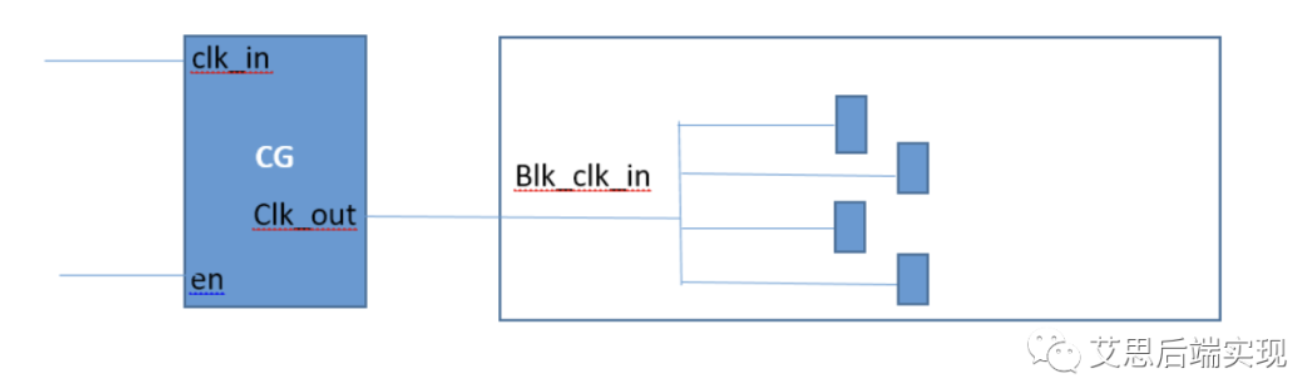

(2)集成时钟门控ICG

现在几乎所有的标准单元库都提供了集成门控时钟单元(ICG),这种单元将上述所述的latch+ AND门或latch + OR门组合成一个标准单元。

值得注意的是,latch前面的OR门是为了DFT加入的,而控制信号SE可以根据需要选择test_mode或scan_en。

ICG的应用相对简单,无需特别的设置,且CTS对于ICG的时序分析更加自动化。ICG的setup和hold时间都已经在库中进行了建模,并且其CK引脚默认为implicit non-stop pin。

以上内容只是简单的示例,实际上,根据sequential cell的类型、控制寄存器触发边沿和测试控制信号的位置,库中可以提供多种不同的ICG单元。

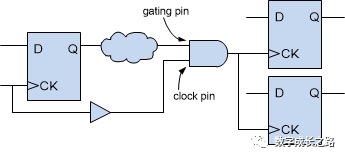

(3)什么情况下会做clock gating check(tool infer)

可以通过经过cell的信号和经过的cell类型这两个条件判断:

1)经过cell的信号

• 被gating的clock信号,在下游需要当做clock使用(即达到reg的CK pin、output port);

• gating的EN信号,不能带有clock属性;或者原来带有clock属性的EN信号,经过gating cell后不再当做clock使用,或者被后面的generated clock打断了。

如图所示,在AND门的输出端,定义了一个generated_clock,其master为CLKA。因此CLKB无法传播到AND后面,相当于下游不再作为clock信号使用。

在这种情况下,PT会将CLKA视为时钟信号,CLKB视为门控信号,并对AND门进行clock gating check。

gating的EN信号和被gating的clock信号,要fanout到gating cell相同的输出pin;如图中一个EN和CLK,一个faout到了A,另一个fanout到了B,那么工具是不会自动的做clock gating check的。

以上三个条件要同时满足,工具才会做clock gating check。

2)经过的cell类型

除了上述三个约束条件外,另一个需要满足的条件是信号必须通过非复杂类型的cell。如果一个cell是non-unate cell,那么这个cell可以被视为复杂类型的cell。

对于复杂类型的cell(如常见的异或、同或和MUX),工具不会自动执行时钟门控检查。

append

• 可以通过使用set_clock_gating_check命令来显式地指定门控单元的时钟门控关系。

• 如果用户使用set_clock_gating_check命令设置的时钟门控检查类型与工具推断出的不一致,则通常会报警告,并且以用户的设置为准。

• 此外,用set_clock_gating_check设置的setup/hold时间值优先级高于库中定义的值。

• 如果不需要进行某些时钟门控检查,则可以使用set_disable_clock_gating_check命令将其禁用。

-

寄存器

+关注

关注

31文章

5343浏览量

120357 -

锁存器

+关注

关注

8文章

906浏览量

41508 -

触发器

+关注

关注

14文章

2000浏览量

61155 -

门控时钟

+关注

关注

0文章

27浏览量

8950 -

CLK

+关注

关注

0文章

127浏览量

17169

发布评论请先 登录

相关推荐

FPGA的时钟门控是好还是坏?

逻辑电路的基础知识

通常有两种不同的时钟门控实现技术

什么是门控时钟 门控时钟降低功耗的原理

ASIC的clock gating在FPGA里面实现是什么结果呢?

clock gating基础知识介绍:基本逻辑门控/ICG

clock gating基础知识介绍:基本逻辑门控/ICG

评论