最近一直在研究两件事,目前都有了一些成果。

第一件事:不同版图EDA工具间数据的转换问题,除了基于OA的database的pcell 还是存在一些各家工具自己封闭的内容,这部分内容如何能够不同tool上做对应。

因为目前主流foundry都会提高两套PDK,所以这部分foundry提供ipdk的一般问题都不大。这里不展开说。

第二件事:如果使用验证工具来完善版图上的设计流程。

这里举个例子:如果版图没有完全使用SDL 这样的设计Flow来做,后期导致net 和device 没法和电路上一一对应。这个问题有没有办法解决。Virtuoso 配合pvs 可以重塑SDL对应关系 Custom compiler 配合ICV同样可以实现SDL的关系。CC中对于的command是:

lx::establishCorrespondenceFromLVS -path -layout -schematic

如果使用第三方工具做的PV 是否也能够实现这样的功能。看过我文章的应该看到过前面提到的calibre的perc,perc确实可以实现从lvs pass的svdb 或dfmdb结果中提取出device信息,net信息。但是我感觉还不够方便。

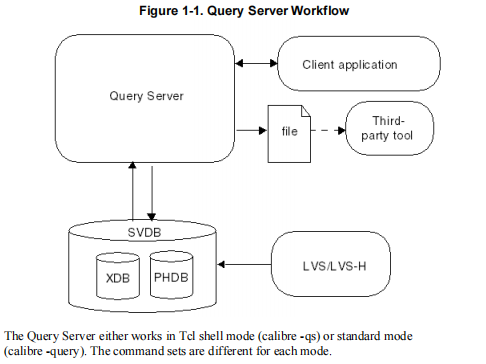

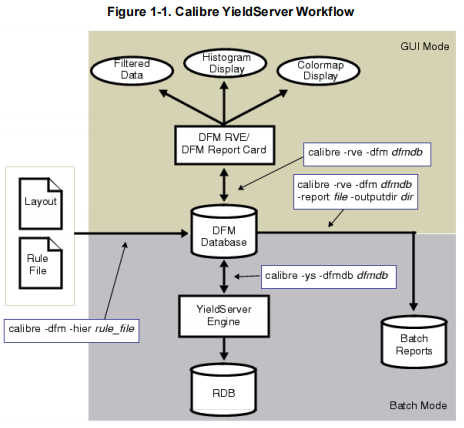

今天介绍的calibre的 queryServer 和YieldServer 能够更快的提取出这些信息。DRC LVS可能大家比较熟悉对query和yield 比较陌生,这两个server在某些场景下也是非常好用,也很方便。

对应的命令是calibre -qs 和calibre -ys

从calibre svdb结果到Custom compiler重建SDL也是基于query和Yield 来实现的

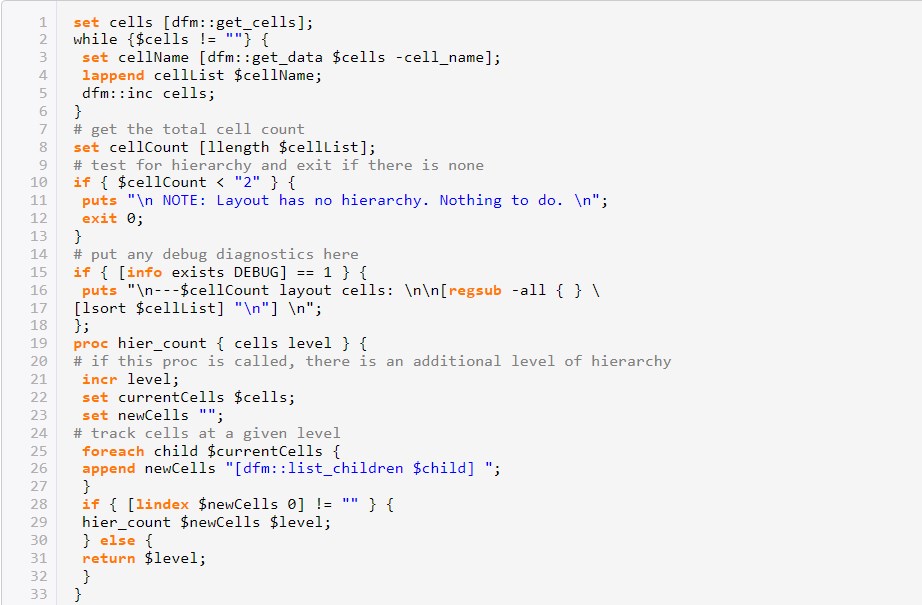

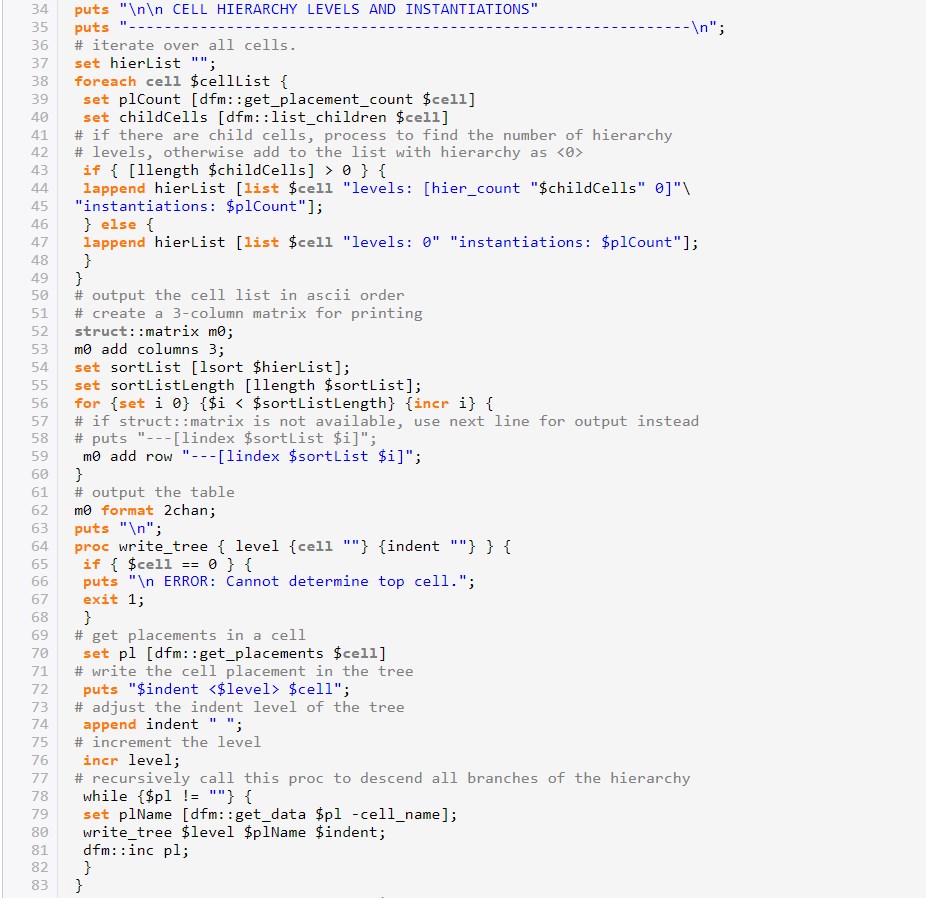

下面列举个case演示qs 和ys 的部分功能,

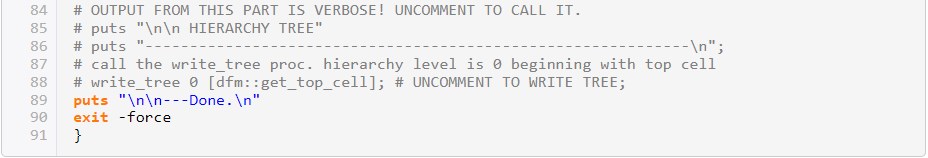

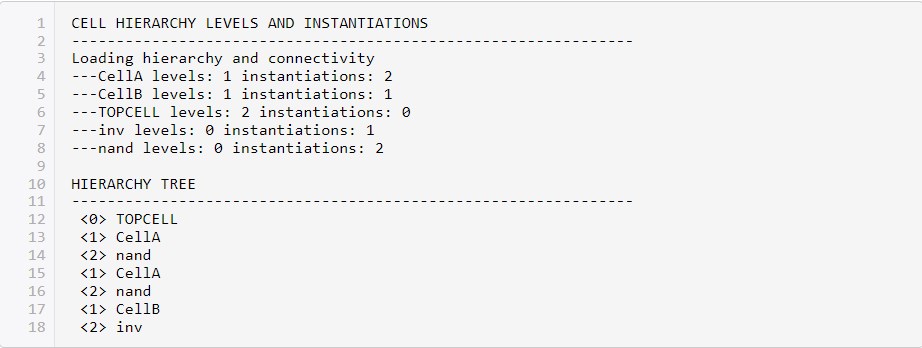

这个case是使用YieldServer 的脚本来实现Hierarchy的报告

calibre -qs -svdb svdb -exec qs.tcl

打印出的效果:

-

EDA工具

+关注

关注

4文章

268浏览量

31845 -

DRC

+关注

关注

2文章

149浏览量

36230 -

SDL

+关注

关注

0文章

18浏览量

7410 -

LVS

+关注

关注

1文章

36浏览量

9959

发布评论请先 登录

相关推荐

AN1258 - OP AMP PRECISION DESIGN: PCB LAYOUT - MICROCHIP

RDA锐迪科(上海)微电子招聘Layout设计工程师

Antenna Design and RF Layout Guidelines

Mentor工具简介Calibre物理验证系列

非规则矩形电阻在Calibre LVS中阻值提取

Laker & Calibre Bandgap 实例教程

Design and Layout of a Video G

Soft-Design-Showcases.NB3000_Live_Webcam_Server

EDA云实证Vol.13:暴力堆机器之王——Calibre

到底谁能提升Calibre的效率?

calibre query和yeild server在layout design上的应用

calibre query和yeild server在layout design上的应用

评论