1 简介

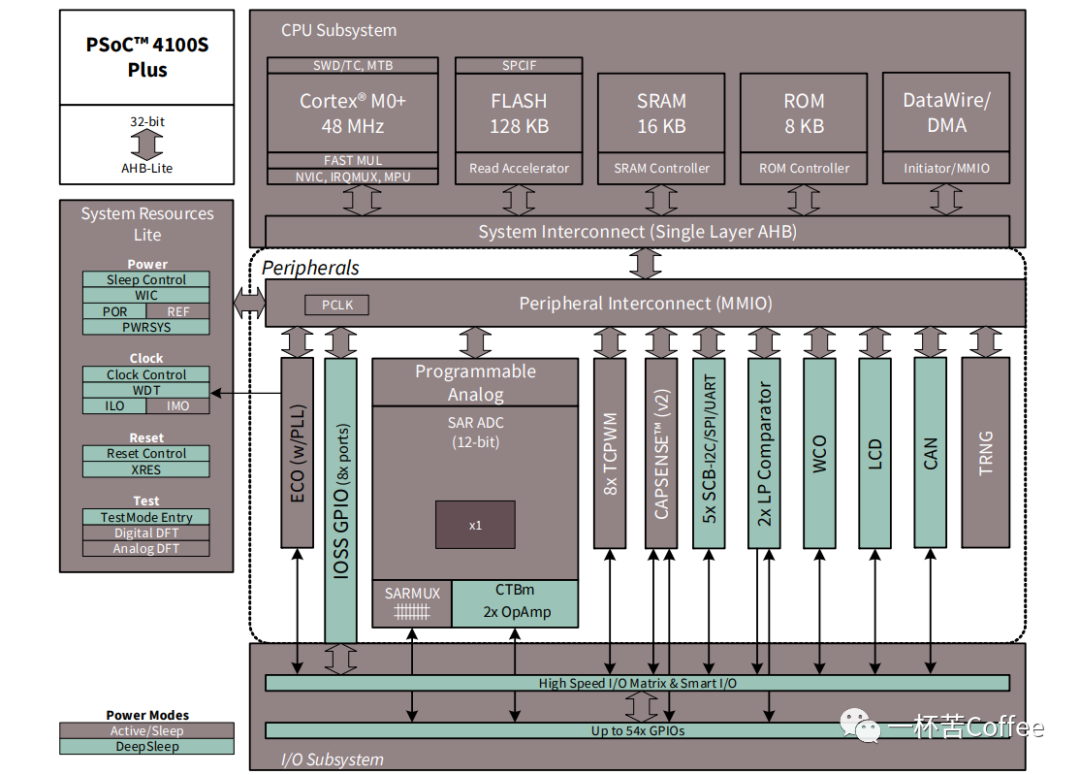

PSoC™4是一种可扩展和可重构的平台架构,适用于一系列可编程嵌入式系统控制器,具有Arm®Cortex®-M0+ CPU,同时符合AEC-Q100标准。它结合了可编程和可重构的模拟和数字块与灵活的自动路由,Cypress现在已被Infineon收购。Cypress 1982年在美国加州成立,主要提供汽车、工业、网络平台到互动消费以及移动设备的解决方案。该公司主要有四个部门:可编程系统部门、存储产品部门、数据通信部门、新兴技术部门。

2 PSoC™4介绍

PSoC™4100S Plus是PSoC™4平台架构的成员。它结合了带有标准通信和定时外设的微控制器、具有一流性能的电容式触摸传感系统(CAPSENSE™)、可编程通用连续时间和开关电容模拟模块以及可编程连接。PSoC™4100S Plus产品将与PSoC™4平台的产品能实现向上兼容,以满足新的应用和设计需求。

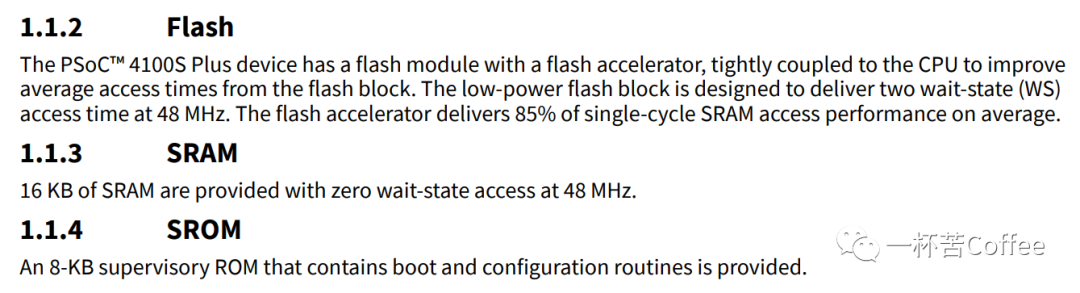

- 存储器

提供128K Flash、16KB SRAM、5KB ROM。

- 电源介绍

PSoC™4100S Plus使用单个外部电源,工作范围为1.8 V±5%(外部调节)或1.8 V至5.5 V(内部调节),并有三种不同的电源模式,其中转换都是由电力系统管理的。PSoC™4100S Plus提供活动、睡眠和深度睡眠低功耗模式。所有子系统都在主动模式下运行。CPU子系统(CPU、闪存和SRAM)在睡眠模式下被时钟门控关闭,而所有外设和中断都是活动的,在唤醒事件上具有瞬时唤醒。在深度睡眠模式下,高速时钟和相关电路被关闭;从该模式唤醒需要35µs。opamp可以在深度睡眠模式下保持运行。

- 时钟系统

PSoC™4100S Plus时钟系统负责为所有需要时钟的子系统提供时钟用于在不同时钟源之间切换而不会出现故障。此外,时钟系统确保不存在亚稳条件。PSoC™4100S Plus的时钟系统由IMO, ILO, 32 khz手表晶体振荡器(WCO), MHz ECO和PLL组成,并提供外部时钟。WCO允许将IMO锁定到32khz振荡器。

硬件I2C块实现了一个完整的多主和从接口(它能够进行多主仲裁)。该块能够以高达1mbps (Fast Mode Plus)的速度运行,并具有灵活的缓冲选项,以减少CPU的中断开销和延迟。它还支持EZI2C,在PSoC™4100S Plus的内存中创建邮箱地址范围,并有效地减少I2C通信,从内存中的数组读取和写入。此外,该块支持8bit位深FIFO接收和发送,通过增加CPU读取数据的时间,大大减少了由于CPU没有及时读取数据的而导致的时钟扩展的需要。I2C外设兼容NXP I2C总线规范和用户手册(UM10204)中定义的I2C标准模式和快速模式Plus设备。I2C总线I/O是用Open Drai Mode的GPIO实现的。

- UART mode

这是一个全功能的UART,运行速度高达1mbps。支持汽车单线接口(LIN),红外接口(IrDA)和智能卡(ISO7816)协议,所有这些都是基本UART协议的次要变体。此外,它支持9位多处理器模式,允许通过普通RX和TX线路连接的外设寻址。支持常见的UART功能,如奇偶校验、中断检测和帧错误。8深FIFO允许更大的CPU服务延迟被容忍。

- SPI mode

SPI模式支持全摩托罗拉SPI, TI SSP(增加一个启动脉冲用于同步SPI编解码器)和National Microwire(半双工形式的SPI)。SPI块可以使用FIFO。

有一个CAN模块,它实现了Bosch规范中定义的CAN 2.0B,并符合ISO-11898-1标准。

- GPIO

PSoC™4100S Plus具有多达54个gpio。每个GPIO有8种驱动模式:

- Analog input mode (input and output buffers disabled)

- Input only

- Weak pull-up with strong pull-down

- Strong pull-up with weak pull-down

- Open drain with strong pull-down

- Open drain with strong pull-up

- Strong pull-up with strong pull-down

- Weak pull-up with weak pull-down

- 特殊功能外设

- CAPSENSE™(手势识别)

PSoC™4100S Plus通过CAPSENSE™sigma-delta (CSD)模块支持CAPSENSE™,该模块可通过模拟多路复用总线通过模拟开关连接到任何引脚。因此,CAPSENSE™功能可以在软件控制系统中的任何可用引脚或引脚组上提供。为CAPSENSE™块提供了PSoC™Creator组件,使其易于用户使用。

屏蔽电压可以在另一个模拟多路总线上驱动,以提供耐水能力。通过与传感电极同步驱动屏蔽电极来提供水容忍度,以防止屏蔽电容衰减被感测输入。也可以实现近距离感应。CAPSENSE™块有两个IDAC,如果不使用CAPSENSE™(在这种情况下两个IDAC都可用),或者如果CAPSENSE™不耐水使用(一个IDAC可用),则可用于一般用途。CAPSENSE™模块还提供10位斜率ADC功能,可与CAPSENSE™功能结合使用。CAPSENSE™模块是一种先进的低噪声可编程模块,具有可编程电压参考和电流源范围,可提高灵敏度和灵活性。它也可以使用外部参考电压。它具有全波CSD模式,交替感应到VDDA和接地以消除电源相关噪声。

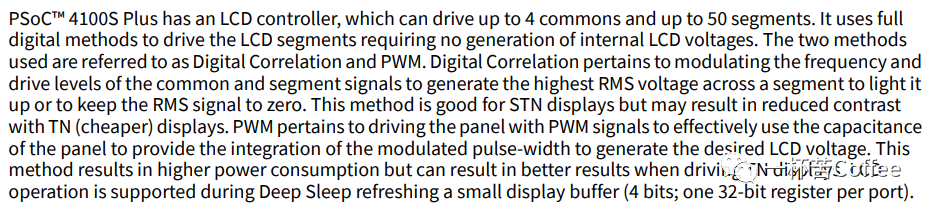

- LCD显示驱动

3 方案介绍

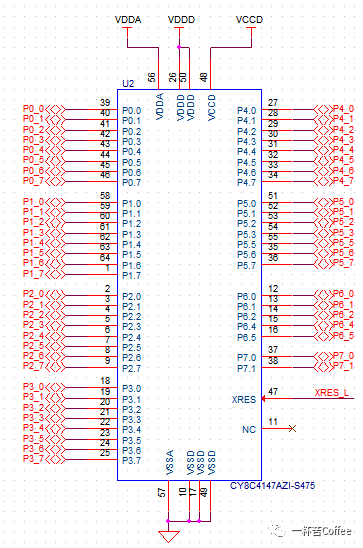

今天主要介绍的芯片是CY8C4147AZI-S475,共有8组端口。

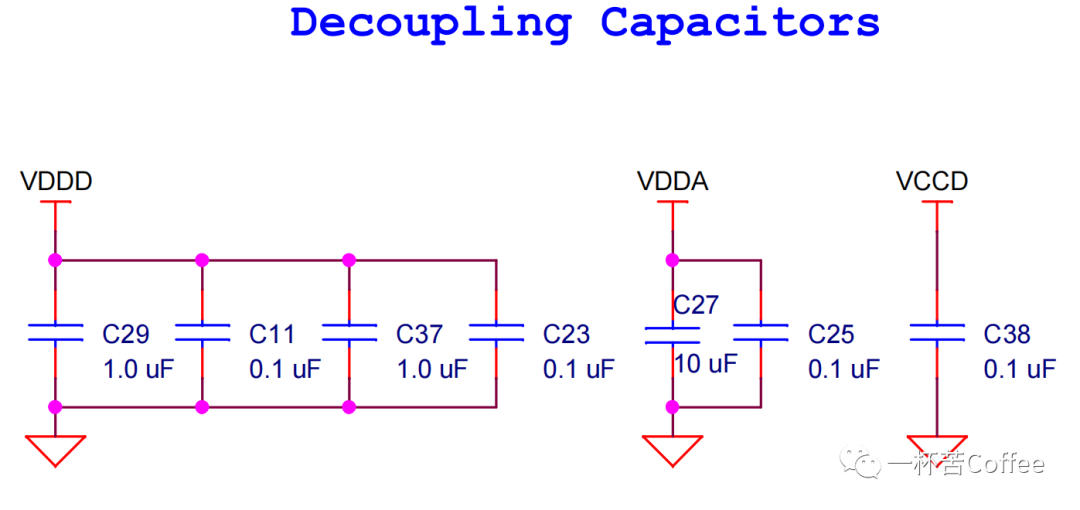

- 电源电路设计

电源部分,主要包含VDDD、VDDA和VCCD,各部的功能分别见下:

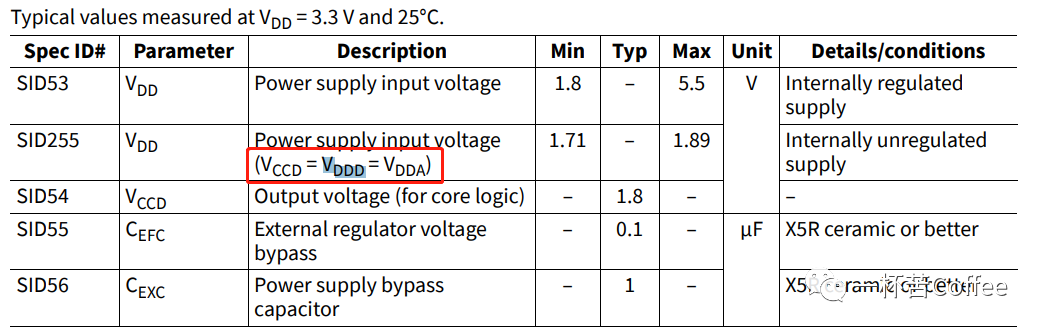

供电范围设计指导:

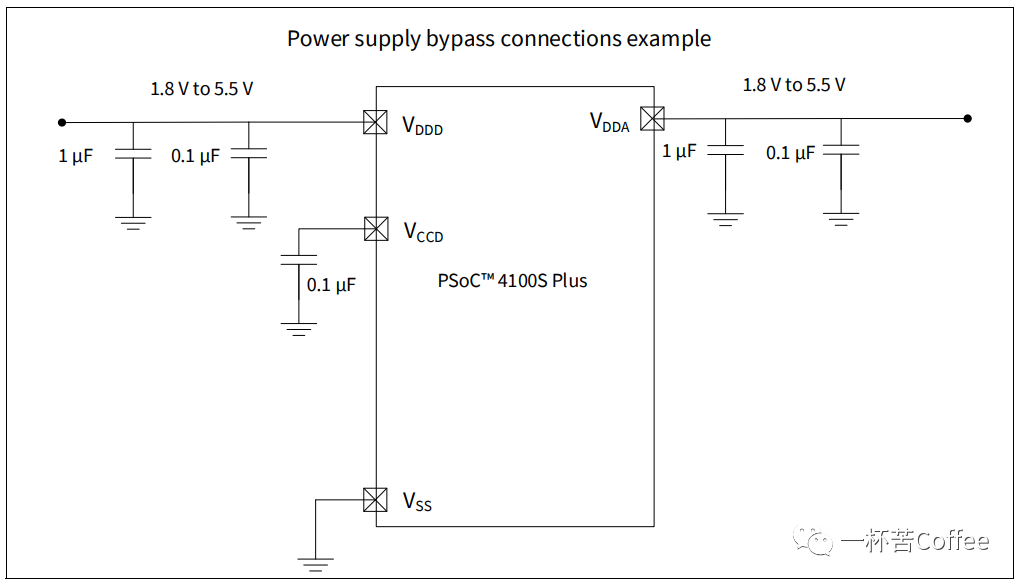

手册设计参考设计:

- 时钟电路设计

时钟主要包含两个部分,分别是主时钟和RTC时钟,电路设计分别见下:

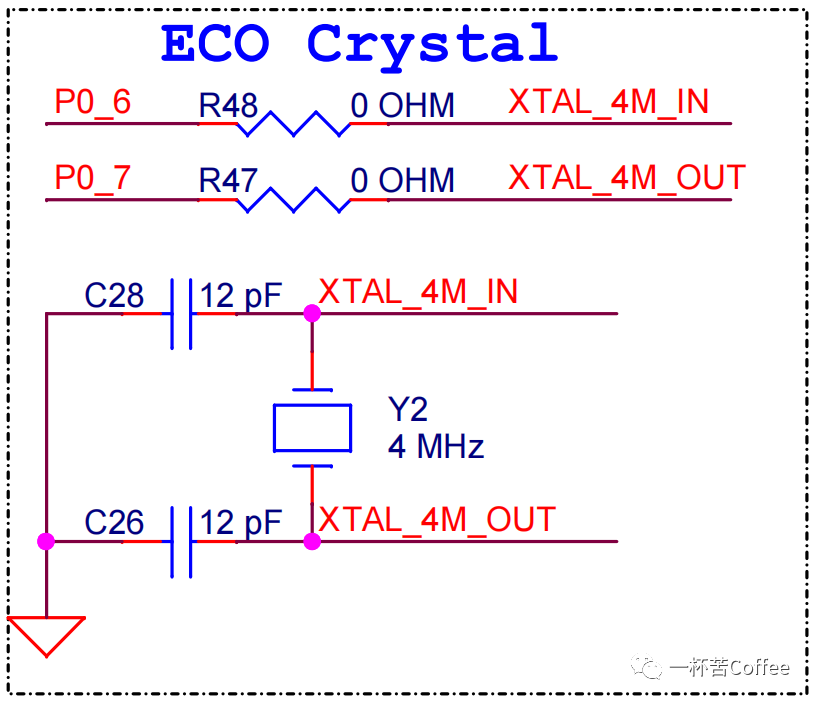

- 主时钟电路设计

时钟的引脚为P0_6和P0_7,采用4M的晶振,时钟输入范围4to33 MHz。

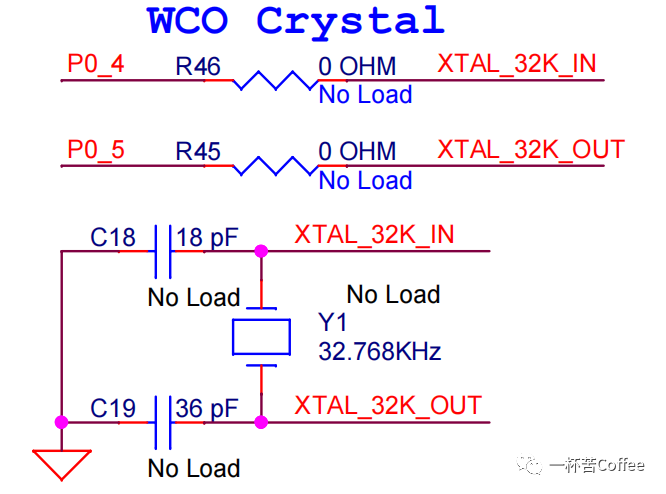

- 实时时钟电路设计

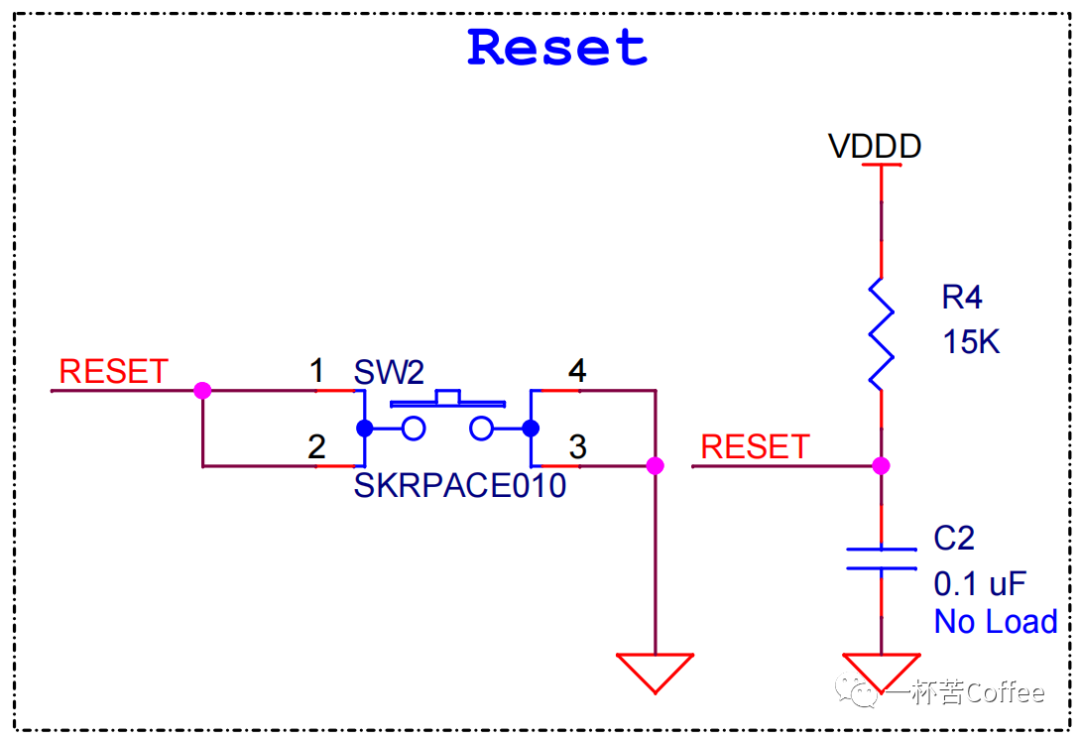

- 复位电路

复位采用的是低电平复位的方式,其中焊接C2可实现硬件消抖。

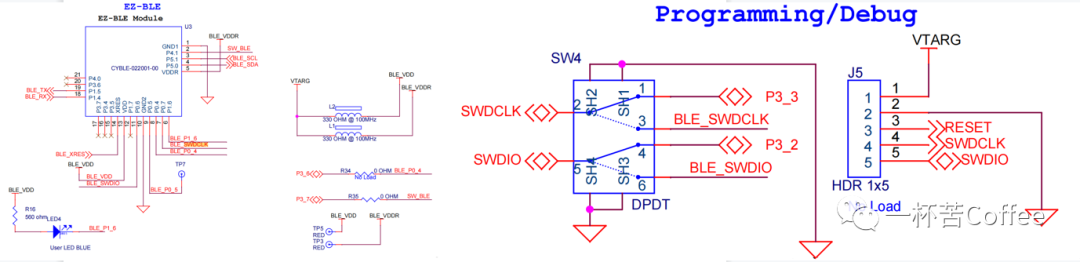

- 下载电路

软件下载这个位置还没有研究过,感兴趣的朋友可以研究一下。

-

嵌入式

+关注

关注

5103文章

19265浏览量

309960 -

PSoC

+关注

关注

12文章

173浏览量

92428 -

嵌入式系统

+关注

关注

41文章

3645浏览量

130080 -

cpu

+关注

关注

68文章

10945浏览量

213879 -

电路设计

+关注

关注

6681文章

2475浏览量

206317

发布评论请先 登录

相关推荐

怎么成为硬件电路设计高手?

硬件电路设计之PSoC™4100S Plus电路设计

硬件电路设计之PSoC™4100S Plus电路设计

评论