事故现场

先贴一下代码的简版:

localparam S_IDLE = 4'd0;

localparam S_HEAD = 4'd1;

localparam S_PAYLOAD = 4'd2;

localparam S_TAIL = 4'd3;

localparam S_ERROR = 4'd4;

reg [3:0]status, nx_status;

always @(posedge clk_100m or negedge rst_spt_n)begin

if(!rst_spt_n) status <= S_IDLE;

else status <= nx_status;

end

always @* begin

case(status)

S_IDLE: ...

S_HEAD: ...

S_PAYLOAD: ...

S_TAIL: ...

S_ERROR: ...

default: nx_status = status;

endcase

end

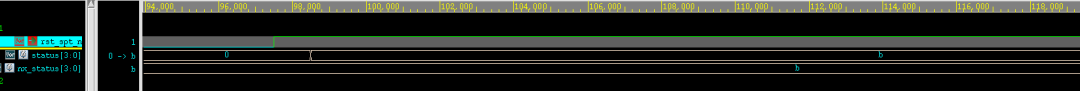

状态机本身很简单,default也写了,然后进行仿真时看到了这样的波形:

nx_status仿真初始的值为4'hb,而后导致status的值也为4'hb,始终无法回到IDLE状态,整个电路的功能也无法正常开展。

事故分析

这个问题得以暴露要感谢在验证环境中打开了initreg功能:

CMP_OPTIONS += +vcs+initreg+random

RUN_OPTIONS += +vcs+initreg+$(SEED)

通过这样的配置使得reg型的数值在仿真开始时被赋值为随机数。该bug就是由于nx_status被赋值为状态之外的随机数而发现的。

在代码中,nx_status没有任何位置被进行“复位”,当然了因为nx_status本身不是寄存器也就不存在复位的问题,不过状态机的alway@*中的处理是有问题的,这导致nx_status一旦跑“飞”了,status下一拍会更新为nx_status的值,那么整个状态机将不可恢复。

事故解决

修改状态机的写法为:

always @* begin

case(status)

S_IDLE: ...

S_HEAD: ...

S_PAYLOAD: ...

S_TAIL: ...

S_ERROR: ...

default: nx_status = S_IDLE;

endcase

end

或者

always @* begin

nx_status = S_IDLE;

case(status)

S_IDLE: ...

S_HEAD: ...

S_PAYLOAD: ...

S_TAIL: ...

S_ERROR: ...

default: nx_status = status;

endcase

end

重新仿真后波形正确:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

寄存器

+关注

关注

31文章

5386浏览量

121438 -

仿真器

+关注

关注

14文章

1019浏览量

84001 -

状态机

+关注

关注

2文章

492浏览量

27694

发布评论请先 登录

相关推荐

Verilog状态机+设计实例

在verilog中状态机的一种很常用的逻辑结构,学习和理解状态机的运行规律能够帮助我们更好地书写代码,同时作为一种思想方法,在别的代码设计中也会有所帮助。 一、简介 在使用过程中我们常说

什么是状态机?状态机的三种实现方法

文章目录1、什么是状态机?2、状态机编程的优点(1)提高CPU使用效率(2) 逻辑完备性(3)程序结构清晰3、状态机的三种实现方法switch—case 法表格驱动法函数指针法小节摘要:不知道大家

发表于 12-22 06:51

如何写好状态机

如何写好状态机:状态机是逻辑设计的重要内容,状态机的设计水平直接反应工程师的逻辑功底,所以许多公司的硬件和逻辑工程师面试中,状态机设计几乎是必选题目。本章在引入

发表于 06-14 19:24

•97次下载

什么是状态机 状态机的描述三种方法

状态机 1、状态机是许多数字系统的核心部件,是一类重要的时序逻辑电路。通常包括三个部分:一是下一个状态的逻辑电路,二是存储状态机当前状态的时

什么是状态机?状态机5要素

玩单片机还可以,各个外设也都会驱动,但是如果让你完整的写一套代码时,却无逻辑与框架可言。这说明编程还处于比较低的水平,你需要学会一种好的编程框架或者一种编程思想!比如模块化编程、状态机编程、分层思想

状态模式(状态机)

以前写状态机,比较常用的方式是用 if-else 或 switch-case,高级的一点是函数指针列表。最近,看了一文章《c语言设计模式–状态模式(状态机)》(来源:embed linux

发表于 12-16 16:53

•9次下载

什么是状态机?状态机的种类与实现

状态机,又称有限状态机(Finite State Machine,FSM)或米利状态机(Mealy Machine),是一种描述系统状态变化的模型。在芯片设计中,

状态机怎么上来就错了?怎么解决?

状态机怎么上来就错了?怎么解决?

评论