复位信号在使用前一般需要进行消抖处理,也称为复位滤毛刺。复位的抖动可能会导致芯片产生多次复位动作,给系统带来不确定性和误差。消抖的目的是为了确保复位信号的稳定性和可靠性,从而保证系统能够正常工作。

通过消抖,可以消除复位信号的抖动干扰,保证复位信号的可靠性和稳定性,避免系统故障和数据丢失等问题。

举个例子,如果要消除30ns以下的复位抖动,那么30ns以下的复位信号rst_n拉低操作就会被消抖电路消除,不会对电路产生任何的影响,只有30ns以上的复位拉低操作才能作用于内部电路。

所以复位消抖电路具体长什么样子呢?目前我了解的有三种方式,不过因为没有实际参与过CRG模块的设计与流片,所以以下内容只做参考。我们假定滤毛刺时钟为100M,需要滤除的复位抖动为30ns以下的信号。

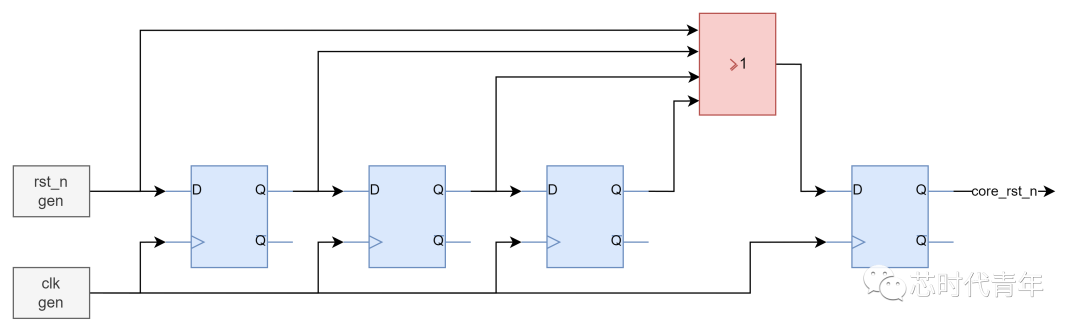

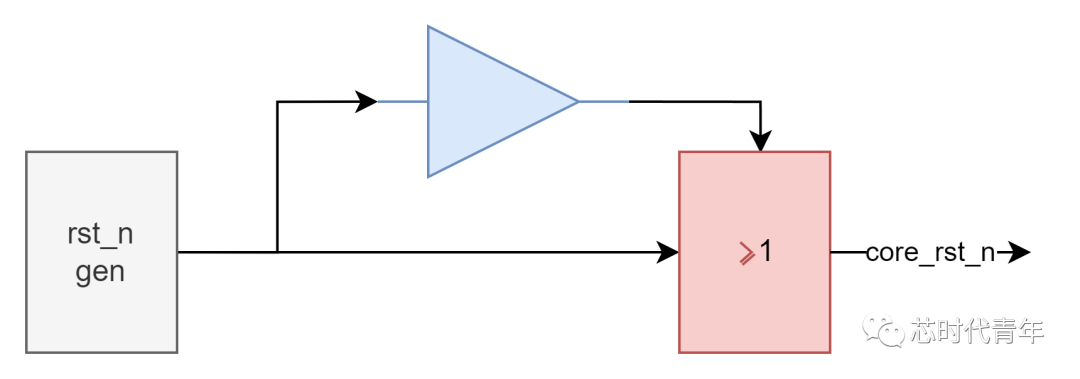

第一种方式通过滤毛刺时钟+D触发器来完成 ,如要滤过30ns的抖动电路图如下:

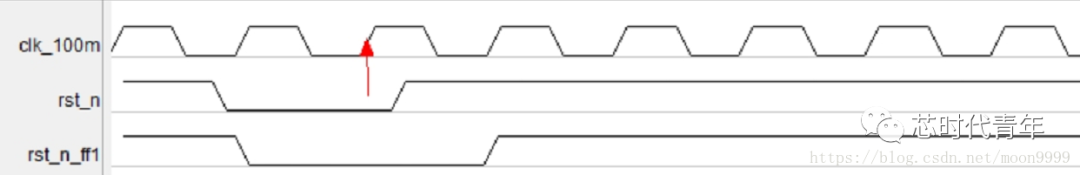

D触发器的数量关系是如何得到的呢?先假设我只有一个延时D触发器,那么复位信号必须维持L电平在一个clk时钟周期以上或门才能在时钟沿处打出一个L信号出来(即时钟上升沿时rst_n || rst_n_ff1 == 1'b0),如下面的波形图所示:

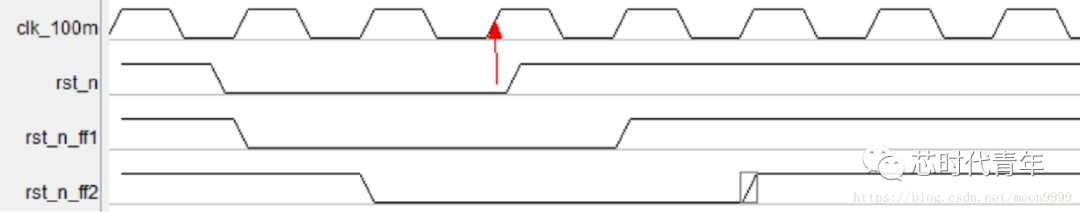

同样的,如果有两个延时D触发器,那么复位信号必须维持L电平在两个clk时钟周期以上,或门才能在时钟沿处打出一个L信号出来:

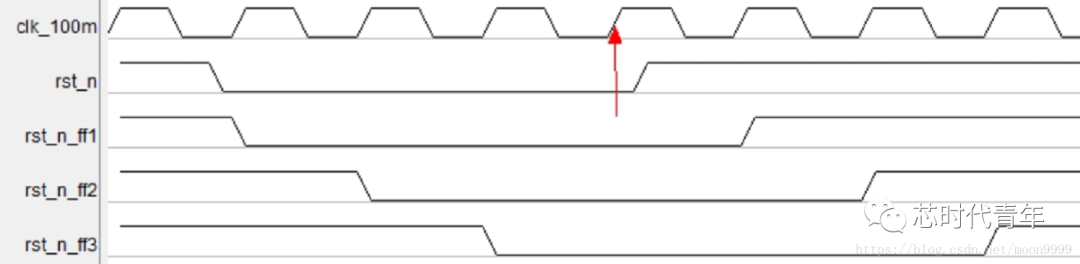

如果有三个延时D触发器,那么复位信号必须维持L电平在三个clk时钟周期以上,或门才能在时钟沿处打出一个L信号出来:

因此,在或们前放置了N个延时D触发器,就可以滤除N*T(T为消抖时钟的周期)时长以下的复位毛刺信号。这种方式存在一个巨大隐患,消抖时钟信号是不受复位控制的,一旦消抖时钟信号出了什么问题,复位信号将永远无法从消抖电路传递出去。

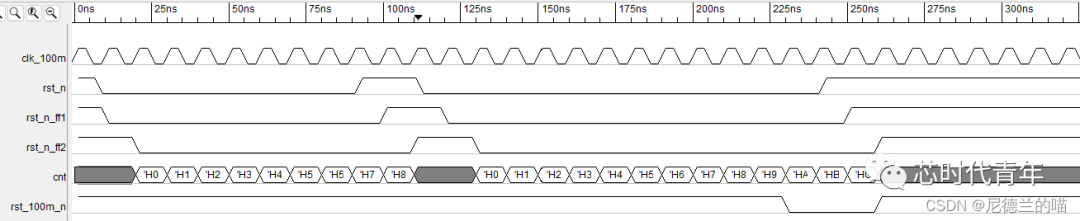

第二种方式通过累加器来完成, 简单来说就是数一下rst_n连续出现了多少拍,假如需要通过100M消抖时钟来滤除100ns以下的复位抖动,那么rst_n要连续出现10拍低电平才达到100ns的复位标准。将rst_n打两拍rst_n_ff1/rst_n_ff2消除亚稳态,当rst_n_ff2持续达到10拍对外输出复位信号,对应的波形示意如下:

简单的代码示意如下:

reg rst_n_ff1, rst_n_ff2;

reg [3:0]vcnt_100m;

always @(posedge clk_100m) begin

rst_n_ff1 <= rst_n;

rst_n_ff2 <= rst_n_ff1;

end

wire vcnt_100m_clr = (rst_n_ff1 != rst_n_ff2);

always@(posedge clk_100m) begin

if(vcnt_100m_clr)

vcnt_100m <= 4'h0;

else if(!rst_n_ff2)

vcnt_100m <= vcnt_100m + 1'b1;

end

always@(posedge clk_100m) begin

rst_100m_n <= (!rst_n_ff2 & vcnt_100m >=4'd9) ? 1'b0 : 1'b1;

end

这个消抖方案呢同样存在上面的问题,消抖时钟信号是不受复位控制的,所以在芯片内的模块级别可能会被采用,但是在外部复位消抖时是一般不会使用的。

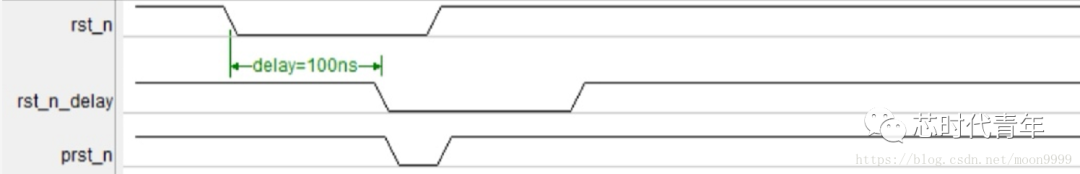

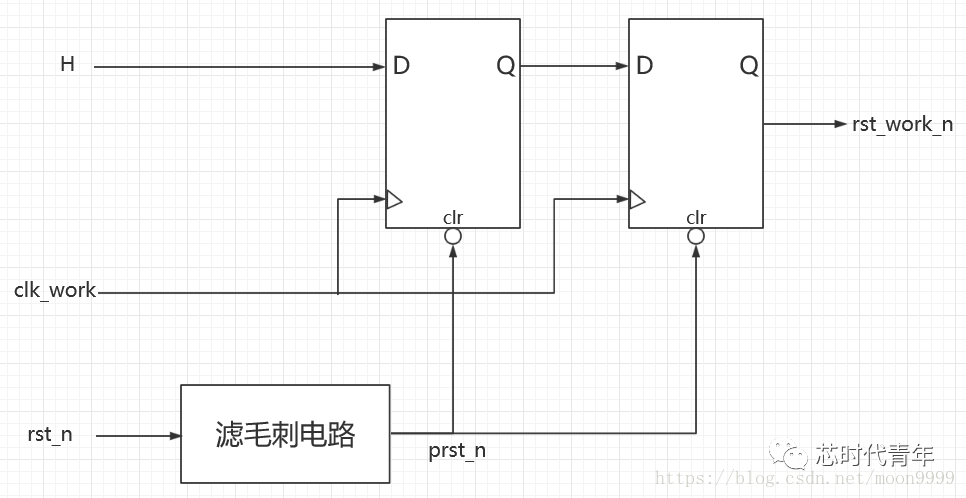

第三种方式是通过延时器件来实现 ,要滤去100ns以下毛刺,那么就引入100ns延时器件,组成如下电路:

对应的波形也很简单:

通过波形可以看出,如果复位时长不够100ns,prst_n根本不会被触发。这个电路的隐患在于如何保证延时器件在不同温度等外部环境干扰下的延时准确性。

-

D触发器

+关注

关注

3文章

164浏览量

47915 -

延时器

+关注

关注

1文章

36浏览量

15099 -

CLK

+关注

关注

0文章

127浏览量

17165 -

累加器

+关注

关注

0文章

50浏览量

9455 -

消抖电路

+关注

关注

0文章

6浏览量

8587

发布评论请先 登录

相关推荐

复位消抖电路具体长什么样子呢?

复位消抖电路具体长什么样子呢?

评论