摘要:选取了一种半烧结型银浆进行粘接工艺研究,通过剪切强度测试和空洞率检测确定了合适的点胶工艺参数,并进行了红外热阻测试和可靠性测试。结果表明,该半烧结型银浆的工艺操作性好,烧结后胶层空洞率低;当胶层厚度控制在30μm左右时,剪切强度达到25.73MPa;采用半烧结型银浆+TSV转接板的方式烧结功放芯片,其导热性能满足芯片的散热要求;经过可靠性测试后,烧结芯片的剪切强度没有下降,具有较高的稳定性和可靠性,可用于晶圆级封装中功率芯片的粘接。

关键词:晶圆级封装;半烧结型银浆;剪切强度;导热性能;可靠性度;导热性能;可靠性

1

引言

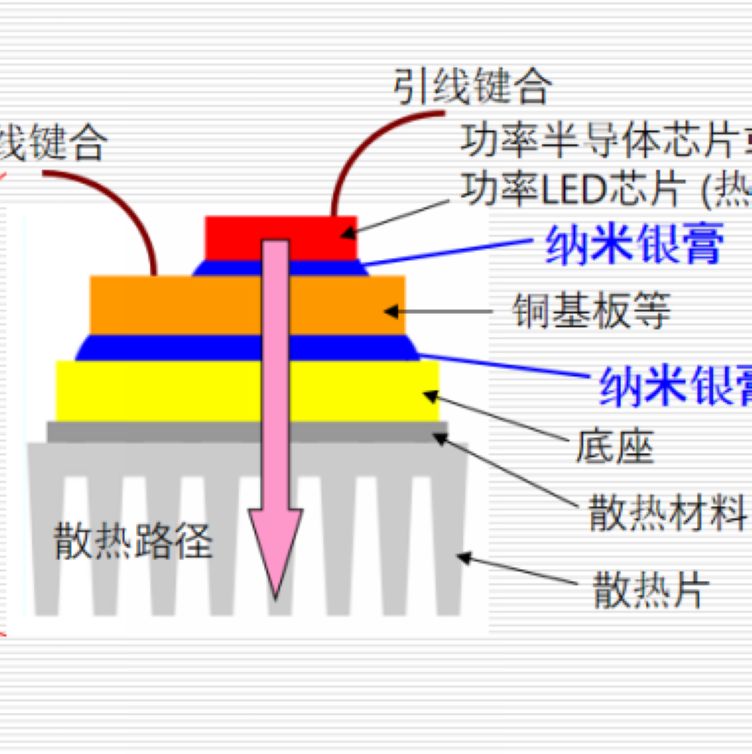

随着射频微系统技术在信息技术、生物医疗、工业控制等众多领域的应用越来越广泛,对更高集成度、更高性能、更高工作频率、更低成本的多通道多功能器件的需求也更加迫切。传统器件由于其本身的物理极限难以实现进一步的突破,因此当前在封装层面提高器件的集成度就变得越来越重要。晶圆级封装是一种先基于硅通孔(ThroughSiliconVia,TSV)技术制造硅基转接板,再集成GaN、GaAs等化合物多功能芯片和SiCMOS控制芯片,将化合物芯片、SiCMOS芯片与TSV转接板进行三维堆叠的先进封装技术,是促进射频微系统器件低成本、小型化与智能化发展的重要途径。

传统Si芯片与GaAs芯片通过导电银浆进行晶圆级封装的技术已应用到实际生产中,相关全自动贴装设备、固化设备以及工艺技术、可靠性等都已有相当成熟的配套与研究。但随着以SiC、GaN为代表的第三代半导体单片微波集成电路(MMIC)器件在高温大功率场景中的快速应用,苛刻的服役条件对功率芯片的互连提出了更高要求:一方面要求互连材料本身具有良好的导热性能,另一方面要求在进行长时间高温服役时具有高可靠性。普通导电银浆的导热性较差,在高温下使用会因热疲劳效应导致连接强度下降,可靠工作温度低,已不能满足功率芯片互连的应用要求。因此,急需寻找既能低温烧结高温服役,又能兼容现有贴装、固化设备的新型连接材料。

近年来,纳米Ag颗粒烧结银浆在电子封装中表现出良好的应用前景。此类银浆大多为全烧结型,主要成分通常为纳米级Ag颗粒、微米级Ag颗粒以及分散剂等有机溶剂,其黏度、触变指数等性能与普通导电银浆相差不大,完全可使用现有的晶圆级全自动贴装设备和固化设备。烧结后有机溶剂分解挥发,连接层几乎为纯银,具有很高的热导率、良好的导电性、优异的抗腐蚀性及抗蠕变性。然而已有研究发现,Ag纳米颗粒容易发生电化学迁移,银烧结层长时间高温服役时组织容易发生孔隙聚集并失效;对于镀金界面,即使连接层的初始性能优良,但由于Ag-Au之间的强烈互扩散,在长时间高温服役的过程中性能也会迅速下降。为提高长时间高温服役的可靠性,国外已有机构研制了半烧结型银浆,增加了环氧树脂含量,使其性能和烧结后状态介于全烧结型银浆与普通导电银浆之间。文中选取了一种半烧结型银浆进行粘接工艺研究,通过掌握该银浆的工艺操作性,确定出合适的粘接工艺参数,并测试其导热性能和可靠性,以期能够用于晶圆级封装中功率芯片的粘接。

2

试验方法

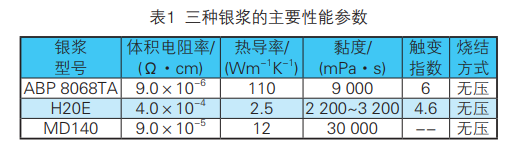

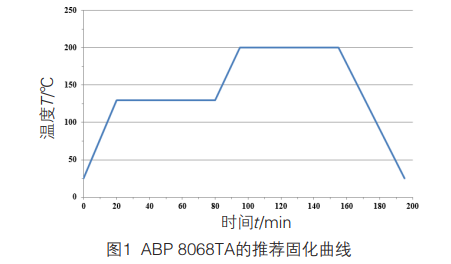

经广泛调研,选取了德国Henkel公司生产的一款型号为ABP8068TA的半烧结型银浆,主要性能参数见表1。可以看出,半烧结型银浆ABP8068TA的导电性和导热性远高于导电银浆H20E和MD140,但黏度介于两者之间,触变指数相差不大,因此可使用现有的晶圆级全自动贴装设备。推荐的固化曲线如图1所示,烧结温度为200℃,可使用现有的固化设备。

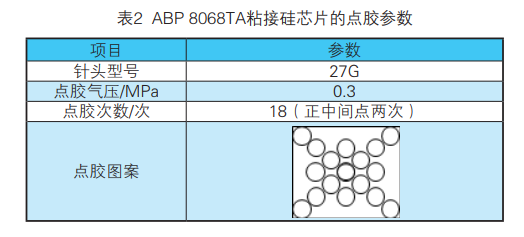

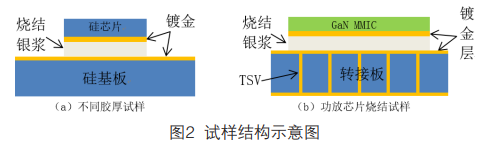

制备试样使用的硅芯片尺寸为2.3mm×1.96mm×0.25mm,背面电镀金,厚约8.5μm;使用的硅基板尺寸为14.5mm×13.5mm×0.725mm,表面电镀金,厚约3.5μm。采用半自动点胶机进行点胶贴片,点胶参数见表2。通过控制单个胶点的点胶时间,制备不同胶层厚度的试样,制备的试样如图2(a)所示。采用厌氧烘箱按图1所示的固化曲线进行烧结;通过X-ray检测烧结后的胶层状态和空洞率;采用推拉力测试仪进行剪切强度测试。

采用半烧结型银浆+TSV转接板的方式烧结GaN功放芯片,粘接试样如图2(b)所示,测试其导热性能是否满足芯片的散热要求,并与Au80Sn20共晶合金+无氧铜载体的烧结工艺进行对比。所选GaN功放芯片的型号为WFDN080120-P41-5,尺寸为2.5mm×1.6mm×0.08mm,背金厚约6.0μm,频率8~12GHz,热耗14.5W;TSV转接板和无氧铜载体的尺寸为2.5mm×3.0mm×0.2mm,TSV转接板表面电镀金,厚约3.5μm。将试样装配到管壳里,再进行金丝互联,完成整个测试样件的制备。

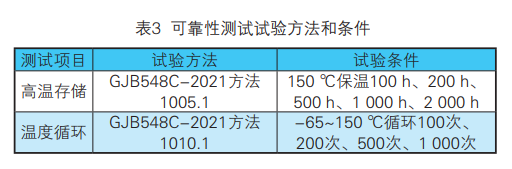

通过可靠性测试验证半烧结型银浆在实际工作中的性能变化,可靠性测试的试验方法和条件见表3。通过SEM观察界面形貌,采用推拉力测试仪进行剪切强度测试。

3

试验结果与分析

2.1 剪切强度及空洞率测试结果

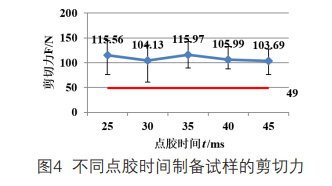

根据GJB548C-2021中方法2019.3规定:按2倍力曲线判断,若附着区面积大于4.13mm2,被试件承受的最小作用力应为49N;若附着区面积小于或等于4.13mm2,被试件承受的最小作用力应为12.2N/mm2。

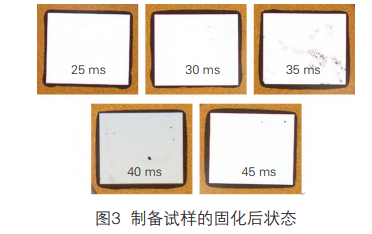

图3所示为不同点胶时间制备试样的固化后状态,满足目检要求,且银浆没有过分溢出。图4所示为制备试样的剪切力,并标示了剪切力的极差范围。可以看出,所有试样的剪切力都能满足GJB548C-2021中的规定。同时还可以看出,试样的剪切力随点胶时间的增加,变化并不明显。点胶时间越长,胶量越多,胶层相应越厚,因此可以推断:在一定范围内,胶层厚度对剪切力影响不大,这将会大大提高工艺窗口宽度;当点胶时间为35ms时,剪切力最大,为115.97N,即剪切强度为25.73MPa,对应的胶层厚度约为30μm,如图5(a)所示。由于划片后胶层边缘不易分辨,因此测量的是包含硅芯片与硅基板镀金层的尺寸,镀金层总厚度约为12μm。半烧结型银浆ABP8068TA的黏度较小,触变指数较大,硅芯片放置后在自身质量的作用下,就已能够将银浆缓慢挤出,保证了胶层厚度的一致性以及溢胶的充足。从图5(b)的X-ray检测照片也可以进一步确认,胶层内部均匀一致,几乎无空洞存在。

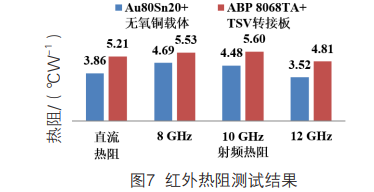

2.2红外热阻测试结果

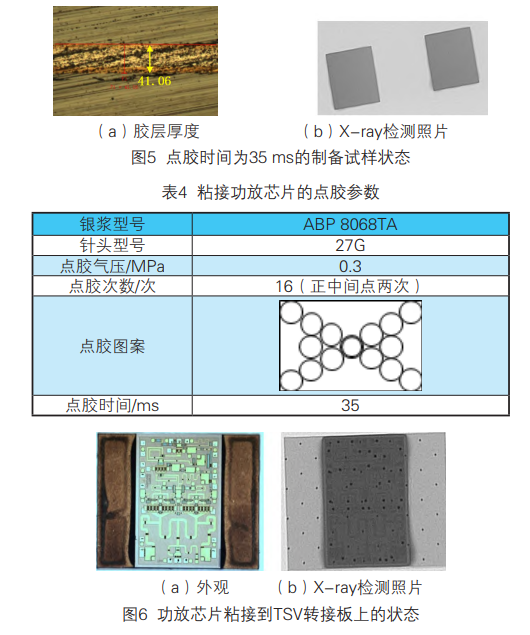

采用半自动点胶机进行功放芯片的粘接,点胶参数见表4。功放芯片粘接到TSV转接板上的外观状态和X-ray检测照片如图6所示。可以看出,芯片粘接平整,无明显倾斜;芯片四周溢胶充足,且无银浆上翻至芯片表面造成污染、短路;粘接轮廓面光滑无孔洞、无裂纹;胶层内部均匀一致,几乎无空洞存在;完全满足射频微系统对功率芯片装配的要求。

图7所示为采用两种烧结方式的红外热阻测试结果。可以看出,采用半烧结型银浆ABP8068TA将功放芯片烧结到TSV转接板上的方式时,热阻值为5±1℃/W,满足芯片的散热要求。但相较于采用Au80Sn20共晶合金将功放芯片烧结到无氧铜载体上的方式,热阻增大了约1℃/W,表明半烧结型银浆ABP8068TA+TSV转接板方式的散热能力略差于传统的金锡共晶+无氧铜载体方式。这可能是因为半烧结型银浆在烧结时,由于环氧树脂的存在,无法像全烧结型银浆那样使连接层为纯银,因此在一定程度上降低了导热性能。

2.3界面组织及可靠性测试结果

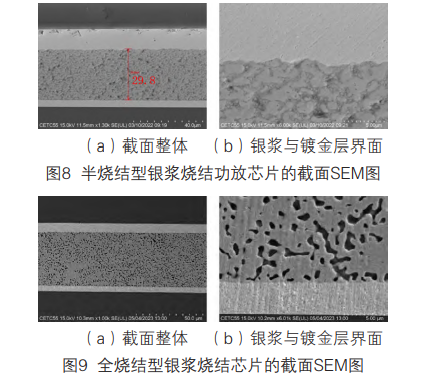

烧结银浆的低温烧结机理为:银浆中含有的纳米金属颗粒通过其高表面能在低温下经过互相扩散、长大形成相对致密的连接层,同时纳米金属颗粒与两侧的镀层金属或者基体金属也通过固态扩散形成界面冶金结合。因此,烧结银浆可以在较低的温度下通过无压烧结形成牢固连接。图8所示为采用半烧结型银浆ABP8068TA烧结功放芯片的截面SEM图。图9所示为采用全烧结型银浆烧结芯片的截面SEM图。由图8可以看出,银浆在烧结过程中发生了致密化行为,形成了良好连续的致密体,厚度约30μm,与划片测量一致;不同于图9中银颗粒烧结后形成的多孔性结构,半烧结型银浆烧结后,银颗粒并没有完全连接到一起,而是形成更大尺寸的银颗粒,通过交叉排布形成紧密连接;环氧树脂填充到银颗粒之间的缝隙中,使连接层整体的孔隙率降低;界面处的银颗粒与镀金层通过原子扩散形成了良好的冶金结合,结合紧密,没有裂纹。因此,烧结后的连接层能够为功率芯片的机械强度和导电导热提供可靠保障。

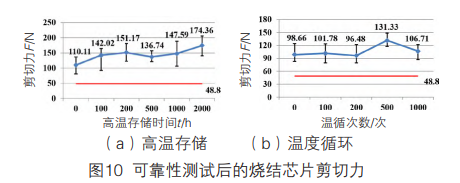

功率芯片在工作时会较长时间处在较高温度下,这就需要半烧结型银浆在进行长时间高温服役的过程中具有良好的稳定性和可靠性。图10所示为采用半烧结型银浆ABP8068TA烧结功放芯片经过可靠性测试后的剪切力。由图10(a)可以看出,随着存储时间的增加,烧结芯片的剪切力整体呈缓慢上升趋势,都高于存储前的剪切力;这种变化趋势可能是经过一定时间的高温存储后,银浆中残存的有机物得以进一步分解挥发,银颗粒继续扩散、长大,使烧结孔隙进一步减少,致密度提高;同时银浆中的银原子持续扩散到芯片与基板镀金层中形成冶金结合,从而使连接强度得以提高。由图10(b)可以看出,随着温循次数的增加,烧结芯片的剪切力变化不明显,原因可能在于烧结后,连接层银颗粒之间存在的微小孔隙被环氧树脂填充,使连接层弹性模量降低,这有利于应力的释放,因此在较强的热应力作用下仍能保持较好的连接强度稳定性。

4

结论

1)半烧结型银浆ABP8068TA的工艺操作性好,工艺窗口宽;烧结芯片的剪切强度达到25.73MPa,且胶层内部均匀一致,空洞率低;可使用现有的晶圆级全自动贴装设备和固化设备,满足晶圆级全自动大批量装配的应用需求。

2)半烧结型银浆+TSV转接板方式的导热性能满足功率芯片的散热要求;经过可靠性测试后,烧结芯片的剪切强度没有下降,具有较高的稳定性和可靠性,可用于晶圆级封装中功率芯片的粘接。

来源:电子工艺技术

作者:李志强,胡玉华,张 岩,翟世杰

中国电子科技集团公司第五十五研究所

-

芯片

+关注

关注

459文章

51649浏览量

430368 -

晶圆

+关注

关注

52文章

5034浏览量

128688 -

封装

+关注

关注

127文章

8181浏览量

143947

发布评论请先 登录

相关推荐

碳化硅SiC芯片封装:银烧结与铜烧结设备的技术探秘

150℃无压烧结银最简单三个步骤

降银的网版印刷技术:无网结搭接对银浆印刷形貌的影响与优化

半烧结型银浆粘接工艺在晶圆封装的应用

半烧结型银浆粘接工艺在晶圆封装的应用

评论