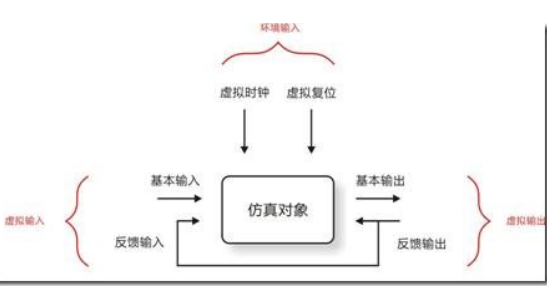

直接在modelsim软件内执行.do文件进行仿真,不通过vivado调用modelsim,vivado仅用于生成IP核。

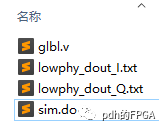

1.需要vivado软件安装路径下的glbl.v文件

路径举例:D:XilinxVivado2017.4dataverilogsrcglbl.v

2.需要编写sim.do文件

(1). sim.do文件包含了testbench.v文件.

(2).其他源代码.v/.sv文件.

(3).IP simnetlist.v文件,仿真IP核需要.

3.用一个文件夹,将该两个文件放同一目录下,如:

4.文件sim.do编写如下举例:

vlib work; vlog glbl.v Vlog ../../../duc_in_sel_module_5g/dds.v Vlog ../../../duc_in_sel_module_5g/duc_in_sel_module_5g.v Vlog ../../../duc_in_sel_module_5g/ip/complex_multiplier_sim_netlist.v Vlog ../../../duc_in_sel_module_5g/ip/IF_DDS_sim_netlist.v vlog -sv ../cpri_ctrl_nr/cpri_ctrl_nr_decomp_regroup.sv vlog -sv ../cpri_ctrl_nr/cpri_ctrl_nr_tx_data_regroup.sv vlog -sv ../cpri_ctrl_nr/cpri_ctrl_nr_tx_data_sel.sv vlog -sv ../testbench/tb_xxxx.sv vsim -t ps -novopt work.tb_xxxx glbl -L secureip -L simprims_ver -L unifast_ver -L unimacro_ver -L unisims_ver -L xpm log -r /*

以上编写完成

其中 ../ 为sim.do文件当前目录的上一级文件夹,../../ 则为上两级文件夹

IF_DDS_sim_netlist.v 就是vivado IP核生成以后,出来的仿真用.v文件

vlib work; 在sim.do文件夹目录下在创建一个work文件夹

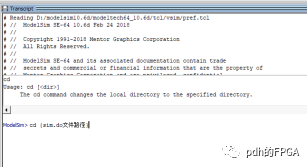

5.打开modelsim窗口

在gui界面输入

cd {sim.do文件路径}

{}中的内容就是sim.do文件的路径,绝对路径。

例如

cd {E:cpri_ctrl_topsim}

输入完成以后,直接输入 do sim.do 指令

即可

审核编辑:刘清

-

Xilinx

+关注

关注

73文章

2208浏览量

131978 -

Vivado

+关注

关注

19文章

860浏览量

71427 -

MODELSIM仿真

+关注

关注

0文章

15浏览量

7735

原文标题:单独使用modelsim仿真xilinx

文章出处:【微信号:pdh的FPGA,微信公众号:pdh的FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何在ModelSim中添加Xilinx仿真库

安富利GSM给您说说ModelSim仿真XILINX库添加

Xilinx ISE 12.2 调用Modelsim进行行为仿真详解

减少Xilinx Ise与Modelsim联合仿真的错误方法

Xilinx ISE是如何调用ModelSim进行仿真的

仿真软件ModelSim及其应用,ModelSim的仿真流程

Modelsim仿真教程Modelsim的基础入门基础教程免费下载

怎样单独使用modelsim仿真xilinx呢?

怎样单独使用modelsim仿真xilinx呢?

评论