1、什么是状态机建模

状态机建模是使用状态图和方程式的手段,创建基于混合信号的有限状态机模型的一种建模工具。

状态图具有强大的视觉特征,在设计的早期阶段,使用状态图能够将复杂的系统行为抽象为更高层次的模型,而状态机建模工具具有将基于行为状态模型与系统关联起来的独特功能。

状态机建模工具可以生成基于MAST、VHDL-AMS和Verilog-A语言的仿真模型。使用状态机建模工具不需要系统的训练,不需要懂专业的建模语言语法,上手非常容易。

状态机建模工具主要应用于:电源控制管理或电路控制、离散时间控制、事件控制等场合。

2、状态机建模工具介绍

打开SaberRD,在Model标签栏下单击状态机建模按钮,进入建模界面。

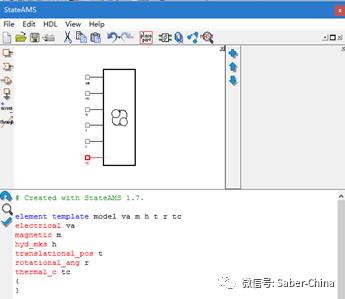

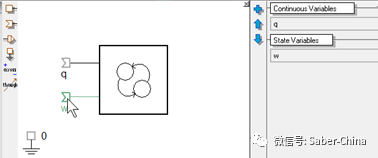

如上图所示,状态机建模界面可分为三部分:拓扑编辑区,变量编辑区和状态图编辑区。

l 拓扑编辑区:定义模型接口及接口属性;

l 变量编辑区:定义与模型相关的变量

l 状态图编辑区:定义模型内部各个变量之间的逻辑关系及使用公式对变量进行行为描述

2.1. 拓扑编辑区

进行状态机建模首先需要定义状态机拓扑,包括定义状态机的接口,及接口属性。

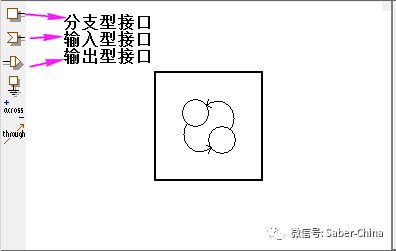

接口有三种类型:分支型,输入型,输出型。当定义的接口为输入或输出端口时,对应在右侧变量区域会有相同名称的变量生成;当接口定义为分支型接口时,该接口包含through和across型变量。

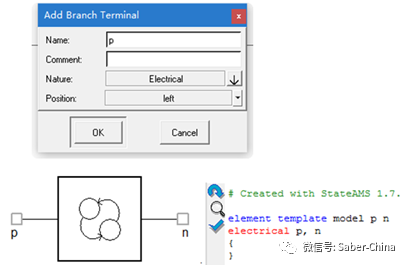

2.1.1. 分支型终端

分支型终端可以使得系统内部各元素之间进行能量的交换,遵循能量守恒定律。能量的端口类型包括:电,磁,机械,热。每一种分支型端口包含一对跨接(across)和(导通)through型变量,如电类型端口包含电压和电流两种信息。电压大小代表潜在驱动能力,而导通型变量电流表示流量的大小。分支型终端可以是差分形式或者是单端形式。

下图是几种分支型终端的类型定义。

2.1.2. 输入/输出端口定义

输入端口和输出端口功能类似,下文表述以输入端口为例,对于输出端口同样适用。

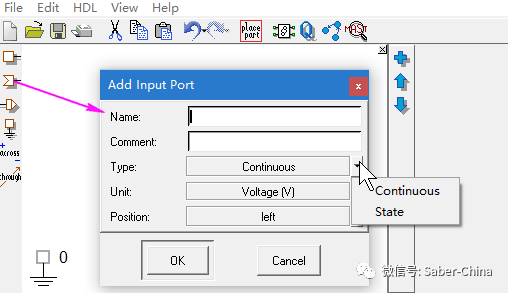

输入端口不包含能量守恒信息,用于多算法控制或者逻辑控制,变量类型分别对应Continuous和State,如下图所示。Continuous变量是连续变量,用于基于时间的算法控制,State是状态变量,用于基于事件驱动的控制。

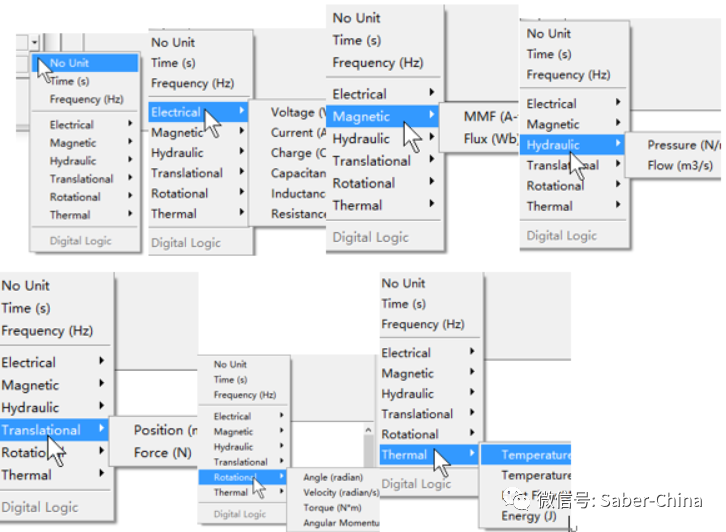

输入输出端口的单位有多种类型,如下图所示。对于控制类的,多使用无单位的。

输入输出端口定义好后,对应的在右侧变量区会出现相同名称的变量,如下图所示:

2.2. 变量编辑

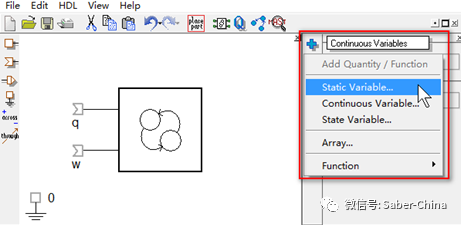

定义好接口拓扑后,下一步就是定义模型中需要用到的变量。包括静态变量,连续型continuous和状态型state变量。同时还可以定义数组,和函数。

2.2.1. 静态变量 Static

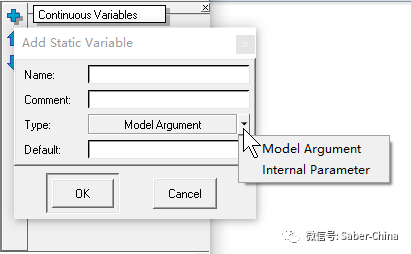

静态变量是指在整个瞬态仿真过程中,变量参数不变。定义静态变量时,需要注意区分是模型参数还是内部参数。如下图所示。

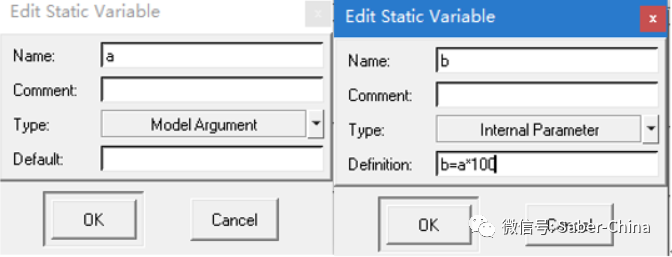

模型参数就相当于定义模型的外部参数,变量值在模型初始化时可以参量化设置。

而内部参数多是通过一个表达式由其他模型参数计算而来。

例如定义了一个模型变量a,再定义一个内部参数静态变量b,b=a*100,定义式如下图所示:

2.2.2. 连续型变量

连续型变量用在基于连续时间状态的仿真应用中。一般使用等式进行赋值。状态机变量中包括的类型有4种:

n 分支型连续变量(包含一对跨接(across)和(导通)through型变量)

n 输入型连续变量(控制型输入变量)

n 内部连续变量

n 输出连续变量(控制型输出变量)

2.2.3. 状态型变量

状态型变量用于基于事件驱动的离散时间仿真应用中。状态型变量一般在state exit,state entry,initial actions时进行赋值。

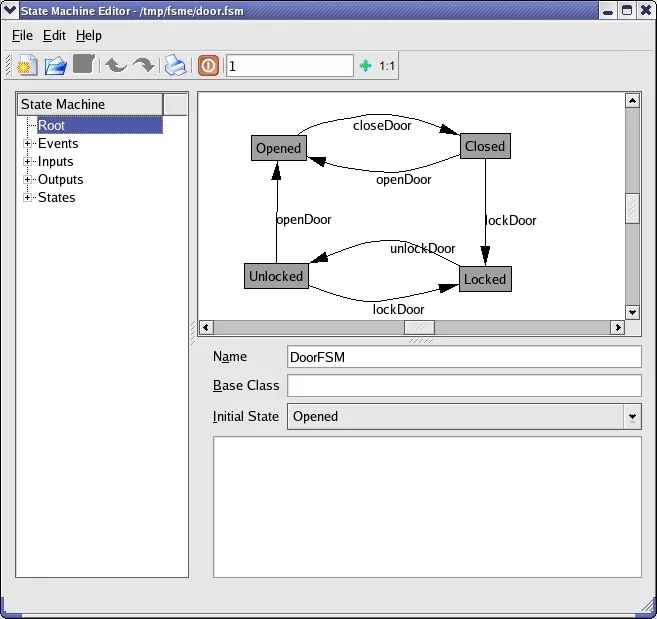

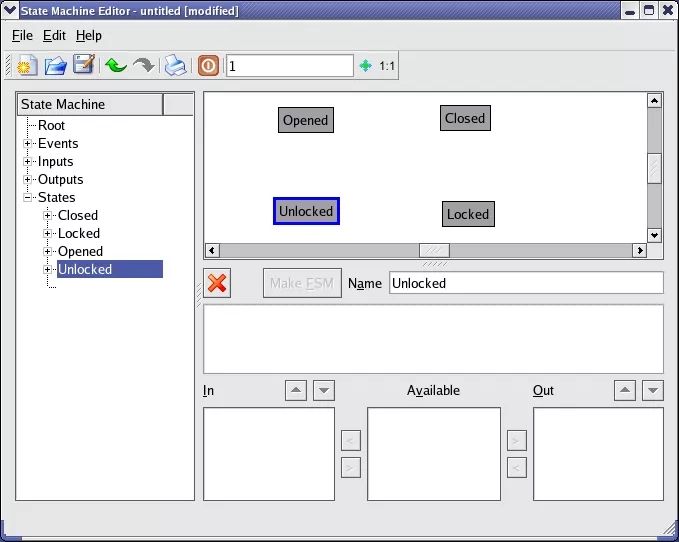

2.3. 状态机状态图编辑

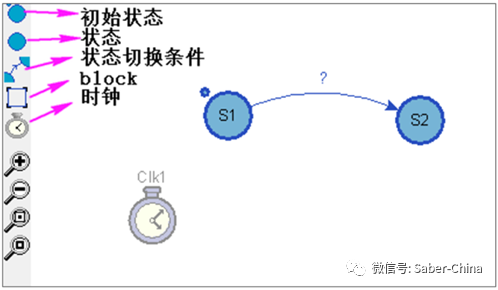

状态机状态图编辑包含:States、Transitions、Blocks、Clocks

2.3.1. States

states本质上说是一个布尔型变量,它的状态可以是激活和非激活状态。

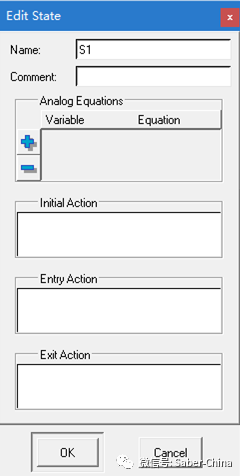

Ø AnalogEquation:连续型变量的赋值或state变量赋值

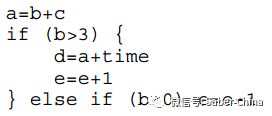

可以赋值基于连续变量的公式continuous variable equation如:a=b+c等价于b+c;a=b*cos(a);b+c

可以赋值state equation

Ø Initial/Enty/Exit :state型变量赋值,只能给内部或输出state variables赋值。Initial在做DC分析时使用,Entry:状态激活时赋值;Exit:状态退出时赋值内容。

赋值形式variable = expression。

允许使用if-else语句。例子:

Processes 进程

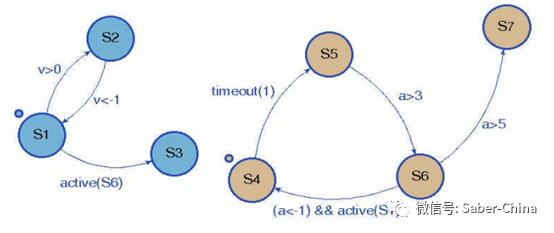

进程概念允许并发激活状态。单个进程是一组不能同时激活的独占状态,但是处于不同进程的状态可以同时激活。如下图所示是一个2个进程状态机。共有状态3*4=12个状态。

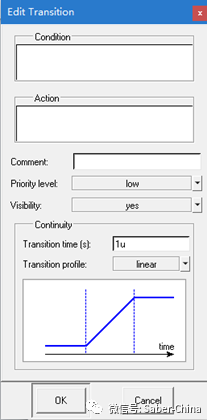

2.3.2. Transitions

定义状态之间切换的条件及过程。条件是一个布尔型结果或变量

l Transition condition:>, <, <=, >=, &, |, ==, =, !=, timeout, active, event_on (note that == and = are equivalent)

n timeout function定义一个关于时间的公式,超过这个时间,就会触发状态变化。timeout(1)&&(a>b) becomes true whenever "a" becomes greater than "b" after one second has elapsed since state entry

n active function:使用states的名称作为参数,用于进程之间的跳变

n event_on function:state变量作为参数,event_on(clk)&&(clk==’1’)

l Transition action:(after any state or block exit actions and before any state or block entry actions),规则同entry actions。

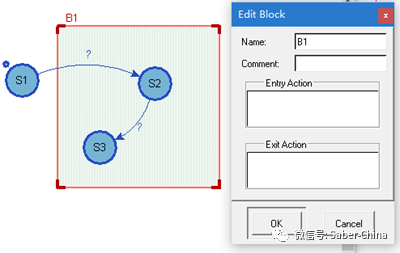

2.3.3. Blocks

允许多个states共享transition和actions

Block有Entry Action和Exit Action属性。设计规则与state 中的Action是一样的。如下,Block状态切换发生在从S1的Exit Action之后,S2的Enter Action之前。

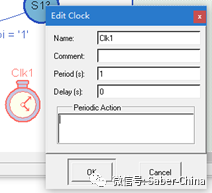

2.3.4. Clocks

Clock允许某些动作周期性的发生,但是与state是否激活无关。

-

VHDL语言

+关注

关注

1文章

113浏览量

18303 -

状态机

+关注

关注

2文章

493浏览量

27855 -

逻辑控制

+关注

关注

0文章

40浏览量

12480 -

静态变量

+关注

关注

0文章

13浏览量

6728

发布评论请先 登录

相关推荐

什么是状态机?状态机5要素

状态模式(状态机)

如何生成状态机框架

SaberRD状态机建模工具介绍(一)什么是状态机建模

SaberRD状态机建模工具介绍(一)什么是状态机建模

评论