本文来自“集成芯片与芯粒技术白皮书”,本文重点介绍了发展集成芯片和芯粒的重要意义。

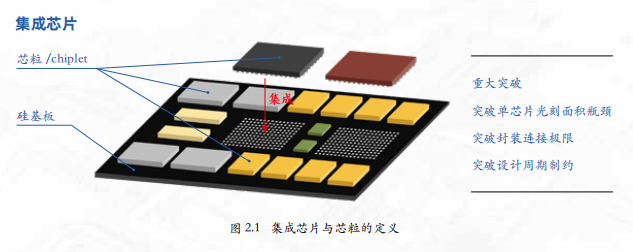

集成芯片是指先将晶体管集成制造为特定功能的芯粒(Chiplet),再按照应用需求将芯粒通过半导体技术集成制造为芯片。其中,芯粒(Chiplet)是指预先制造好、具有特定功能、可组合集成的晶片(Die),也有称为“小芯片”,其功能可包括通用处理器、存储器、图形处理器、加密引擎、网络接口等。硅基板(Silicon Interposer),是指在集成芯片中位于芯粒和封装基板(Substrate)之间连接多个芯粒且基于硅工艺制造的载体,也有称为“硅转接板”、“中介层”。硅基板通常包含多层、高密度互连线网络、硅通孔 (Through Silicon Via, TSV) 和微凸点 (Micro Bump),保证了电源、数据信号在芯粒之间和封装内外的传输,而且可以集成电容、电感等无源元件和晶体管等有源电路。

集成芯片的概念源于 2010 年台积电的蒋尚义博士提出的“先进封装”概念,他提出可以通过半导体互连技术连接两颗芯片,从而解决单芯片制造的面积上限,解决板级连接的带宽极限问题。而后,时任美国美满电子公司总裁的周秀文博士(Sehat Sutrardja)将“模块化”设计思想与方法进一步融入。

经过多年学术界和企业的发展,“先进封装”已无法涵盖多芯粒集成后所形成的新系统的科学与技术,于是在 2022 年自然科学基金委召开的双清论坛上,孙凝晖院士、刘明院士以及蒋尚义先生等我国学者在凝练相关基础技术后提出“集成芯片(Integrated Chips)”这一概念替代“先进封装”、“芯粒”等称谓,用于表达其在体系结构、设计方法学、数理基础理论、工程材料制造等领域中更丰富的含义。

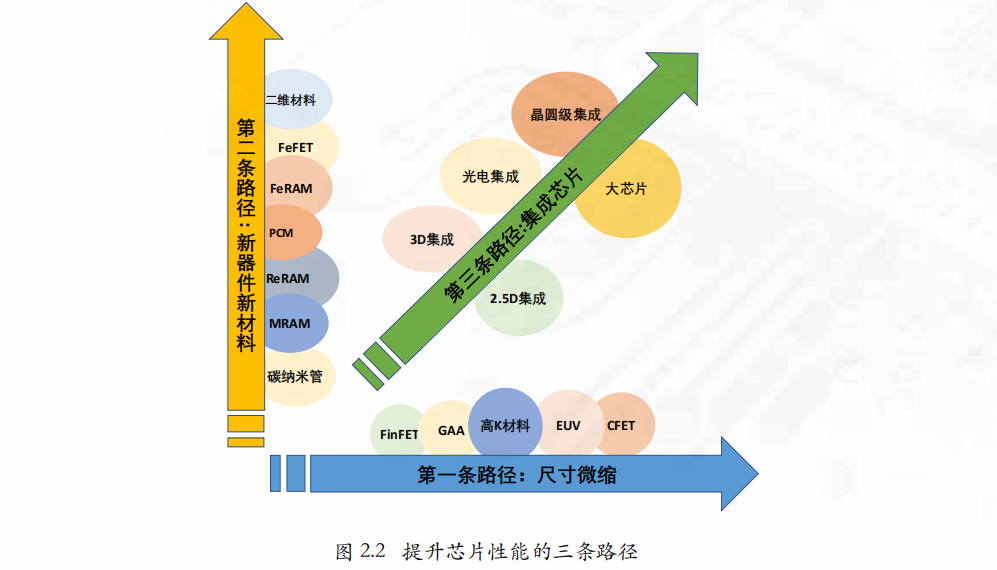

从技术上看,目前主要有三条提升芯片性能的发展路径,如图 2.2 所示,三条技术路径从不同维度共同推动集成电路的发展。

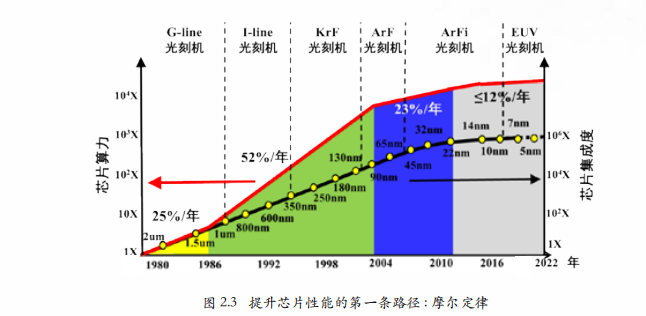

第一条路径是通过将晶体管的尺寸不断微缩实现集成密度和性能的指数式提升,也被称为遵循“摩尔定律”的发展路径。1965 年戈登·摩尔指出,集成电路的晶体管数目大约每 18-24 个月增加一倍。摩尔定律、登纳德缩放定律、以及同时期的体系架构创新,包括指令级并行、多核架构等,共同推动了芯片性能随工艺尺寸微缩的指数式提升。

随着集成电路工艺进入 5nm 以下,尺寸微缩接近物理极限,单纯依靠缩小晶体管尺寸提高芯片性能的空间变小,同时带来了成本与复杂度的快速提高。芯片散热能力、传输带宽、制造良率等多种因素共同影响,形成了芯片功耗墙、存储墙、面积墙等瓶颈,限制了单颗芯片的性能提升。可以说,摩尔定律的放缓已成为国际和我国集成电路发展的重大挑战。

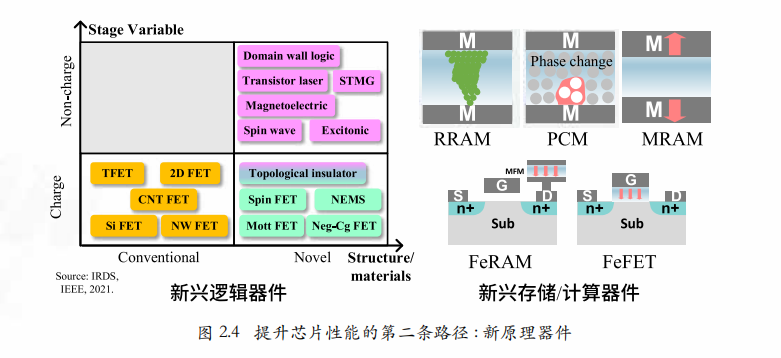

第二条路径是通过发展新原理器件,研发新材料,实现单个晶体管器件的性能提升。随着铁电存储器 FeRAM、阻变存储器 RRAM、磁存储器 MRAM、相变存储器 PCM、铁电晶体管 FeFET 等多种新原理器件的发展,结合宽禁带半导体、二维材料、碳纳米管等新材料的研究,探索超越传统CMOS 器件性能 / 能效的新型器件和突破冯诺依曼架构的新型计算范式成为一个重要的研究领域。然而,新原理器件是面向未来的芯片性能提升发展路径,从科学研究到实际应用的周期通常较长,难以在短时间内解决当前高性能集成电路芯片受限的挑战。

随着技术体系和产业生态逐渐构建,集成芯片将发展为芯片性能提升的第三条主路径。芯片的性能主要取决于芯片集成的晶体管规模,而晶体管规模又取决于芯片制造面积。集成芯片路径能够有效突破芯片制造的面积墙瓶颈。芯片的“面积墙”,是指单颗芯片的制造面积受限于***可处理的极限尺寸和良率。一方面,最先进的高性能芯片(如 NVIDIA H100 GPU 等)面积正在接近光刻面积极限。同时,单芯片良率随面积增长快速下降,在高成本的先进工艺下,该问题更加具有挑战性。集成芯片能够通过多颗芯粒与基板的 2.5D/3D 集成,突破单芯片光刻面积的限制和成品率随面积下降的问题,成为进一步提升芯片性能的可行路径。另外一方面,集成芯片技术是一条不单纯依赖尺寸微缩路线提升芯片性能的重要途径,在短期内难以突破自主 EUV ***和先进节点制造工艺的情况下,可以提供一条利用自主低世代集成电路工艺实现跨越 1-2 个工艺节点的高端芯片性能的技术路线。

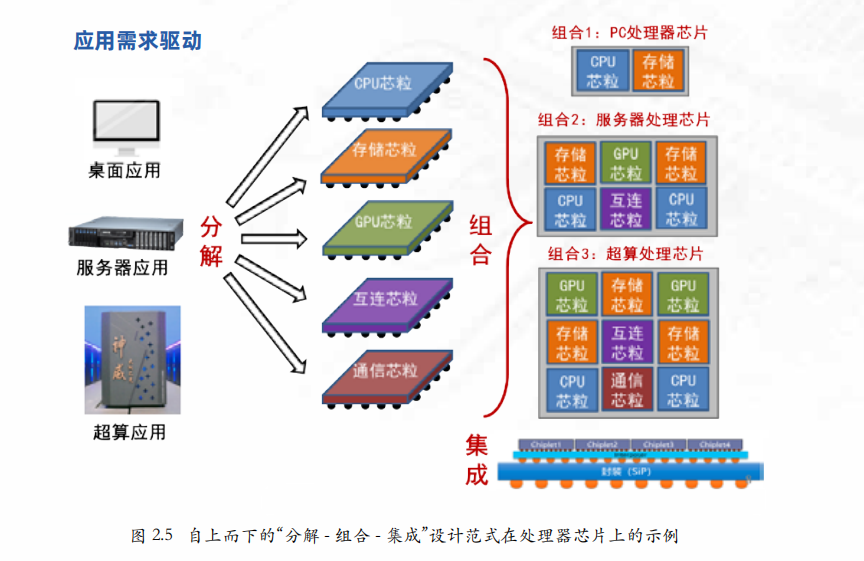

集成芯片采用系统工程学的原理,发展自上而下构造法的集成电路设计新范式。自上而下意味着芯片结构适配应用特征,自上而下采用“分解 - 组合 - 集成”的方法。根据应用特征,抽象分解成若干标准的芯粒预制件,将众多芯粒预制件,按照结构组合成不同应用领域的芯片,将芯片制造分解为芯粒预制件的制造和多芯粒集成。下例展示了处理器芯片采用集成芯片范式后的新流程:

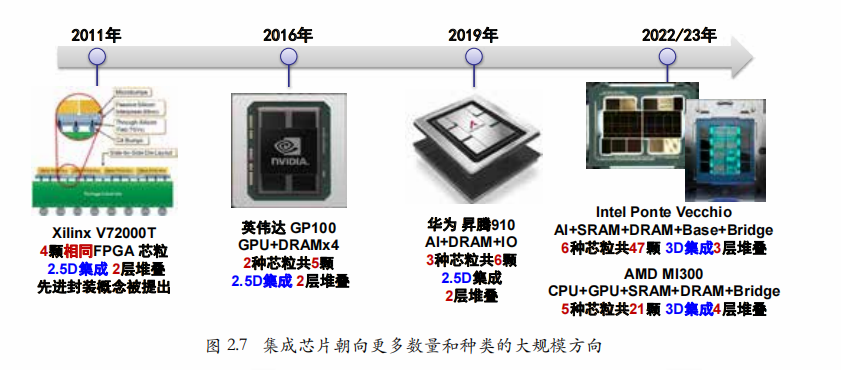

最早的集成芯片原型是由台积电与美国赛灵思(Xilinx)公司共同完成的一款大容量 FPGA 芯片V7200T,它将四个大规模的 FPGA 芯粒在一块硅基板(Interposer)上连接在一起,形成一个超过2000 个可编程逻辑门的系统。借助这一芯片的开发,台积电也完成了基于半导体工艺的芯片互连封装技术,称为 Chip-on-Wafer-on-Substrate(CoWoS)。目前这一技术作为 2.5D 集成芯片的代表性工艺,广泛的应用于高性能处理器芯片产品中。第一个采用 CoWoS 技术的处理器集成芯片是英伟达公司的 GP100 GPU 芯片,它的结构是通过 CoWoS 工艺将 GPU 芯粒和多个 HBM 芯粒在一个封装体内集成,最大化处理器与存储之间的通信带宽,硅基板尺寸超过 1 个光罩(858mm2)。我国华为海思公司设计的昇腾 910 芯片,也是基于这一技术将 3 种、6 个芯粒的集成,实现了高算力的人工智能处理器。

近年来,随着 TSV、铜 - 铜混合键合等工艺的成熟,3D 集成芯片成为了高性能处理器领域新的发展趋势。美国 AMD 和 Intel 公司均基于 3D 集成芯片技术,设计了面向超算的高性能超算处理器芯片。上述产品将将 6-8 种,超过 20 个芯粒的芯粒集成在一个系统中,最终实现了更大规模(千亿以上规模数量级晶体管)、更复杂的集成。在 2.5D 集成上,基于重分布层(Re-Distribution Layer)的扇出工艺(FanOut)可以实现更大规模的芯粒集成,美国 Tesla 公司基于 FanOut 工艺开发面向人工智能的训练处理器集成芯片 DOJO,RDL 基板的总面积达到 20000mm2,包含 25 个 D1 多核处理器芯粒和光电融合的通信芯粒。

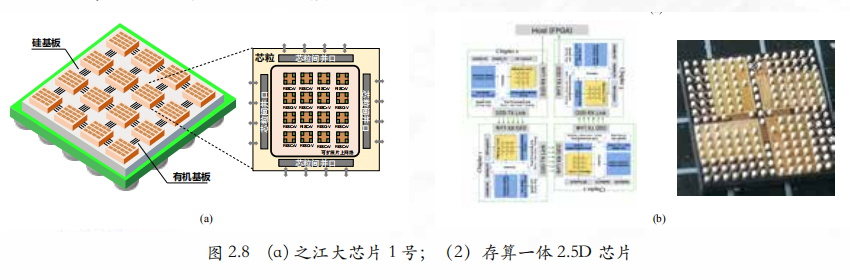

我国研发机构在高集成度上取得了进展。比较有代表性的包含,2022 年中科院计算所智能计算机中心和之江实验室联合开发了“之江大芯片一号”,该芯片成果集成了 16 个芯粒,每个芯粒含 16个 CPU 核,无论是集成的芯粒数和体系结构上的计算核心数,都实现了突破,从体系架构和设计方法学上,验证了利用集成芯片突破单处理器芯片的算力极限技术途径。目前,正在开展“之江大芯片二号”的工作,集成度和性能将进一步提升。

2022 年,复旦大学集成芯片与系统全国重点实验室基于集成扇出封装工艺实现了存算一体 2.5D 芯片,采用片间按层流水的可扩展架构实现了系统算力与存储规模的按芯粒比例的线性增长,避免了“一系统一设计”的高复杂度问题。此外,阿里达摩院联合紫光国芯研发基于 3D 混合键合工艺的智能加速器 -DRAM 堆叠集成芯片,豪威科技的采用三层堆叠工艺将图像传感器芯粒、模拟读出电路芯粒、图像信号处理与 AI 芯粒集成为一个组件,面向像素的不断提升,最小化芯粒间的通信开销。

集成芯片中,由于每个芯粒由不同的单位设计,因此接口的标准化是系统能够高效率组合的关键因素。在 Intel 的主导下,2022 年 3 月,通用高速接口联盟(UCIe)正式成立,旨在构建芯粒技术在芯片上的互联标准。

审核编辑:汤梓红

-

半导体

+关注

关注

339文章

31192浏览量

266356 -

存储器

+关注

关注

39文章

7753浏览量

172162 -

晶体管

+关注

关注

78文章

10434浏览量

148547 -

集成芯片

+关注

关注

1文章

262浏览量

20761

原文标题:集成芯片与芯粒(Chiplet)技术白皮书

文章出处:【微信号:AI_Architect,微信公众号:智能计算芯世界】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

EDA技术从何而来?EDA技术发展历程

封装天线技术发展历程回顾分析

新兴的半导体技术发展趋势

什么是集成无源元件?对PCB技术发展产生了什么影响?

集成电源是电源技术发展的必由之路

集成无源元件对PCB技术发展有什么样的影响

集成芯片的概念和技术发展路径

集成芯片的概念和技术发展路径

评论