编者注:在电路设计中时序是非常重要的,时序也是信号完整性研究的主要内容之一。较大的延时差/偏移(Skew)会直接导致电路时序不满足要求,从而导致产品设计失败。要控制好skew首先就需要学会如何获取skew,本文将介绍了两种方式供大家参考。

在2018年的时候给大家分享过一篇文章,介绍的是传输线的物理等长并代表在时序上就是相等的。这篇文章得到了大量工程师的一致好评。关于一些基本的概念,大家可以参考下文:

90%的工程师都没意识到的高速电路设计问题:等长绕线的影响

最近又有工程师在问:虽然我知道它们不等长了,但是我们如何计算这些skew呢?

在前文中有介绍过,在有的PCB设计工具中是直接可以查看传输线的延时以及延时差(skew)的,有兴趣的工程师可以去研究下。本文主要给大家分享下不使用PCB设计工具,如何计算传输之间的延时差。因为并不是每一个设计都是PCB,有的是连接器、有的是线缆或者芯片封装产品等等。

不管是PCB、芯片封装,还是连接器、线缆,在分析时都会提取其S参数。我们经常讲到,S参数能完整的表征无源器件的特性,其中也就包含了我们要介绍的延时差(skew),那这样就可以从S参数中获取得到传输线之间的延时差(Skew)。

下面介绍两种测量或者计算方式,一种是通过PLTS直接测量;一种是使用ADS仿真获取。

首先来介绍PLTS的测量方式。

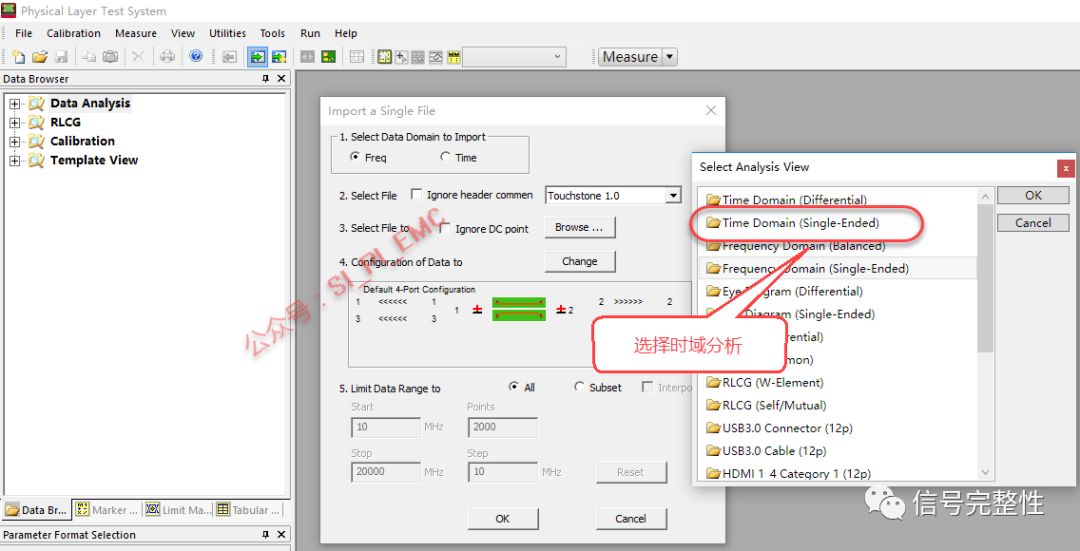

把获取到的S参数导入到PLTS中,如下图所示:

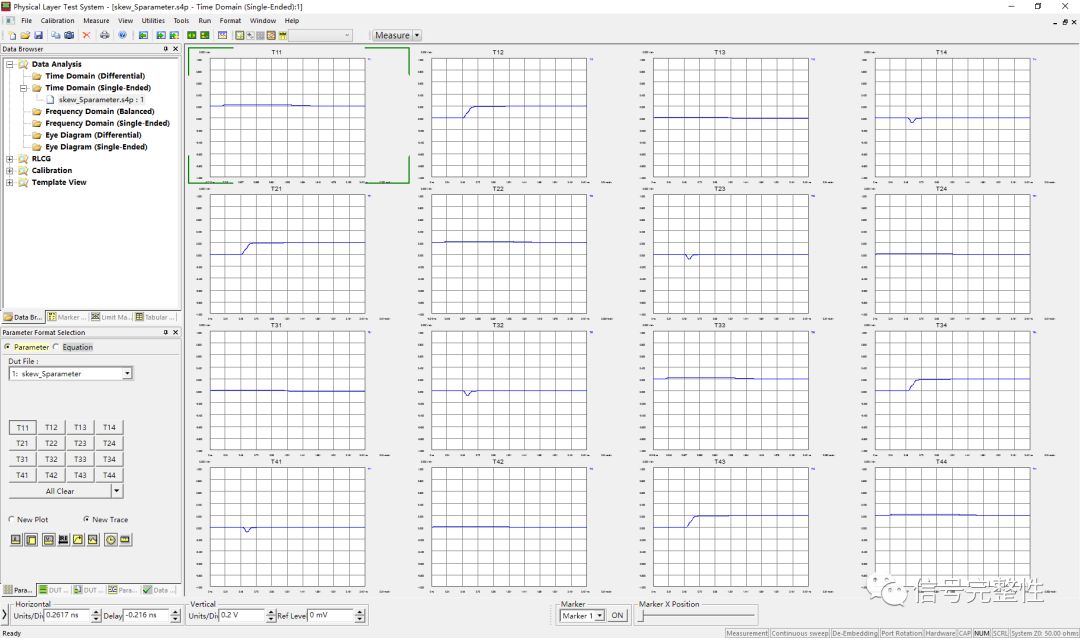

导入的S参数如下图所示:

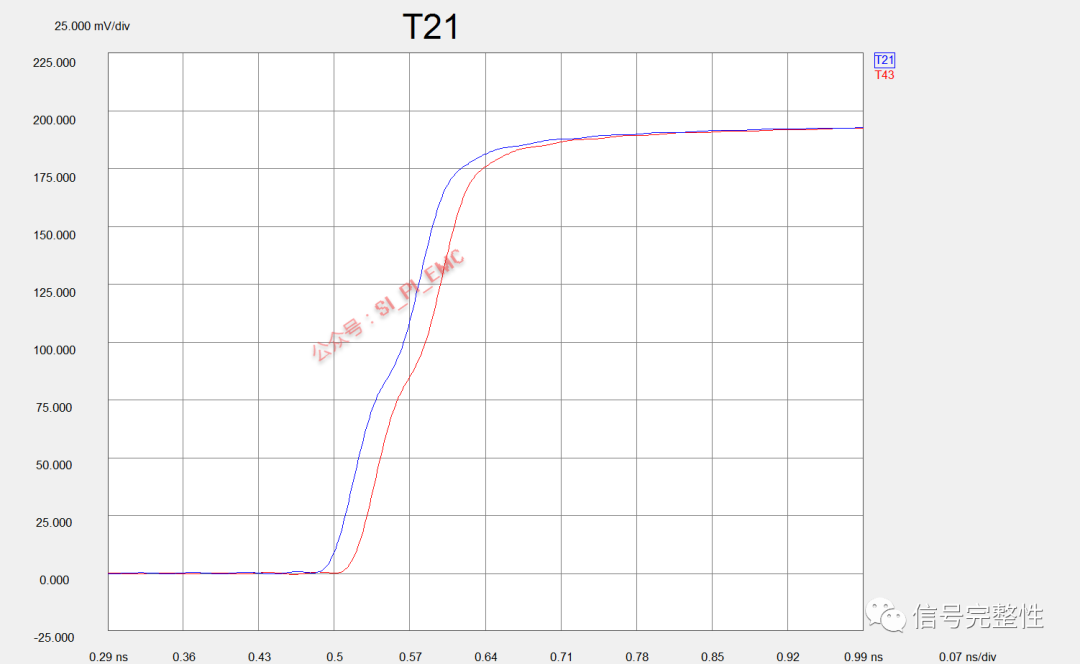

选择T21,双击之后,再选择T43,双击之后,如下图所示:

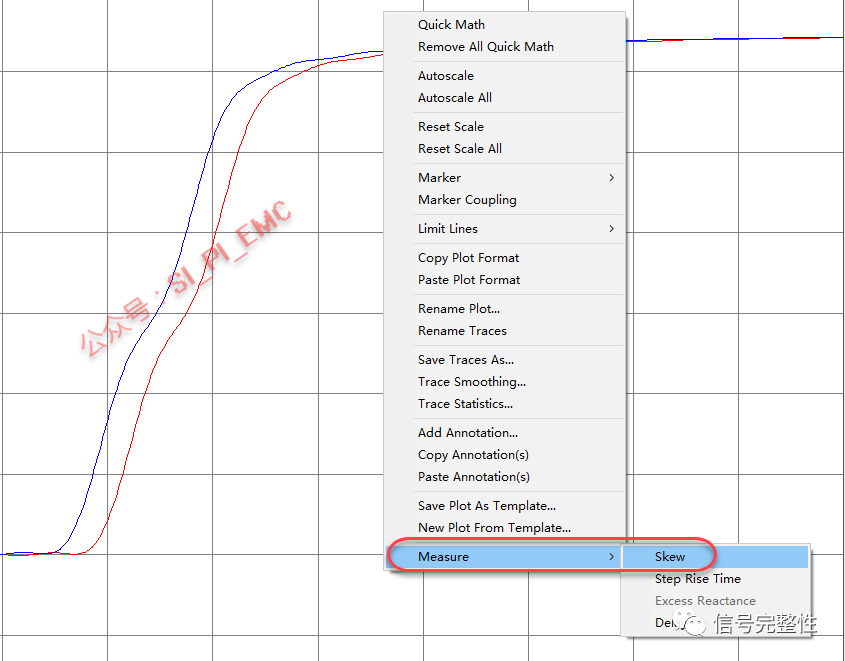

在图示中单击鼠标右键,选择Measure-->Skew

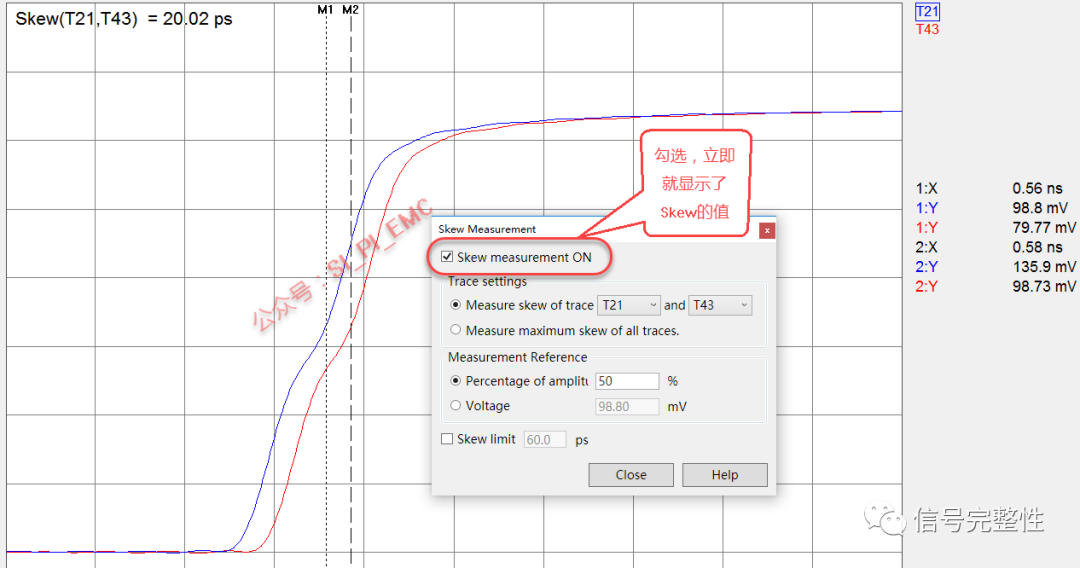

在弹出的对话框中勾选Skew Measurement ON,就会立即显示出延时差(Skew),为20.02ps。

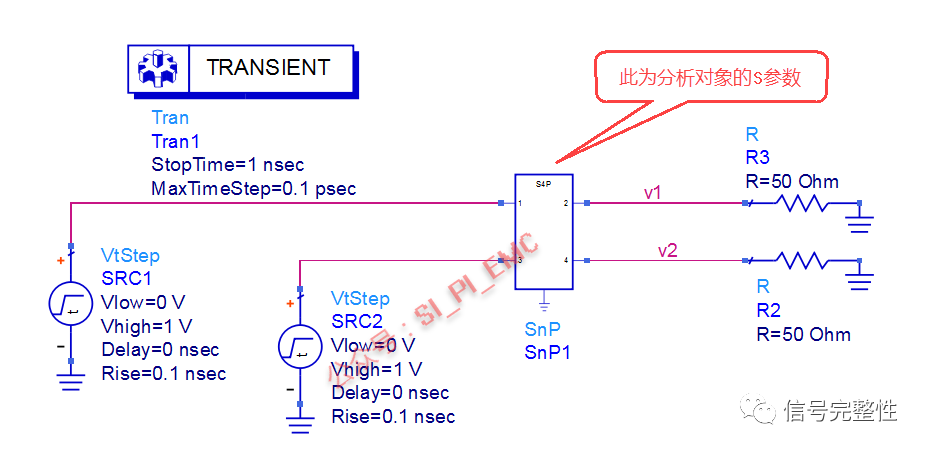

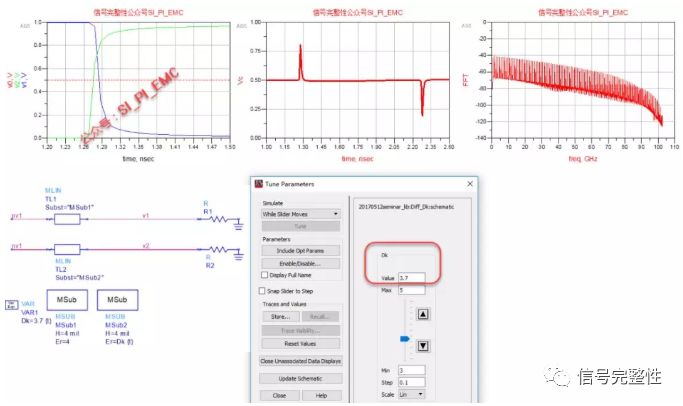

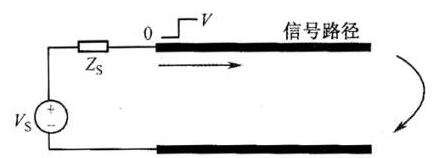

这个方式非常简单。第二种方式就在ADS中搭建一个原理图进行仿真,然后测量出来。仿真的原理图如下图所示,使用的时域仿真器Transient。

S参数与在PLTS中使用的S参数是一致的。在S参数输出端添加上网络名v1和v2。

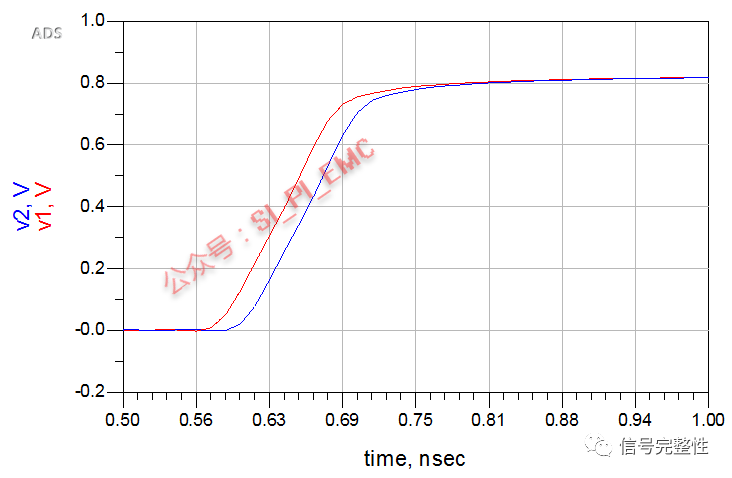

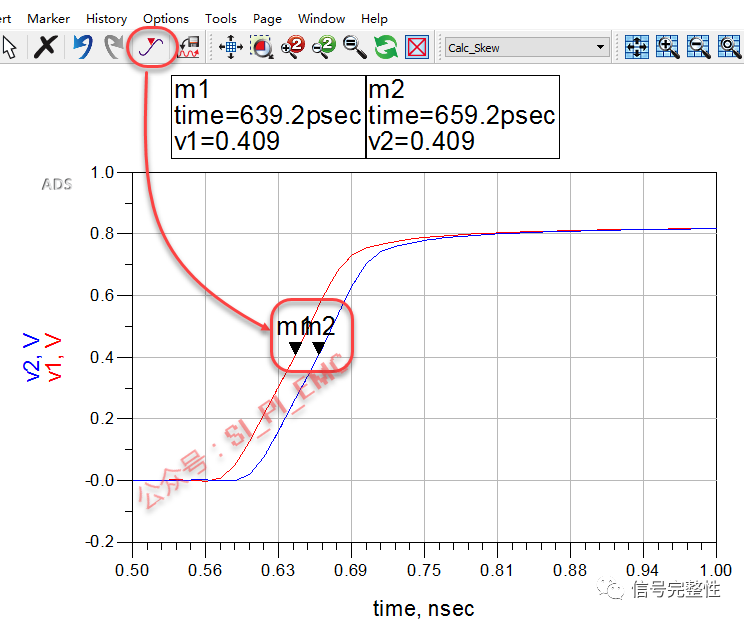

在数据显示窗口中获得如下图所示的波形曲线:

然后分别给v1和v2波形曲线添加Marker,这个要注意的是,幅值为波形总幅值的一半即中间点上,如下图所示:

显然,这时可以读取m2和m1之间的差值为20ps,即延时差(Skew)为20ps。这与PLTS值是一致的(相差0.02ps主要是由于软件在读取值的时候有误差)。

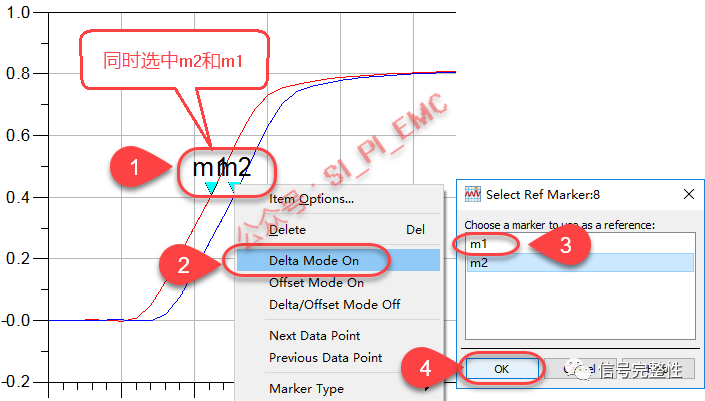

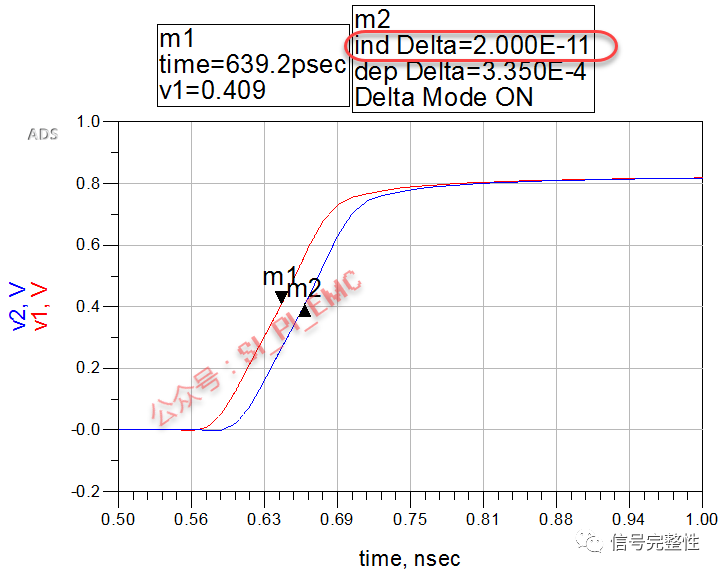

也可以直接读取m1和m2的差值,方式如下:

单击Ok按钮之后,即可读取延时差值(Skew):

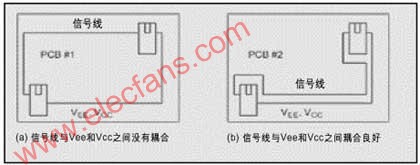

这样就非常方便的读取了传输线延时差了。在日常设计中大家一定要注意传输线延时差(Skew)所带来的影响,因为skew不仅仅会带来信号完整性的问题,也会导致EMI辐射的问题。在这前面的文章中介绍玻纤效应的时候就有介绍过。

有兴趣的也可以参照下文:

简述玻纤效应的影响、仿真以及解决方法

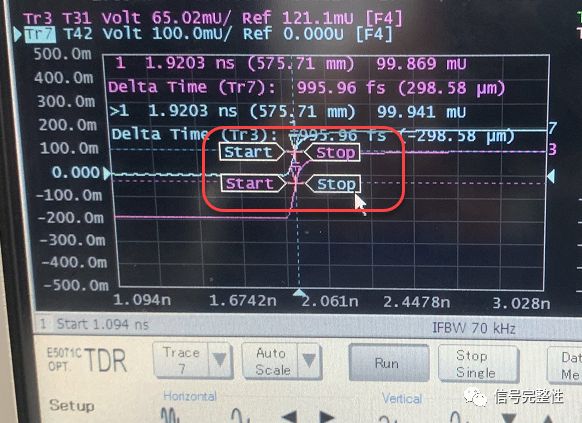

其实获得skew的方式非常多,比如也可以直接通过网络分析仪或者采样示波器测量出来。如下图所示为网络分析仪(E5071C)中测试得到的Skew:

对于不同的产品设计,要解决skew的方式是不一样的,有的通过绕线即可解决,比如PCB;有的则需要改变设计的结构,比如连接器设计。总之,当发现skew比较大时,想尽一切办法去减小skew,这样才能保证产品没问题。

以上内容仅供大家参考,如果大家有更加方便的方式也可以分享给大家。

审核编辑:汤梓红

-

pcb

+关注

关注

4418文章

23979浏览量

426331 -

信号完整性

+关注

关注

68文章

1500浏览量

98269 -

传输线

+关注

关注

0文章

384浏览量

25573 -

时序

+关注

关注

5文章

411浏览量

39019 -

S参数

+关注

关注

2文章

148浏览量

47909

原文标题:【干货】如何计算传输线之间的延时差/偏移(Skew)

文章出处:【微信号:SI_PI_EMC,微信公众号:信号完整性】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

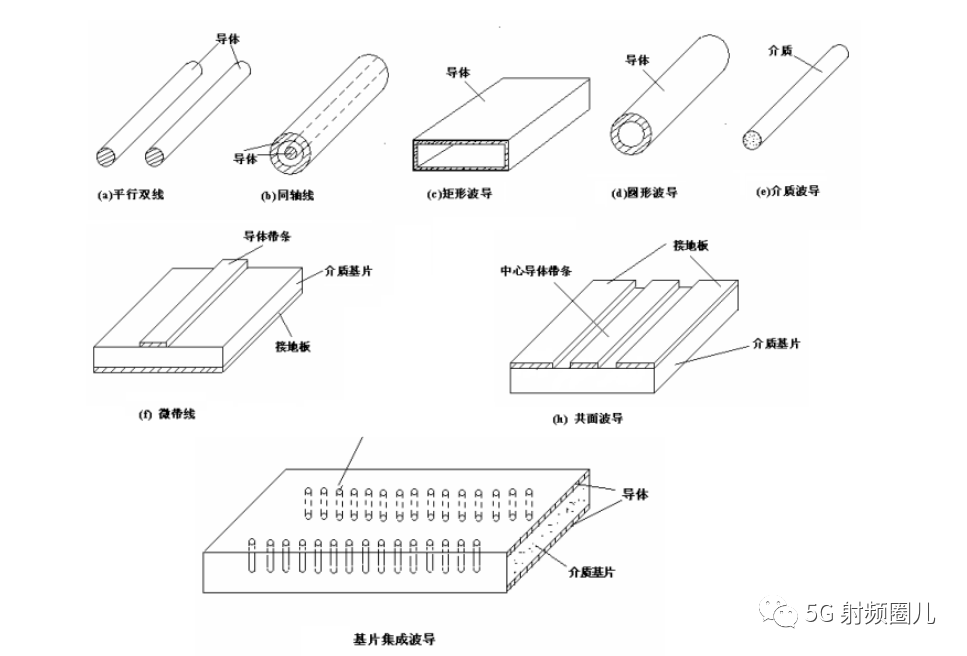

传输线的类型有哪些?PCB上什么样的线才是传输线?

射频传输线设计

传输线及其特性阻抗

PCB传输线参数

传输线阻抗计算中的有关问题

PCB传输线原理_PCB传输线参数

如何计算传输线之间的延时差/偏移

如何计算传输线之间的延时差/偏移

评论