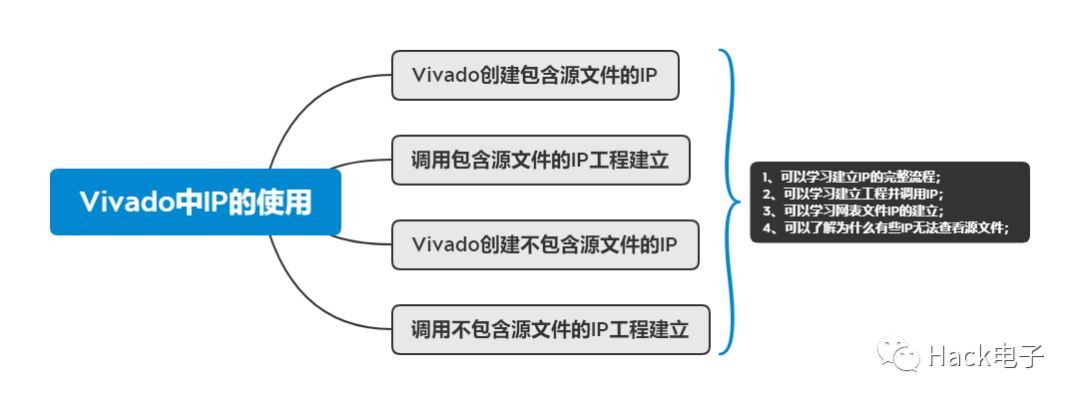

有时候我们想参考官方的源码,但是有些IP怎么也找不到官方的源码,具体原因是什么呢?

下面从下面两种Vivado创建IP的流程看下具体的原因:

所谓“数字积木”,就是Vivado集成开发环境基于IP的 “积木块”设计思想。

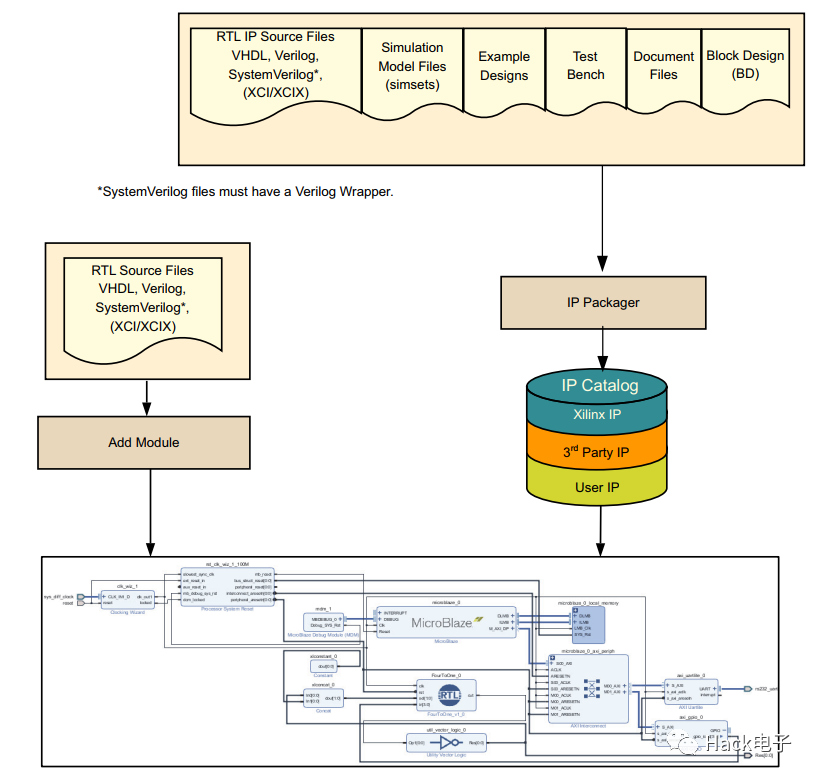

VIvado中IP定制化流程如下:

来源UG896

IP目录将来自下面的IP统一到一个环境中,这些IP包括XilinxIP、第三方IP和用户IP。

基于IP-XACT标准,VivadoIP封装器工具提供了独一无二的“重用”特性。IP封装器为Vivado的任何用户提供了一种能力,即将设计流程任意阶段的一个设计进行封装,然后将该IP作为一个系统级的IP进行使用。

创建不包含源文件的IP

上面建立的IP可以很方便操作一下看到源文件,实际使用过程中IP作为知识产权的成果,设计者并不希望公开IP核的源代码,下面将带你建立一个不包含源文件的IP。

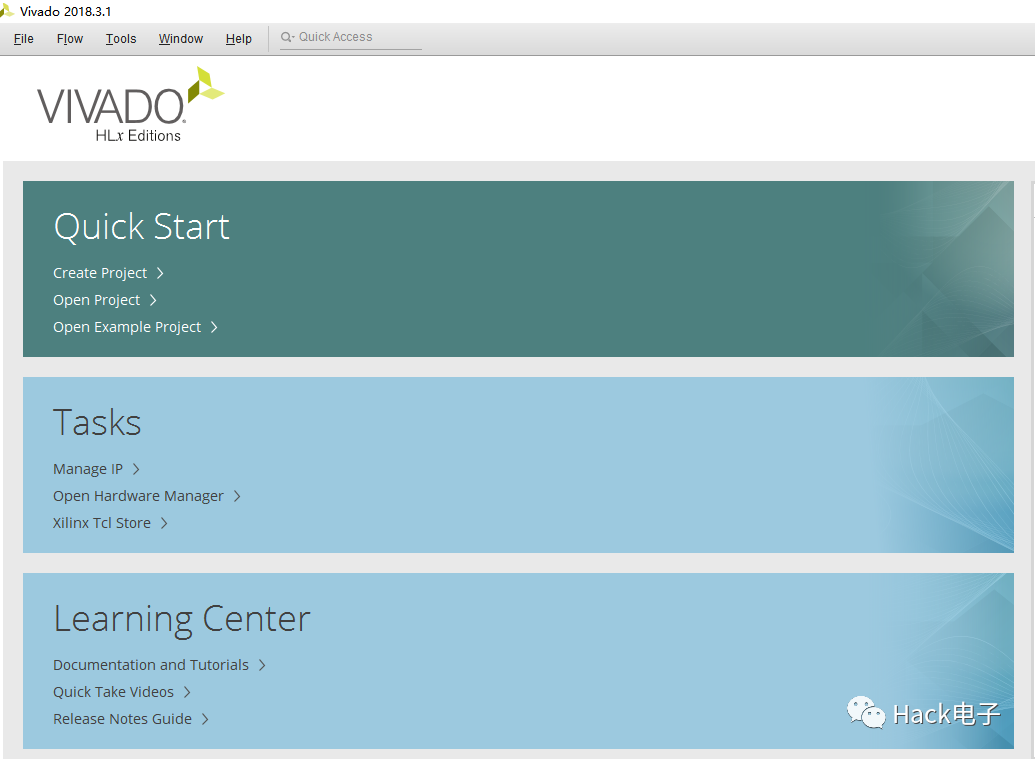

第一步:在操作系统下,执行菜单命令【开始】-【所有程序】-【Xilinx Design Tools】-【Vivado2018】点击【Vivado2018】,启动Vivado集成开发环境。

第二步:在“Vivado2018”主界面下,选择“Create New Project”选项,弹出“New Project-Createa New Vivado Project”对话框。

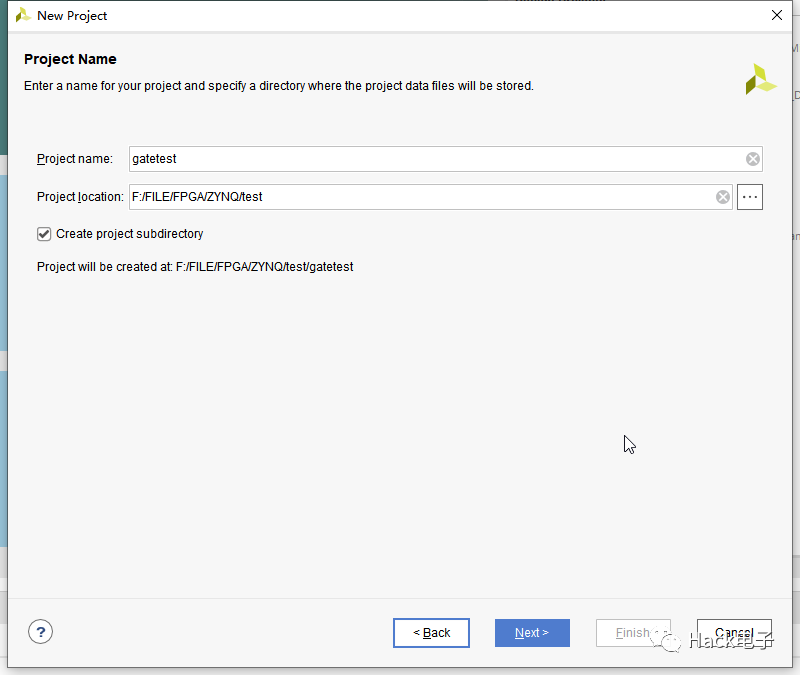

第三步:单击【Next】按钮,弹出“New Project”对话框。在该对话框中,按如下参数进行设置。

(1)Project name:gateip;

(3)选中“Create project subdirectory”前面的复选框。

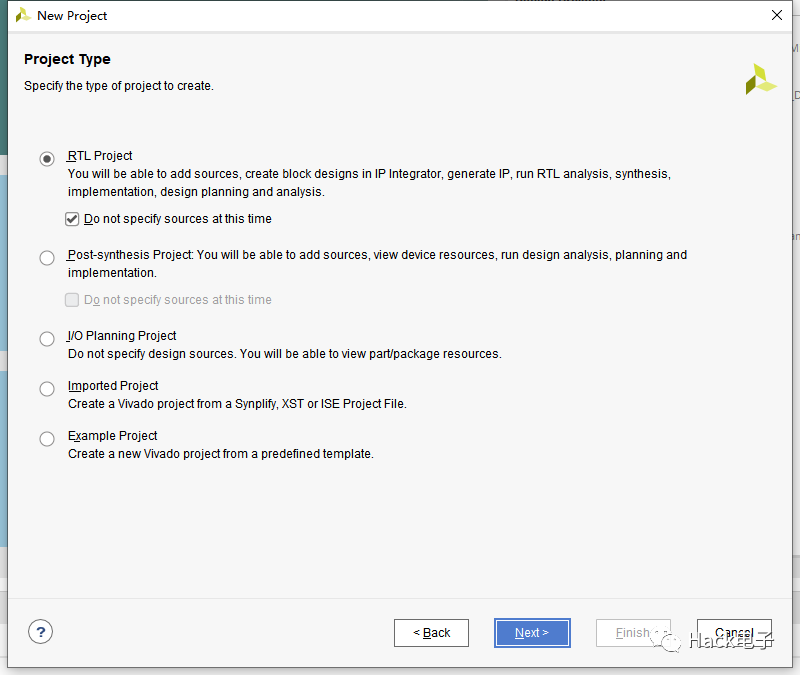

第四步:单击【Next】按钮,弹出“New Project-Project Type”对话框。在该对话框中,按如下参数进行设置。

(1)选中“RTL Project”前面的复选框;

(2)其他按默认设置。

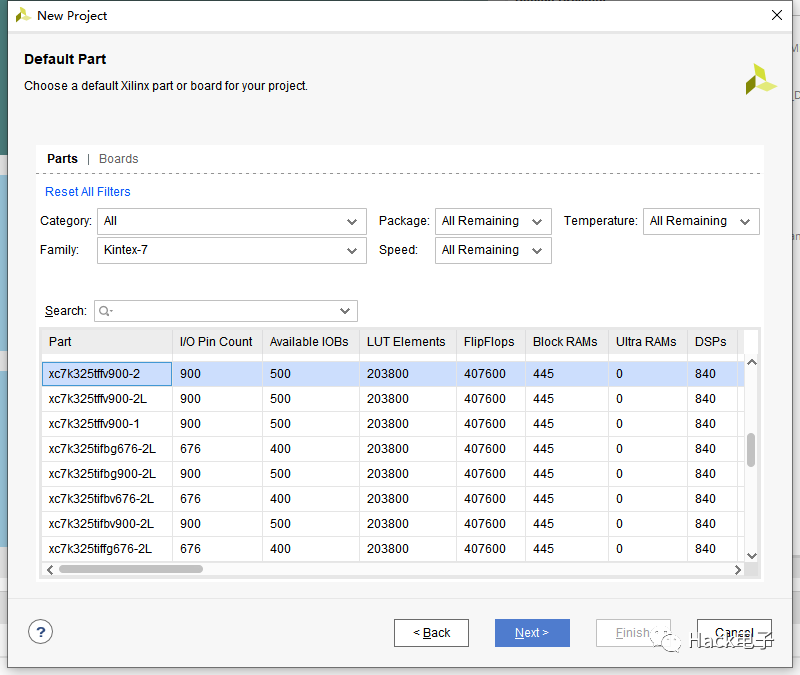

第七步:单击【Next】按钮,弹出“New Project-Default Part”对话框。在该对话框中,选择器件“xc7k325tffg900-2”。

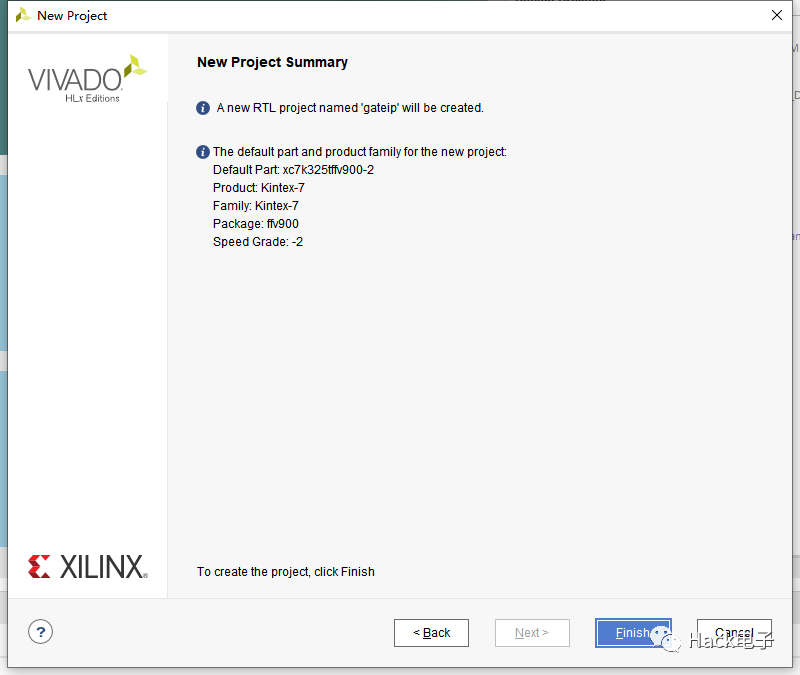

第八步:单击【Next】按钮,弹出“New Project-New Project Summary”对话框。

第九步:单击【Finish】按钮。

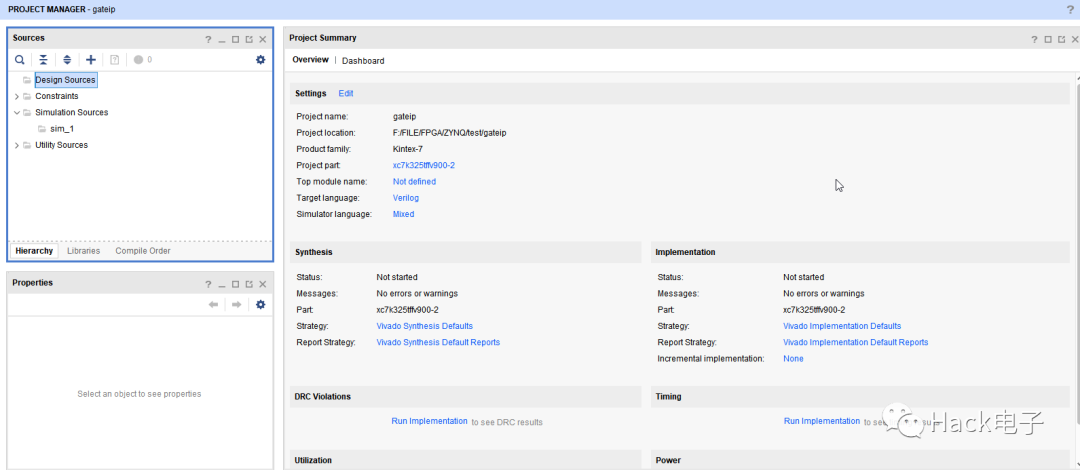

至此,完成新工程的创建。

接下来添加文件

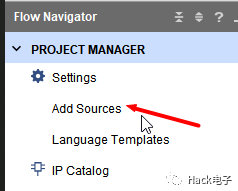

第一步:【Flow Navigateor】-【Add source】按钮

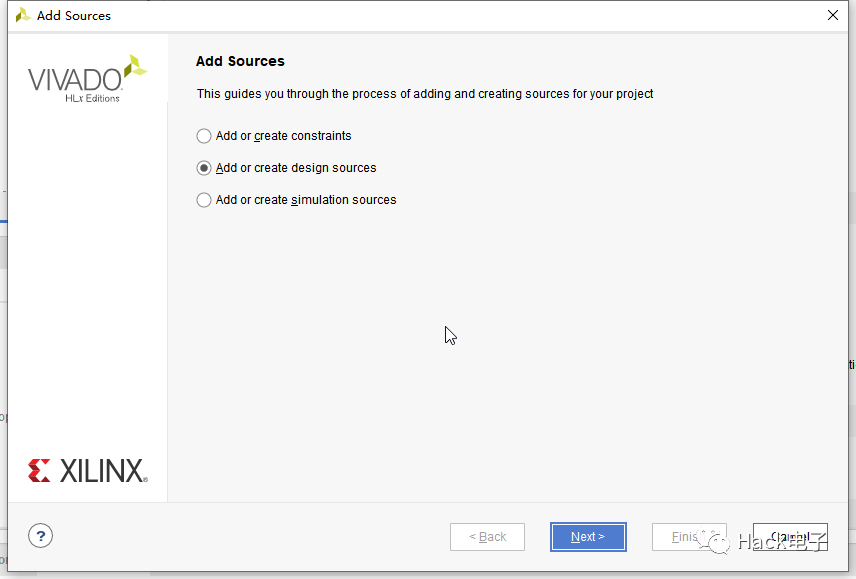

弹出“Add Sources“对话框。在该对话框中,单击【Add or crete design source】按钮,弹出“Add Source Files”对话框。在该对话框中,定位到XXXXsource路径。

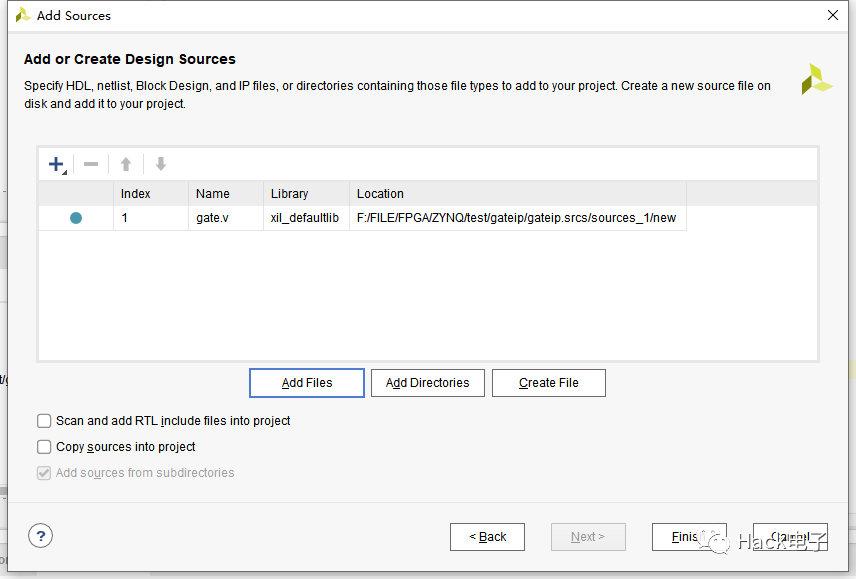

在该路径下,选择gate.v文件。可以看到在“Add Sources”对话框中添加了gate.v文件,并且注意下面的设置。

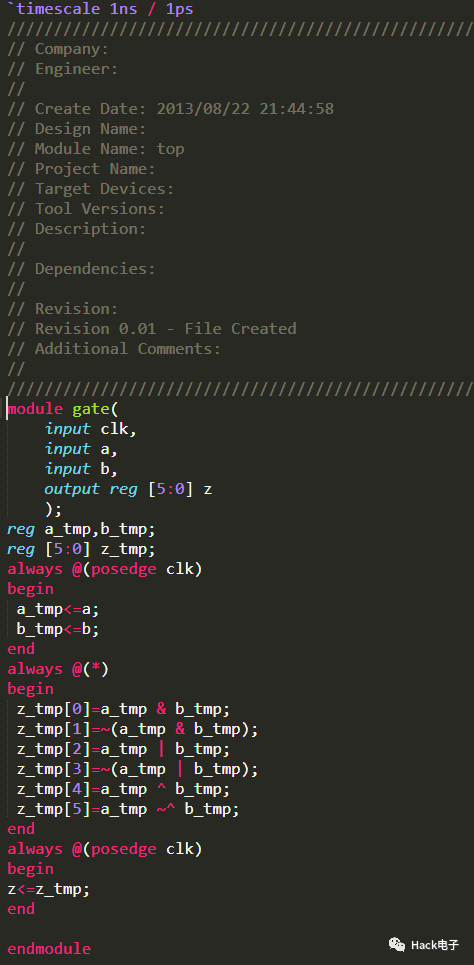

gate.v文件

第六步:单击【Finish】按钮。

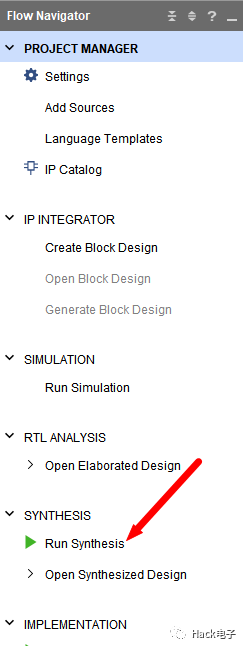

第七步:Vivado成开发环境界面左侧的“Flow Navigator”窗口中找到并展开“SYNTHESIS”选项。在展开项中,选择“Run Synthesis”选项,Vivado开始对该设计执行综合过程。

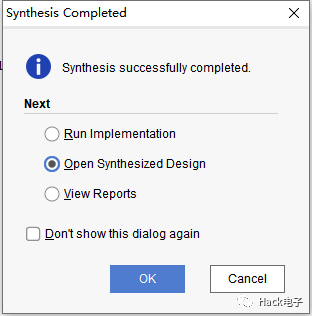

第八步:运行完综合过程后,弹出“Synthesis Completed”对话框。在该对话框中,选择“Open Synthesized Design”前面的复选框。

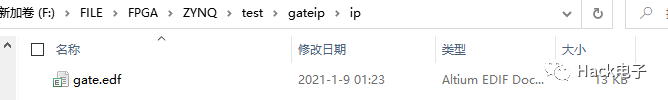

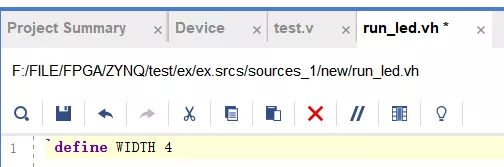

第九步:自动打开综合后的设计。在Vivado当前设计界面底部的“Tel Console”窗口中输入“write_edif F:/FILE/FPGA/ZYNQ/test/gateip/ip/gate.edf”命令,将gate.edf文件写到选择的目录下。

创建新的设计工程

第一步:启动Vivado集成开发环境。

第二步:在“Vivado2018”主界面下,选择“Create New Project”选项,弹出“New Project-Createa New Vivado Project”对话框。

第三步:单击【Next】按钮,弹出“New Project”对话框。按照实际进行设置即可。

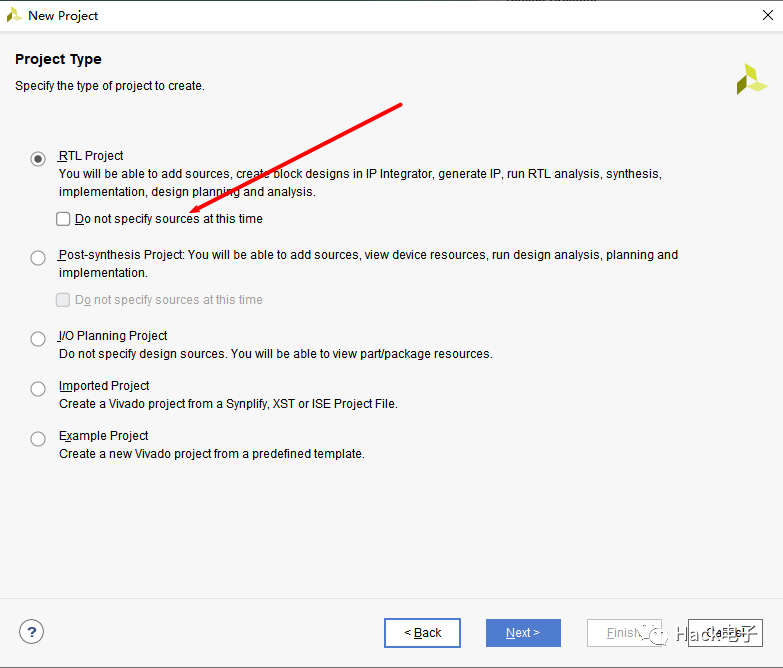

第四步:单击【Next】按钮,弹出“New Project-Project Type”对话框。在该对话框中,按如下参数进行设置。

(1)选中“RTL Project”前面的复选框。

(2)其他按默认设置。

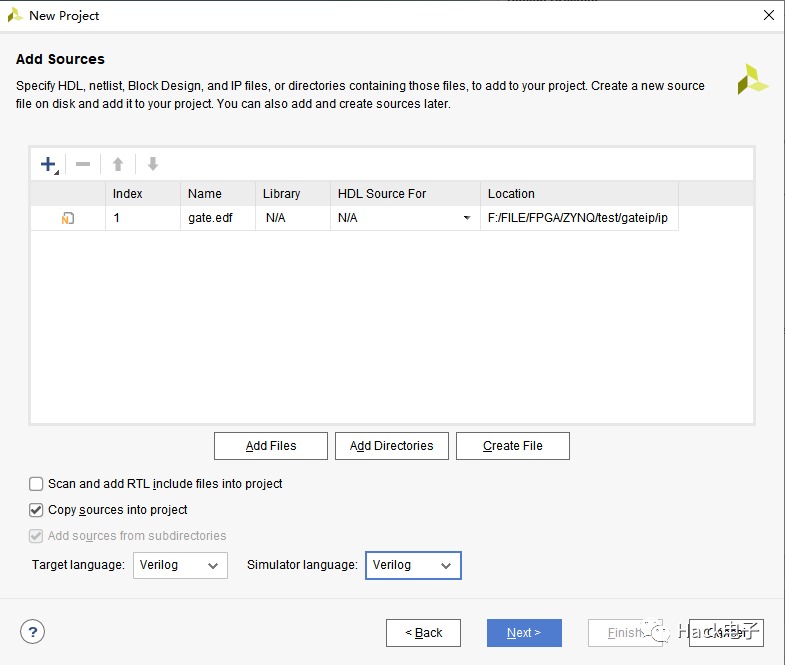

第五步:单击【Next】按钮,弹出“New Project-Add Sources“对话框。在该对话框中,单击【Add Files...】按钮,弹出“Add Source Files”对话框。在该对话框中,定位到gate.edf文件。可以看到在“Add Sources”对话框中添加了gate.v文件,并且注意下面的设置。

(1)在该对话框中,选中“Copy sources into project”前面的复选框。

(2)Target language:Verilog。

(3)Simulator language:Verilog。

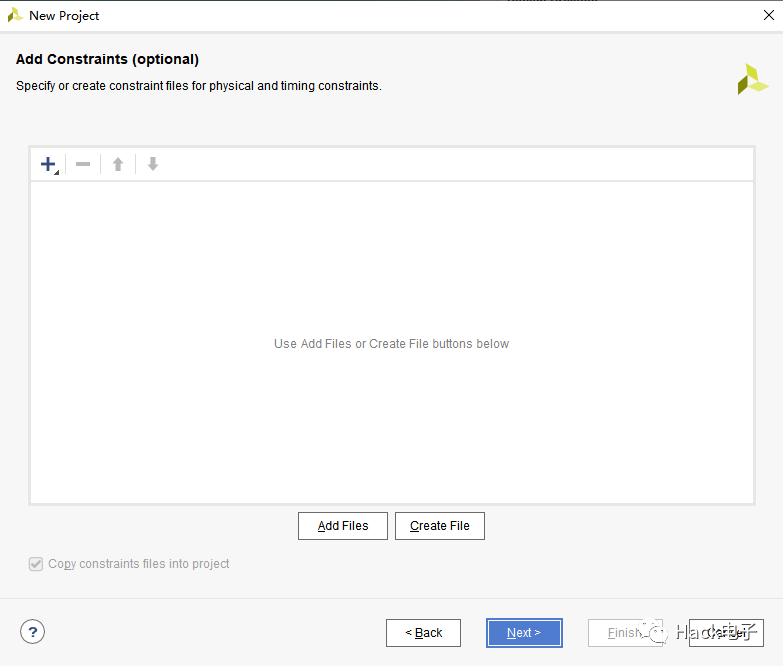

第六步:单击【Next】按钮,弹出“New Project-Add Constraints(optional)”对话框。

第七步:单击【NEXT】按钮,弹出对话框中,选择器件

第八步:单击【Next】按钮,弹出“New Project-New Project Summary”对话框。

第九步:单击【Finish】按钮。

至此,完成新工程的创建。

设置定制IP的库名和目录

第一步:在Vivado当前工程主界面左侧的“Flow Navigator”窗口中找到并展开“PROJECT MANAGER”选项。在展开项中,选择“Settings”选项。

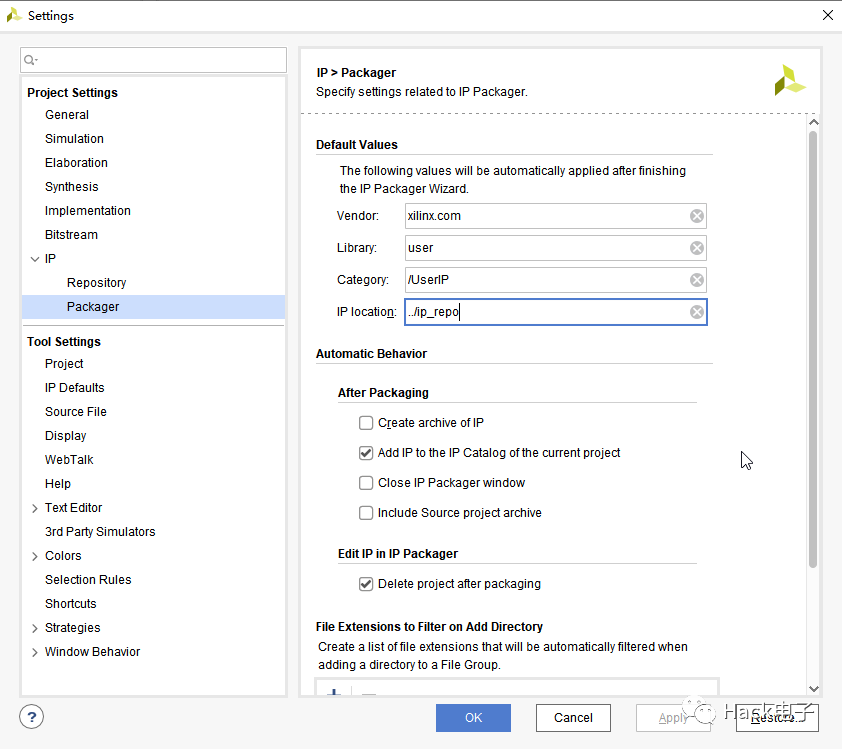

第二步:弹出“Settings”对话框。在该对话框左侧的窗口中,找到并展开“IP”选项。在展开项中,找到并选择“Packager”选项。在对话框右侧的窗口中,按如下参数进行设置。

第三步:单击【OK】按钮,退出“Settings”对话框。

封装定制IP的实现

封装IP的步骤如下所示。

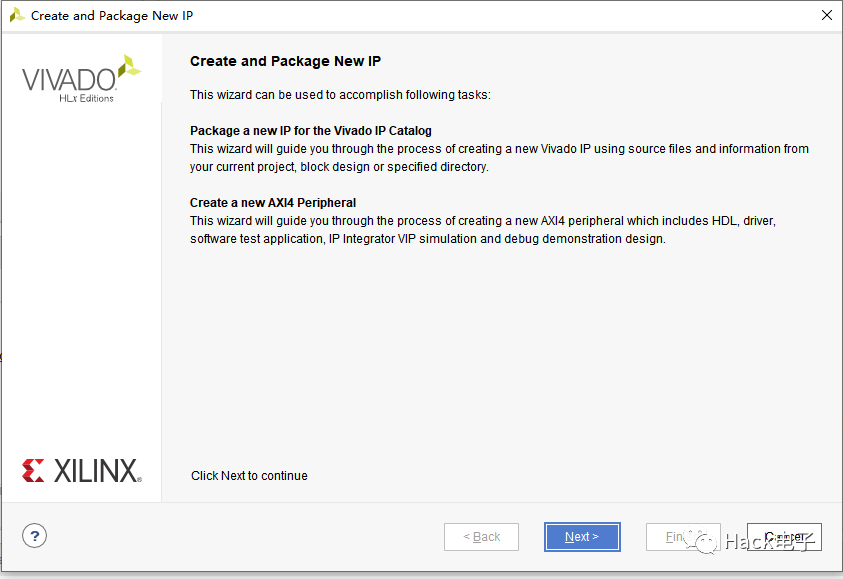

第一步:在Vivado当前工程主界面的主菜单下,执行菜单命令【Tools】-【Createand IP Package...】;

第二步:弹出“Create and Package New IP”对话框。

第三步:单击【Next】按钮。

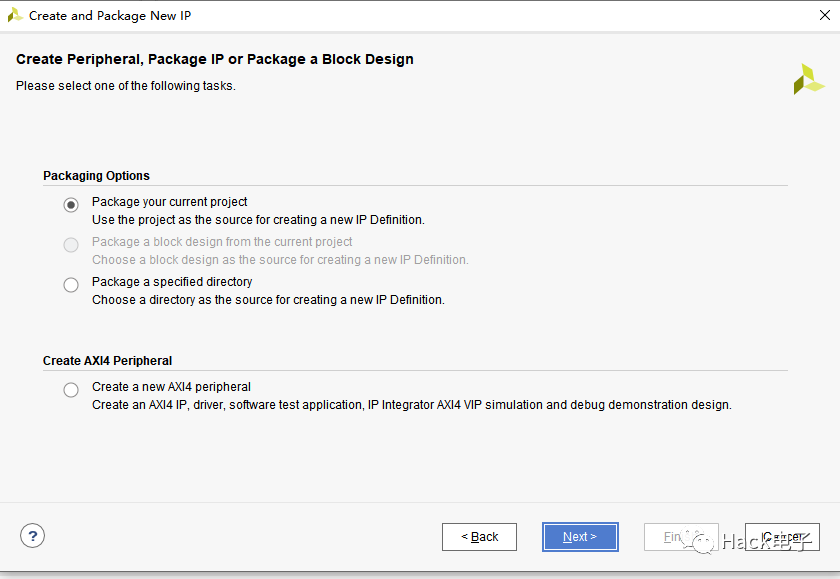

第四步:弹出“Create and Package New IP-Create Peripheral,Package IP or Packagea Block Design”对话框。在该对话框中,选中“Package your current project”前面的复选框。

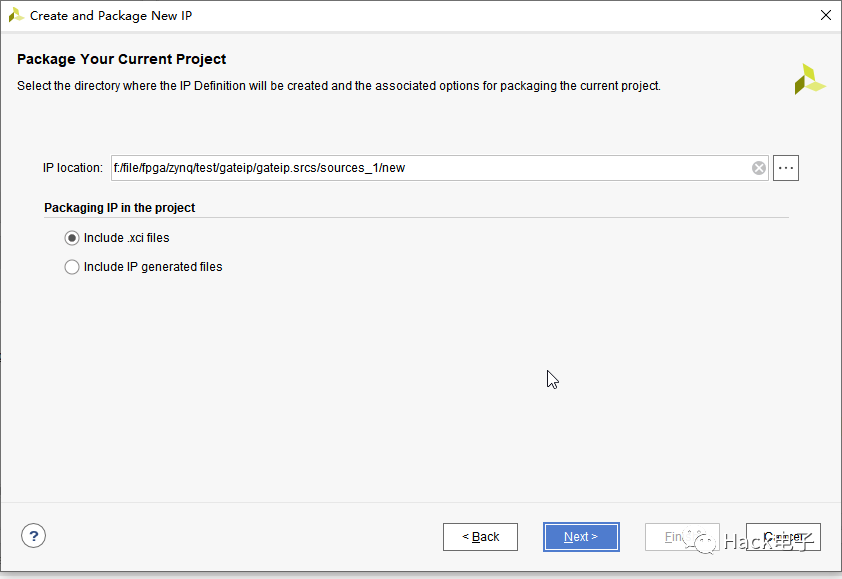

第五步:单击【Next】按钮,弹出“Create and Package New IP-Package Your Current Project”对话框。在该对话框中,按默认参数设置;

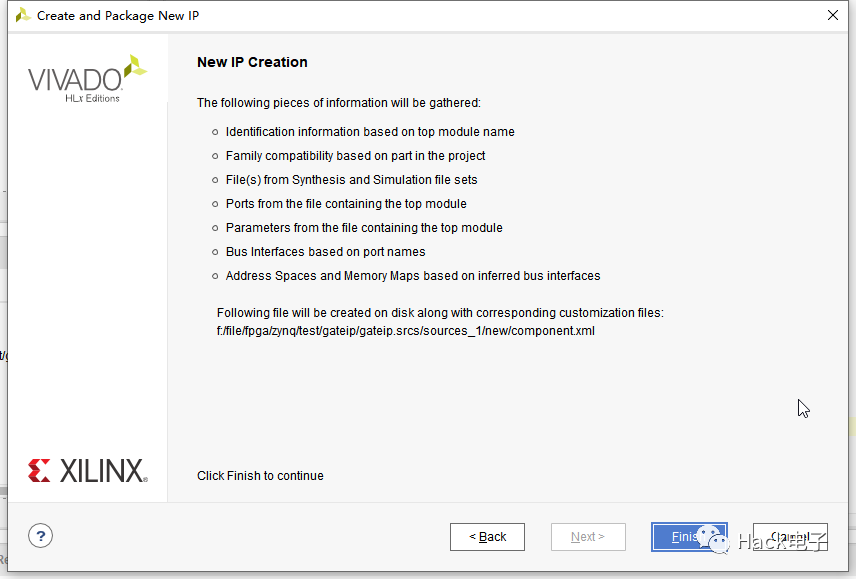

第六步:单击【Next】按钮,弹出“Create and Package New IP-New IP Creation”对话框。

第七步:单击【Finish】按钮,弹出“Package IP”提示对话框。

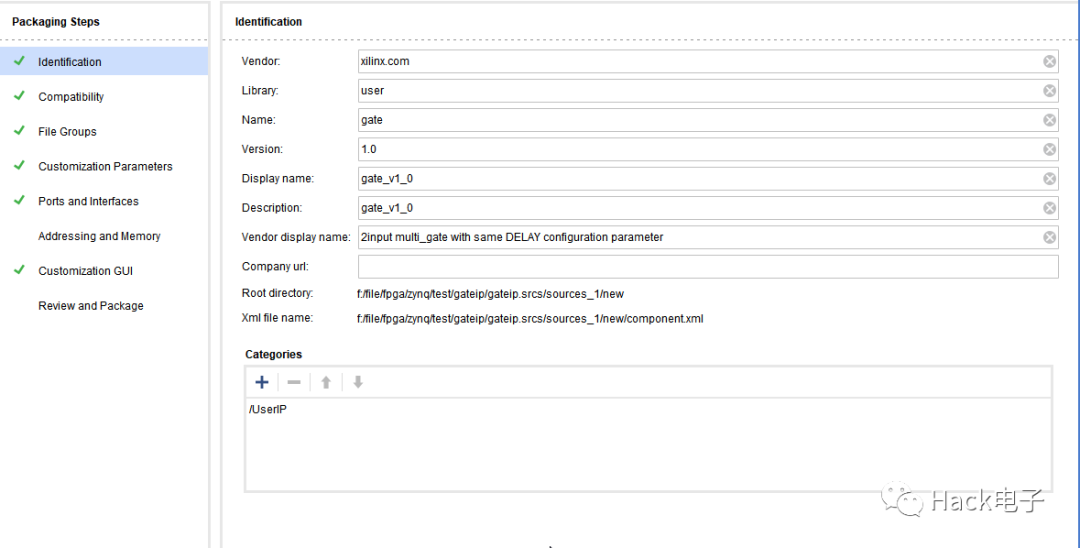

第八步:单击【OK】按钮,在Vivado右侧窗口中,出现配置IP参数的界面。如图所示,给出了“Identification”参数配置对话框。在该对话框中,按如下参数进行设置。

(1)Library:userdefme(与前面声明的库名称一致)。

(2)Name:gate

(3)Verison:1.0

(3)Display name:gate_v1_0

(4)Description: 2 input multi_gate with same DELAY configuration parameter

(5)Vendor display name:GPNT

(6)Companyurl:空着即可

(7)其他按默认参数设置。

第九步:选择“Compatibility”选项。

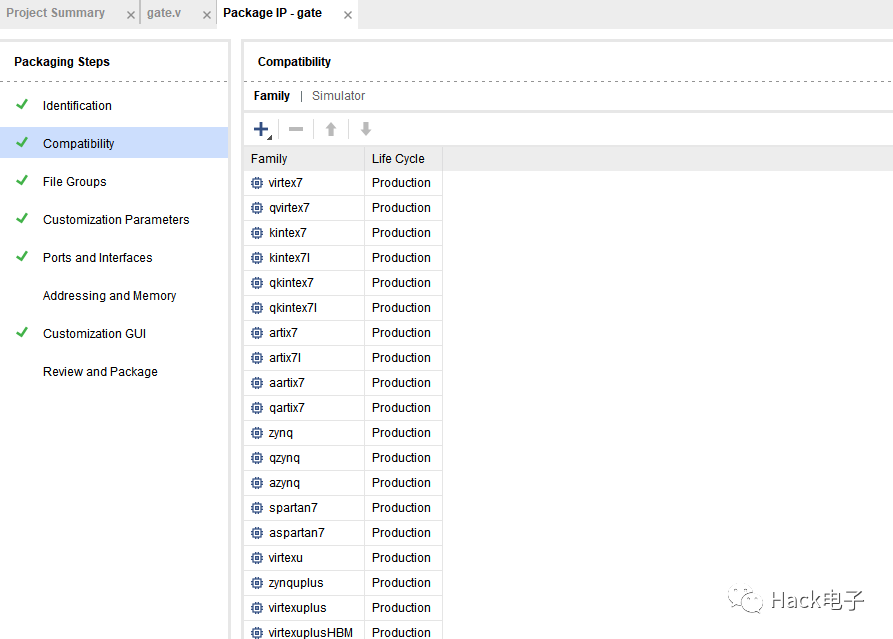

第十步:弹出如图所示的“Compatibility”参数配置对话框,该配置对话框用于确认该IP所支持的FPGA的类型

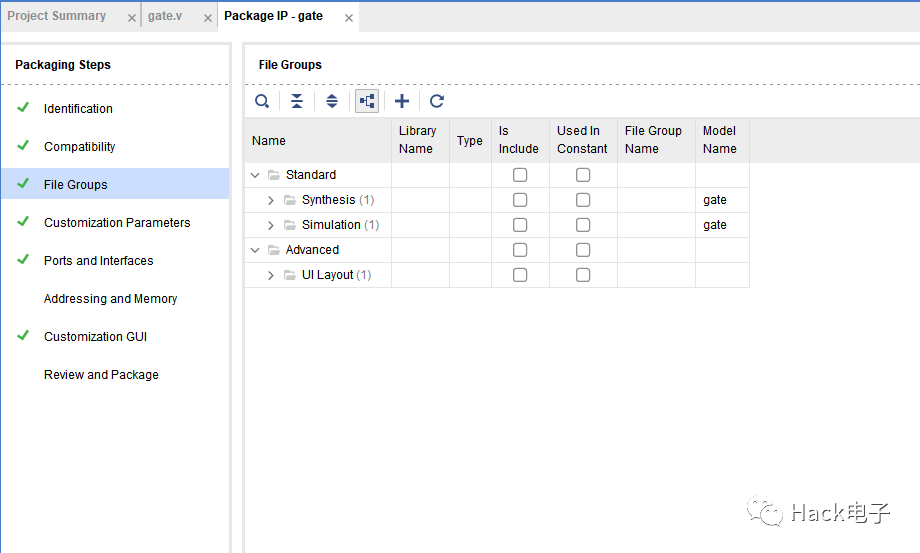

第十一步:单击“File Groups”选项,弹出如图所示的“File Groups”参数配置对话框

在该对话框中,设计者可以添加一些额外的文件,如测试平台文件。

第十二步:单击 “Customization Parameters”选项。

看到此时的界面为空的,并没有像前面封装包含源文件IP的时候出现“DELAY”参数,这是因为“DELAY”参数对于Verilog HDL而言是行为级描述,在综合的时候不起任何作用。所以,在对设计综合后,读者看不到“DELAY”参数。

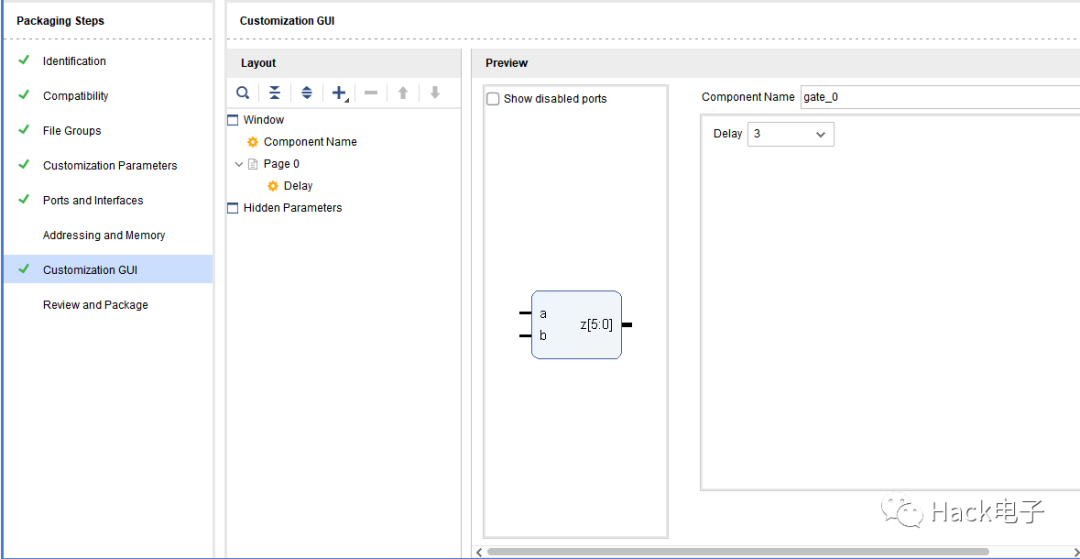

第十三步:单击“Customization GUI”选项,弹出如图所示的“Customization GUI”对话框。该对话框给出了输入/输出端口,以及带有默认值的参数选项。

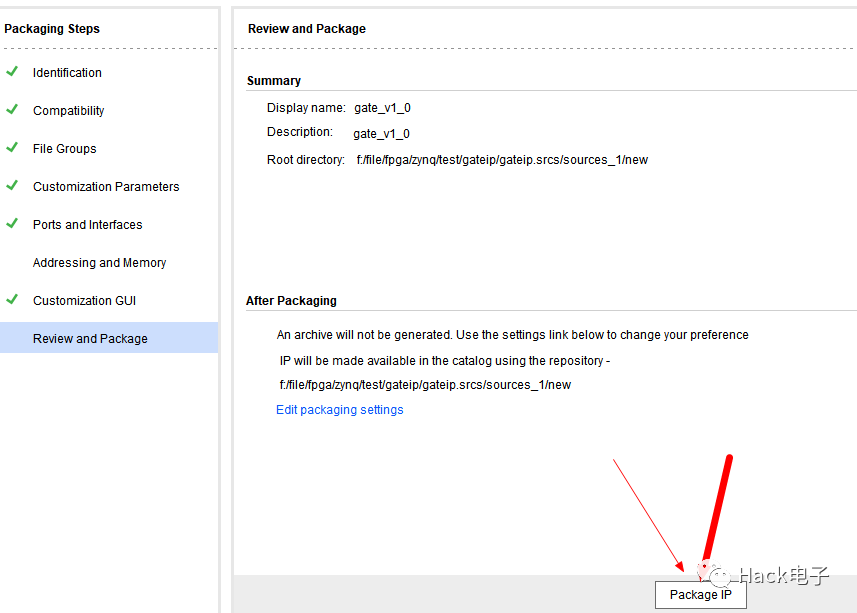

第十四步:选择 “Review and Package”选项,弹出“Review and Package”对话框,在该对话框中单击【Package IP】按钮,如图所示。

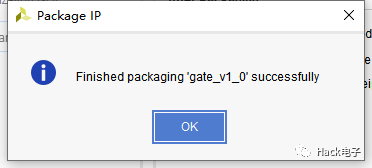

第十八步:弹出“Package IP”对话框,提不“Finished packaging ‘gate_v_l_0’successfully”消息,提示封装IP成功。

第十九步:单击【OK】按钮。

第二十步:在Vivado当前工程主界面的主菜单下,执行菜单命令【File】-【Close Project】,关闭当前的工程。

调用并验证不包含源文件的IP 设计

调用和使用完全和之前的章节一样,这里就不再赘述。

审核编辑:汤梓红

-

IP

+关注

关注

5文章

1739浏览量

150405 -

源码

+关注

关注

8文章

656浏览量

29786 -

Vivado

+关注

关注

19文章

819浏览量

67269 -

源文件

+关注

关注

0文章

30浏览量

4660

原文标题:【Vivado那些事】创建不包含源文件的IP

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

PYNQ设计案例:基于HDL语言+Vivado的自定义IP核创建

基于 FPGA vivado 2017.2 的74系列IP封装

怎么迁移那些具有Netlists源文件的pcores?

包含路径不会添加到项目中的每个源文件怎么解决?

基于vivado的fir ip核的重采样设计与实现

Vivado将模块封装为IP的方法介绍

如何创建Vivado HLS项目

【Vivado那些事】Vivado下头文件使用注意事项

Vivado创建不包含源文件的IP

Vivado创建不包含源文件的IP

评论