什么是帧缓存(frmbuf)

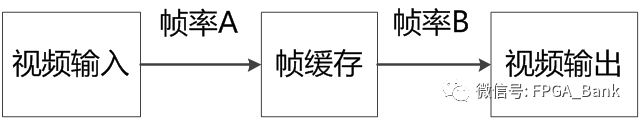

在视频处理系统中,将输入的图像以帧为单位储存到存储器(DDR)中,再根据输出时序需求,读取图像并输出,达到帧率变换、暂停显示的目的。

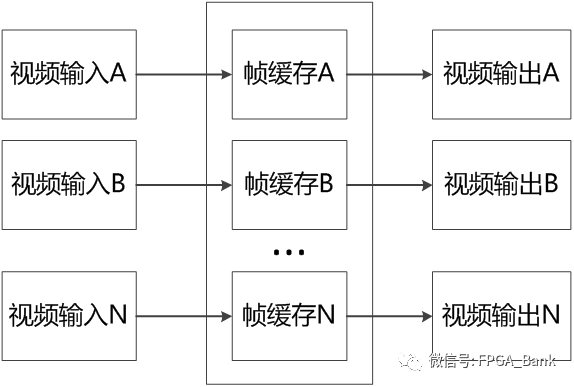

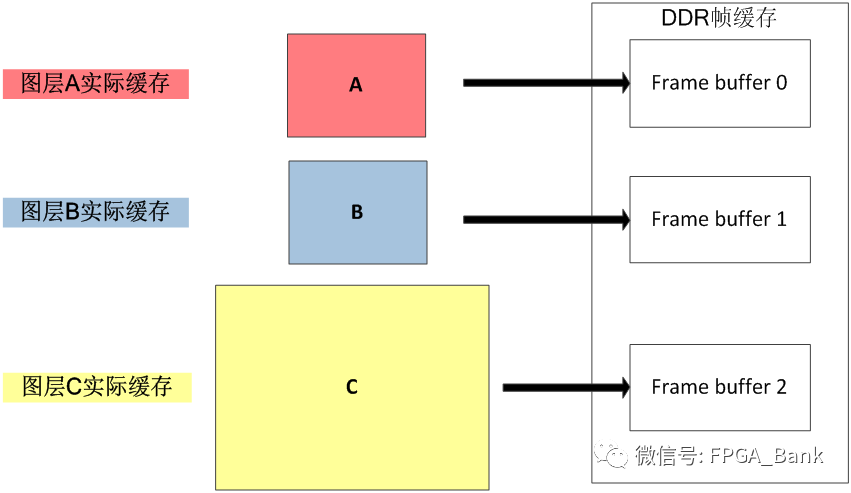

在大部分应用中,视频输入输出的数量通常都不止一组,也就是需要多个帧缓存进行视频的存储;

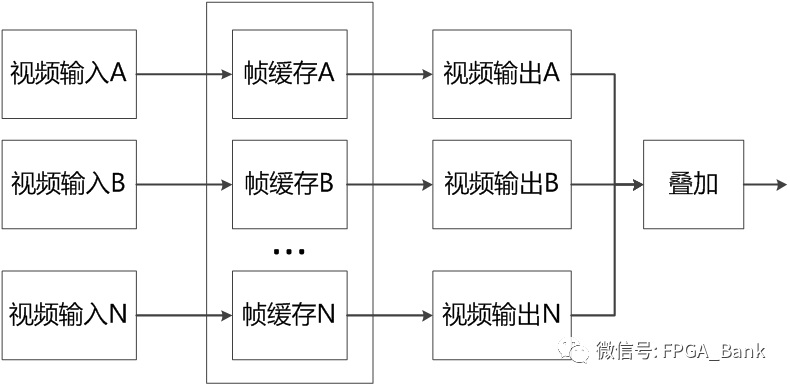

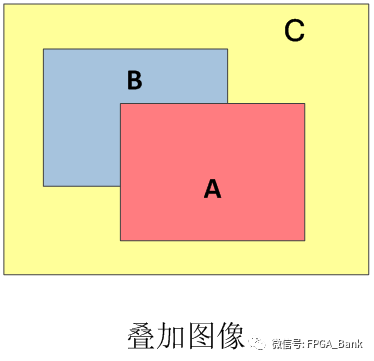

如果一个系统中存在多路视频输入,而只有一路视频输出,那么通常在帧缓存后还要将多路视频叠加在一起才可以进行输出;

常用的帧缓存设计

在常规的视频处理平台中,为了实现多路视频的任意叠加,会将输入到系统中的所有视频都缓存到DDR中,进行叠加时,将所有图层的完整视频从DDR读出,再根据层叠关系进行叠加;

优点:

操作简单

更改叠加位置时可以立刻响应

可拓展透明叠加功能

缺点:

每一个图层都缓存完整的视频,占用的DDR带宽较大,尤其 是在多图层系统中。

以FPGA实现存储4K@60输入,4K@60输出的视频为例:RGB444 24BIT像素

写有效带宽:3840*2160*24*60大约为12Gbit

读有效带宽:3840*2160*24*60大约为12Gbit

总的需要占用DDR带宽为24Gbit。

审核编辑:刘清

-

FPGA

+关注

关注

1629文章

21729浏览量

603024 -

存储器

+关注

关注

38文章

7484浏览量

163768 -

DDR

+关注

关注

11文章

712浏览量

65318 -

RGB

+关注

关注

4文章

798浏览量

58463

原文标题:在FPGA上关于DDR的帧缓存介绍

文章出处:【微信号:FPGA研究院,微信公众号:FPGA研究院】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于FPGA的帧同步系统设计方案

基于FPGA与的VHDL语言驱动时序发生器与数据缓存器的一体化设计

LOTO示波器软件PC缓存(波形录制与回放)功能

视频相邻帧相减,怎么解决图片缓存问题

【AC620 FPGA试用申请】以太网传图帧缓存设计

【AC620 FPGA试用体验】+以太网传图帧缓存系统设计 附工程源码(结项)

FPGA的图像缓存部分电路是怎么写的

帧差法FPGA实现原理

关于内存可缓存性的疑问怎么解释

如何完成基于FPGA技术的驱动时序发生器与数据缓存器的一体化设计?

帧同步系统的FPGA设计

基于FPGA的高速图形帧存设计

简述OpenGL帧缓冲区多线(FBO)基本概念

LOTO示波器软件PC缓存(波形录制与回放)功能

什么是帧缓存?在FPGA上关于DDR的帧缓存介绍

什么是帧缓存?在FPGA上关于DDR的帧缓存介绍

评论