文章来源:半导体综研 原文作者:关牮 JamesG

半导体芯片封装的目的无非是要起到对芯片本身的保护作用和实现芯片之间的信号互联。在过去的很长时间段里,芯片性能的提升主要是依靠设计以及制造工艺的提升。

随着半导体芯片的晶体管结构进入到FinFET时代,工艺节点的进步呈现明显的趋缓形势。虽然根据行业的发展路线图,工艺节点的迭代还有很大的上升空间,但我们能够明显感觉到摩尔定律的减缓,以及生产成本暴增带来的压力。

由此,通过改革封装技术来进一步挖掘性能提升的潜力成为一个非常重要的手段。好几年前开始,行业内就出现了通过先进封装的技术来实现 “超越摩尔(More than Moore)”的口号。

所谓先进封装,一般行业内的常用定义就是:所有利用前道制造的工艺方法的封装技术。

通过先进封装的手段,我们可以:

大幅度缩小封装后芯片的面积

无论是多个芯片的合封,还是单个芯片的Wafer Level化封装,都可以明显降低封装尺寸以减小整个系统板的使用面积。利用封装手段缩小芯片面积在经济上要比提升前道工艺来得更为划算。

容纳更多芯片的I/O端口数量

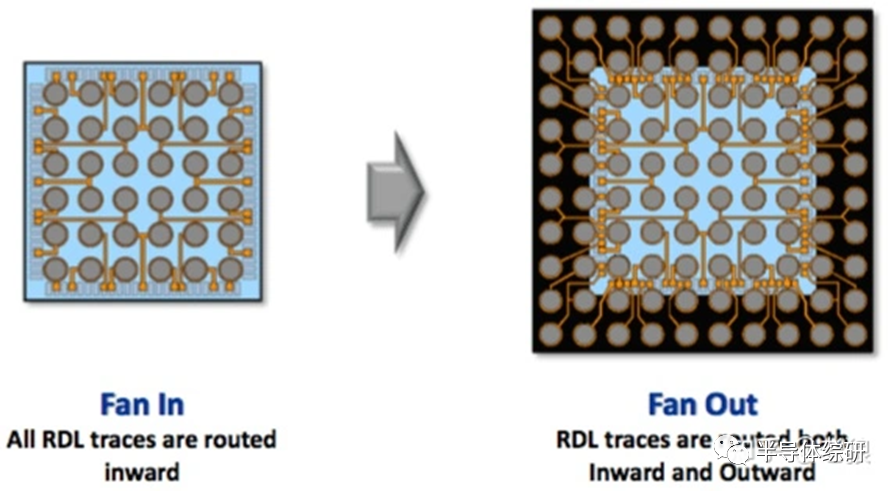

由于前道工艺方法的引入,我们可以利用RDL技术使得单位面积的芯片上能够容纳更多的I/O管脚,从而减少芯片面积的浪费。

降低芯片综合制造成本

由于引入Chiplet的方案,我们可以比较容易地将多个不同功能、不同工艺技术/节点的芯片合封到一起,形成一个系统集成芯片(SIP)。这样就可以避免所有功能和IP都必须采用同一种(最高工艺)的高成本方法。

提升芯片间的互联能力

随着大算力需求的提升,在很多应用场景里都需要计算单元(CPU、GPU...)和DRAM做大量的数据交换。这往往会导致整个系统几乎有一半的性能和功耗浪费在信息交互上。现在我们通过各种2.5D/3D封装,将处理器和DRAM尽可能近的连接在一起,就可以将这种损耗降低到20%以内,从而大幅度降低计算的成本。这种效率的提升远远超过了通过采用更先进制造工艺带来的进步。

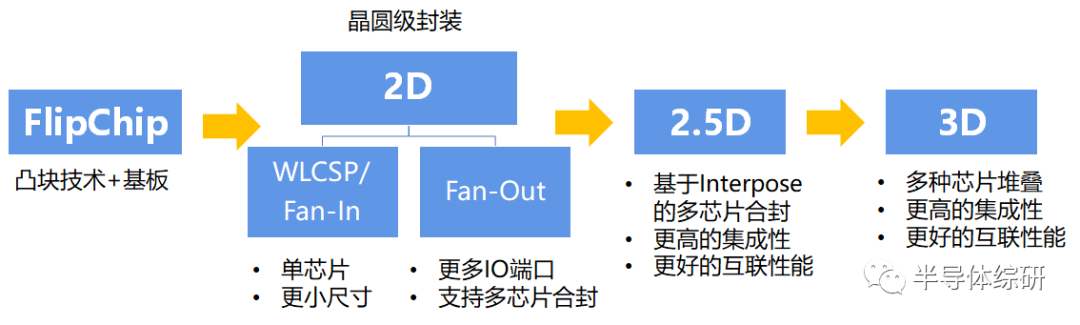

下图是先进封装技术的演进过程

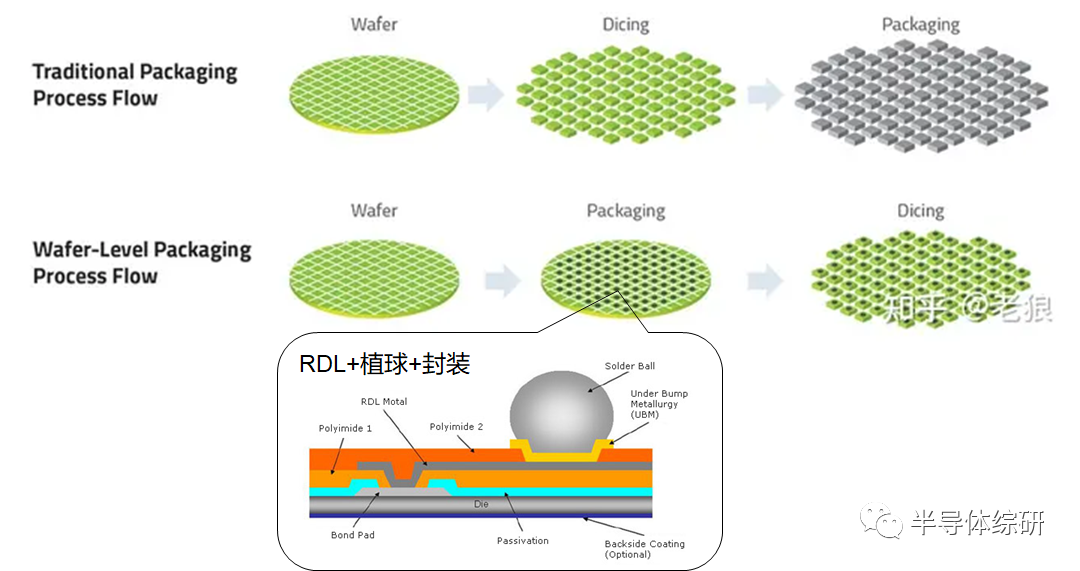

在Flipchip阶段,封装的方式还比较接近于传统技术路线(我多数时候其实是把Flipchip当作传统封装来对待的)。 而从下图可以看到,相对于传统封装,WLCSP(FanIn)的方法就和传统有着明显的区别:用前道技术直接对晶圆进行加工(RDL+凸块)后再直接切割形成芯片。

而当芯片上的I/O端口越来越多,以至于芯片有限面积无法直接容纳这么多管脚的时候,在原来WLCSP(Fan-In)的基础上又发展出了FanOut技术:通过封装材料扩大芯片面积来容纳更多管脚。而且这样一来,多芯片的合封也成为了可能。

当然,封装技术的发展并未在此止步。随着大算力芯片的技术和市场需求的高速发展,行业内又开始开发了2.5D和3D技术:

2.5D:通过Interposer(通常以硅基板为主要材料)将处理器和HBM(High Bandwidth Memory)进行高密度和高效率互联。其中最有名的就是最近因为人工智能而火出圈的台积电的CoWoS封装技术。

3D:直接将不同芯片在Z轴方向上堆叠,通过TSV等方法实现更高效率互联。

审核编辑:汤梓红

-

芯片

+关注

关注

455文章

50807浏览量

423521 -

半导体

+关注

关注

334文章

27362浏览量

218613 -

封装

+关注

关注

126文章

7900浏览量

142948 -

晶体管

+关注

关注

77文章

9692浏览量

138170 -

先进封装

+关注

关注

2文章

404浏览量

246

原文标题:我们为什么需要了解一些先进封装?

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

多芯片整合封测技术--种用先进封装技术让系统芯片与内存达到高速传输

一图了解频率控制技术的演进

哪一种芯片不属于 FPGA 的演进过程中的芯片类型

CDMA技术分阶段向LTE演进过程

云服务架构的演进过程

浅谈关于云服务架构的演进过程

从2G到5G,核心网的演进过程和思路解析

5G核心网演进过程与现存问题分析

区块链的核心技术挖矿演进详细资料说明

SaaS的演进过程(SaaS,PaaS和IaaS及特点)

百度垂类离线计算系统的演进过程 百度垂类离线计算系统的设计与实现

先进封装技术的演进过程

先进封装技术的演进过程

评论