看到这个题目,可能不少朋友都会满脸问号,我们知道cell内部会有leakage,难道cell与cell之间也会有leakage吗?对,没错,今天就想稍微讲解一下这个问题,以便于我们后端理解cell中一些奇怪的工艺。

首先,所谓漏电流,就是指管子不导通的时候流过的电流,即pn结在反向截止状态时,也会有一个很微弱的电流流过,我们就称之为leakage。

对于MOS管来说,它的source、substrate、drain中总会存在一个这样的leakage。那么相邻cell的leakage是如何产生的呢?这就要从layout的工艺开始讲起了。

不知道大家了不了解这些源漏掺杂是如何产生的,其实,工艺的顺序是:首先铺一层衬底,就以NMOS为例好了,先铺一层P衬底,而后通过一些刻蚀沉积之类的方法,标定源漏的位置,然后在这些位置注入n离子,或者说注入电子,形成n well,对于p well就是注入p离子。

这里我就说的不太严谨了,应该就是注入某种材料,总之得到我们的n区p区。我们把这个能注入离子的区域称为有源区,或者叫扩散区,有的fab会称为OD(oxide diffusion)。

如果这个NMOS管旁边还有个NMOS管,这两个管子分别属于不同的cell的话,最传统的做法是分别来做,它们的OD是各自独立的,两个OD之间应该会是其他的材料。

注意,这里对于同一个cell里面可能会有许多MOS管,它们的OD是连在一起的,而cell与cell之间的OD是分开的。

那么cell间的漏电流就很好理解了,就是指分属不同OD的n区p区之间产生的漏电流。由于两个cell的OD并不相连,它们之间的leakage非常非常小,几乎无限接近于0。

然而以上的layout设计会有一个弊端,就是为了分割不同的OD,必须要把cell做的很大,cell的边界要留有一定的空间才行。

要知道PPA中的A-area是我们追求的目标,如何能把cell做的更小一点呢?后来人们提出了CNOD技术(continuous OD),意思是做cell的时候就不把相邻cell的有源区分开了,让他们连在一起好了,没有了中间空隙的要求,这样就大大降低了cell的面积。

那么,代价是什么呢?没错,就是会增大cell之间的漏电流。人们为了再减弱这部分漏电流,一般会在连在一起的那部分OD里注入一些奇怪的材料。具体我也不知道是啥了。

后来人们还是觉得这部分cell间leakage过大,又提出了PODE技术(poly over OD edge)。这个我就了解不多,说错见谅。它是指在OD的边缘上面盖一层poly finger,可以有效减小漏电流,并且相邻cell的OD间距也能大幅缩小。

对于FinFET来说想像起来就比较直观,相邻cell的两个fin就被一块poly阻隔了(FinFET鳍式场效应管,之后可能会专门写文章来聊)。

后来人们为了进一步压缩面积,又又又来了CPODE,即common PODE,意思是相邻的cell就不需要每个人出一个poly了,两个人公用一块poly就可以了,漏电流也不会变大,而面积就省下来了一部分。在芯片界,作为人类最高技术的代表,即使只是为了那么一点点的改善,也要付出巨大的努力。

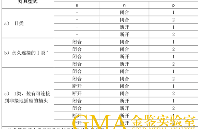

说了这么多,其实作为后端工程师,实际工作中也不会用到。只是明白有的cell会标注CPD(CPODE)、CNOD这样的字眼,就代表了这些cell用到了相应的技术。

-

场效应管

+关注

关注

47文章

1163浏览量

64001 -

MOS管

+关注

关注

108文章

2420浏览量

66995 -

Layout

+关注

关注

14文章

405浏览量

61826 -

漏电流

+关注

关注

0文章

262浏览量

17039 -

FinFET

+关注

关注

12文章

248浏览量

90254

发布评论请先 登录

相关推荐

什么是泄漏电流试验?

医用漏电流测量装置(YC9706-MD-N)漏电流的测试 深圳一测

电容器漏电流测试原理是什么

什么是漏电流,漏电流和陶瓷电容有什么关系?

layout相关—芯片中相邻单元的漏电流

layout相关—芯片中相邻单元的漏电流

评论