天线效应,或者说它的全称工艺天线效应(PAE,process antenna effect),是一种芯片制造过程中产生的效应。

我们后端设计时也必须严格遵守相应的天线效应的rule,否则可能会发生MOS管的损坏,以至于影响良率。今天就来简单说一说什么是天线效应,以及消除的办法有哪些。

要想理解antenna,必须了解金属层是如何制造的。现代工艺采用了一种叫离子刻蚀的方法,在制造每一层metal layer的时候,会先在这个layer上铺满金属,而后通过离子刻蚀去掉不要的部分,留下来的就是我们画的net走线了。

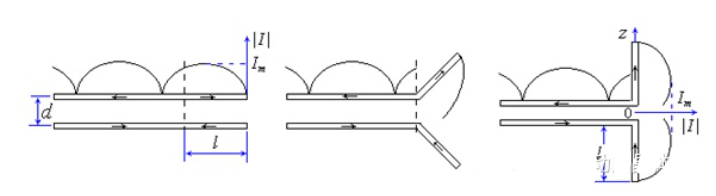

然而离子刻蚀的时候空间中会出现大量的电荷,这些电荷就会附着在金属表面,电荷量的多少与金属面积正相关。现在金属的厚度一般都要大于金属的宽度,相应的金属线侧边会聚集更多电荷。

这些net就如同天线一样吸收着空间中的电荷,如果这根net连接到MOS管的栅极,如果电荷过多就有可能击穿栅氧化层,造成MOS管损坏。

请注意一点,天线效应仅仅发生在制造过程中,因为制造完毕的芯片MOS的栅极一定有一个driver,也就是说会连到某一个source/drain上。

如果真的一条net大量存在电荷,这些电荷也会优先从源漏泄掉,不管是pn结正向导通还是反向击穿,其产生条件都没有击穿栅氧化层苛刻。

为了量化天线效应的影响,我们引入了天线效应比率的概念,它又分成局部天线效应比率和累积天线效应比率。局部天线效应比率指的是某一层金属的面积比上与他相连的栅的面积,这个比率越大,造成击穿的可能性就越高。

累积天线效应比率指的是所有产生天线效应金属层的局部天线效应比率之和。一般我们的antenna rule就会根据这两个比率来定,后端在绕线的时候要注意天线效应比率不能超过rule定的spec。

如果发生antenna violation,要怎样消除呢?一般有两种方法:第一是叫跳层法,说的是把原本很长的一段net打断,在中间打via连到上层或下层,然后再打via连回来。这样在计算天线效应比率的时候就能少算金属层的面积,进而消除violation。

第二种方法是在发生violation的net与地之间插入diode,这样聚集的电荷就会优先走diode这条路,就避免损坏MOS管。

这两种方法都有一定缺点,第一种方法会产生更复杂的绕线,并且会影响原net的timing等,而第二种方法产生更复杂绕线的同时还要加入额外的器件,cell density比较高的情况下就更难摆放。

-

MOS管

+关注

关注

108文章

2411浏览量

66771 -

芯片制造

+关注

关注

10文章

622浏览量

28805 -

天线效应

+关注

关注

0文章

7浏览量

8053

发布评论请先 登录

相关推荐

简单说一说什么是天线效应?消除的办法有哪些?

简单说一说什么是天线效应?消除的办法有哪些?

评论