不知道大家有没有想过,拿到手一个标准单元的lib,它里面的那些参数是怎么得出来的?我们做出来的芯片成品,真的会按lib里描述的那样,timing的值分毫不差吗?

可能很多人觉得在仿真工具上这个芯片完全没问题,流片出来的就也一定没问题,其实不一定。这些lib都是由fab做好了之后给我们的,而他们要保证自己的lib没有问题,就一定要进行流片后的测试。

其实芯片在流片出来之后,我们所能观察的手段就非常有限了,应用最多的方法就只是伸进去一个探针,来测芯片某一点的逻辑信号。但只要用这种方法,再加上一些特别的设计,就可以达到测试标准单元timing的目的!

具体的设计方法可以总结为:把相同的cell串成环,通过反馈电路让他们自己起振产生震荡波形,而后用探针来测输出波形,并与仿真波形比对,就可以推出cell的性能是否真的如lib里写的那样。整个设计非常类似环形振荡器(ring oscillator)。

这种方法实现的原理是ring出来的震荡波的频率是由cell的delay决定,如果测出来的频率和仿真的频率不一致,就说明仿真时用的cell delay不对,就说明lib有问题。反之如果频率能对上,就说明lib的某一部分没有问题。

这种测试电路的设计也需要注意很多问题。比如说,要尽可能覆盖多的使用场景,假设测一个buffer的delay,为了测出不同input transition和output load组合时delay的大小,设计ring的时候就要做出不同组合。

其次我们不希望绕线过多影响结果,cell就摆的很近,让绕线尽量短,并且cell都会摆的很规整。而且为了避免芯片其它部分的影响,还会围boundary等等。

这种思路其实不仅仅可以测delay,还可以测很多东西,比如OCV相关的,POCV的分布,就可以用header控制每个cell。

当ring的cell数最多时,测出的频率最靠近mean的频率,而后依次减少ring cell的数量,就可以测出频率的sigma。还有很多,但核心思想都是来测ring的震荡波形。

另外不仅仅可以测cell,还可以测一些绕线的pattern,比如两根很长的平行metal制造出来是不是会有short,可以用已知的cell,连很长的线来做ring。

其实我也只知道测试原理了,真正设计这种测试电路也会很复杂的。想想我们平常拿到手的lib,也是要很多人花费非常多心血的。

-

环形振荡器

+关注

关注

1文章

12浏览量

8735 -

OCV

+关注

关注

0文章

25浏览量

12579 -

POCV

+关注

关注

1文章

6浏览量

12475

发布评论请先 登录

相关推荐

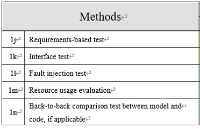

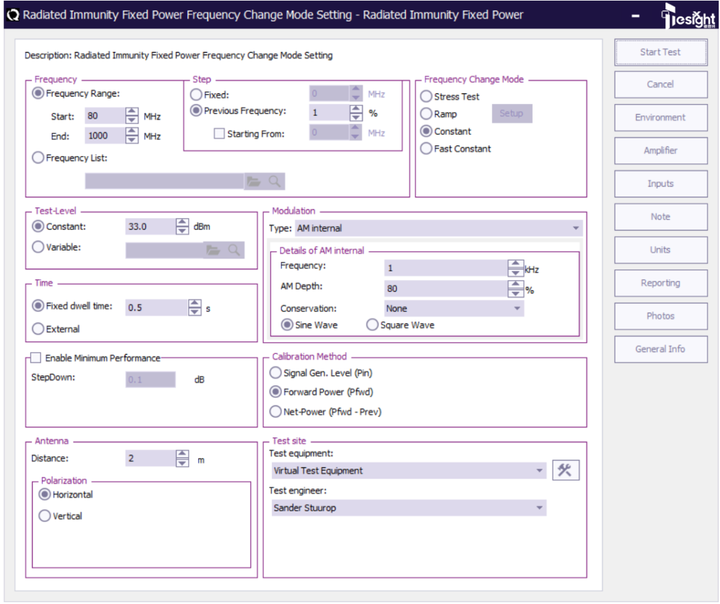

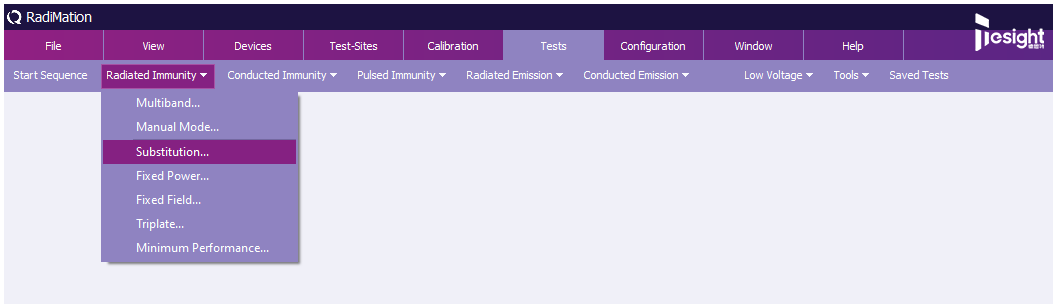

辐射发射测试新境界:深入解析RadiMation套件多种操作方法(五)

ESD器件的测试方法和标准

一种基于光强度相关反馈的波前整形方法

光纤测试方法有哪三种

rup是一种什么模型

性能测试的实现方法是什么

IC设计中值得解决的小问题(一)

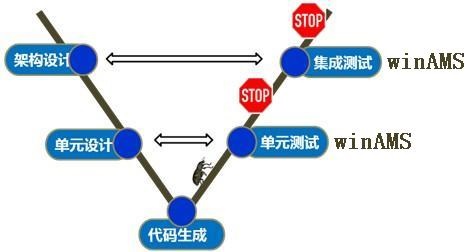

单元/集成测试服务

介绍一种测试标准单元lib的方法

介绍一种测试标准单元lib的方法

评论