佳能日前开始推广其型号为“FPA-1200NZ2C”的半导体纳米压印设备,该工具可将带有电路图案的掩模压印到硅晶圆上。该技术不同于 ASML EUV 工具中专门用于将图案投影到掩模上的光学机制。

专家告诉《EE Times》,佳能技术面临着几个障碍,包括精度不够和对华设备销售的潜在限制。

“半导体研发机构 imec 的项目经理塞德里克-罗林(Cedric Rolin)说:”纳米压印技术很难在质量上与 EUV 相媲美。” 他说,纳米压印的缺陷率“相当高”。

Gartner研究副总裁Gaurav Gupta说,至少在两年内,ASML作为世界上唯一能够制造2纳米节点及以上芯片的光刻设备供应商,其地位可能是稳固的。

他补充说,佳能的设备很可能会受到出口管制的限制。

“如果它能正常工作,而且产量和吞吐量已经得到解决,我预计至少需要两到三年或更长时间才能被使用于大批量生产中,”他说,“前提是它能实现承诺的目标。根据我的经验,这种变革性的技术,需要更长的时间才能看到实际商用的迹象。

佳能的新闻声明称,佳能纳米压印光刻(Nano-Imprint Lithography,NIL)技术可实现最小线宽14nm的图案化,对应5nm节点逻辑半导体。此外,随着掩模技术的进一步改进,NIL有望实现最小线宽为10nm的电路图案,相当于2nm节点。

古普塔表示,这项技术的证据将随着商业采用而出现:

”一旦芯片制造商部署了这种技术,并表示产量和吞吐量与传统光刻技术相当或接近,我就会更有信心。此外,如果它能实现5nm节点,那就意味着它能轻松实现28nm或14nm节点。为什么日本或其他地方还没有人采用它呢?如果它真的那么有前途,为什么要等到只在5nm逻辑上才准备好这项技术,为什么不在更早或更成熟的节点上?

Semiconductor Advisors 总裁 Robert Maire 在向 EE Times 提供的时事通讯中表示,纳米压印技术可能在存储芯片生产中具有潜在应用,因为存储芯片比逻辑更能容忍缺陷问题。他补充说,纳米压印的分辨率较低,远非“现实世界”的大批量制造解决方案。

“缺陷和对准一直是纳米压印的老大难问题和局限性,”Maire 说。“我们确实赞赏佳能公司通过日本公司所擅长的不懈工程取得的卓越进展,但基本的技术限制仍然存在。”

佳能表示,纳米压印工具的一个优势是碳足迹较小。

该公司表示,由于新产品不需要特殊波长的光源,因此与光刻设备相比,它能显著降低功耗。ASML的EUV设备需要消耗大量能源来蒸发锡滴,而锡滴发射的EUV光波长极短,仅为 13.5nm。

传统的光刻技术不仅需要昂贵的光源,还需要复杂的透镜、滤镜、反射镜等光学元件,以及精密的机械结构和控制系统。纳米压印技术则相对简单得多,据说纳米压印技术能够降低40%的制造成本,并且减少90%的耗电量。

此外,佳能表示,传统的光刻技术需要多次重复照射晶圆,每次都要调整位置和角度,还需进行化学处理和清洗等步骤。纳米压印技术则可以一次性完成整个晶圆上所有图形的复制,据说佳能纳米压印设备每小时可以制造100片以上晶圆,基本达到了大规模生产的水平。

Maire指出,佳能在2014年收购德克萨斯州的Molecular Imprints公司时购买了部分纳米压印技术。这可能会使佳能的工具受到美国对华敏感技术出口管制的限制。

-

半导体

+关注

关注

335文章

27826浏览量

223860 -

EUV

+关注

关注

8文章

608浏览量

86199 -

纳米压印

+关注

关注

0文章

11浏览量

6515

发布评论请先 登录

相关推荐

hyper内存条,hyper-v 添加虚拟机还需要硬盘吗

政策与技术并行,共推Robotaxi商业化进程?

简述光刻工艺的三个主要步骤

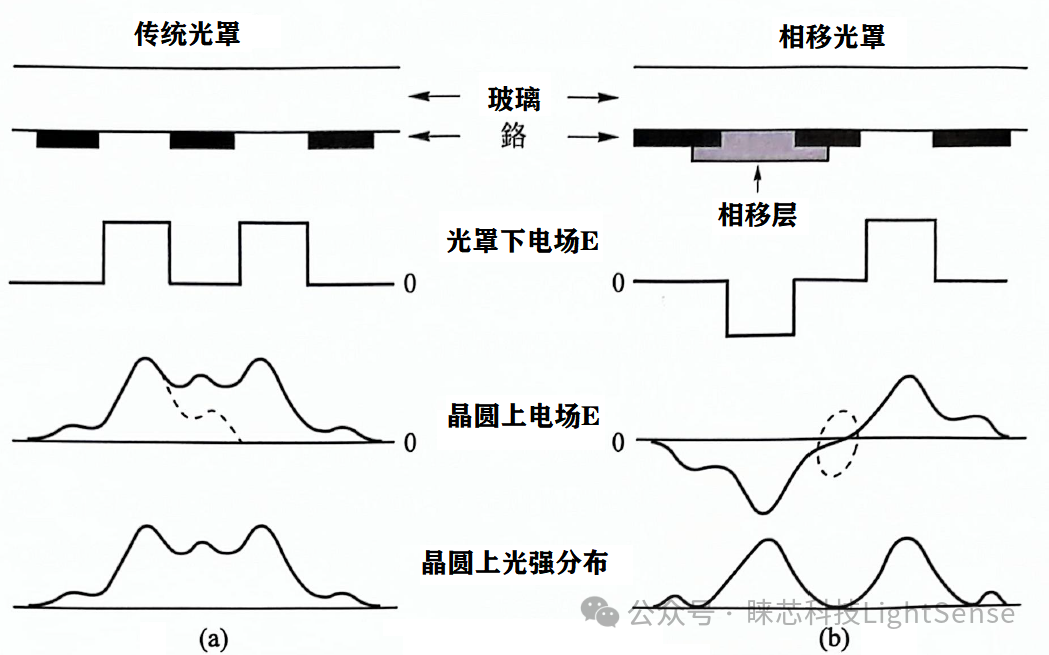

光刻工艺中分辨率增强技术详解

为什么FPGA属于硬件,还需要搞算法?

光刻工艺的基本知识

有了MES、ERP,为什么还需要QMS?

佳能的光刻工具距离商业化还需要数年时间

佳能的光刻工具距离商业化还需要数年时间

评论