半导体器件的制造由许多步骤组成,这些步骤必须产生定义明确的结构,并且从一个器件到下一个器件的偏差很小。每一步都必须考虑之前和随后的制造步骤,以确保实现所需的高制造质量。大多数过程都是在真空腔室中通过引入不同的气态化学物质进行的,这些化学物质通过与基材反应来改变表面。IC最小特征的形成被称为前端制造工艺(FEOL),本文将集中简要介绍这部分,将按照如下图所示的 22 nm 技术节点制造 FinFET 的工艺流程,解释了 FEOL 制造过程中最重要的工艺步骤。

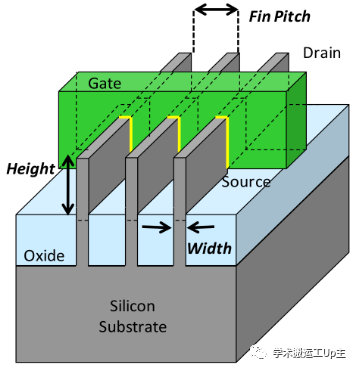

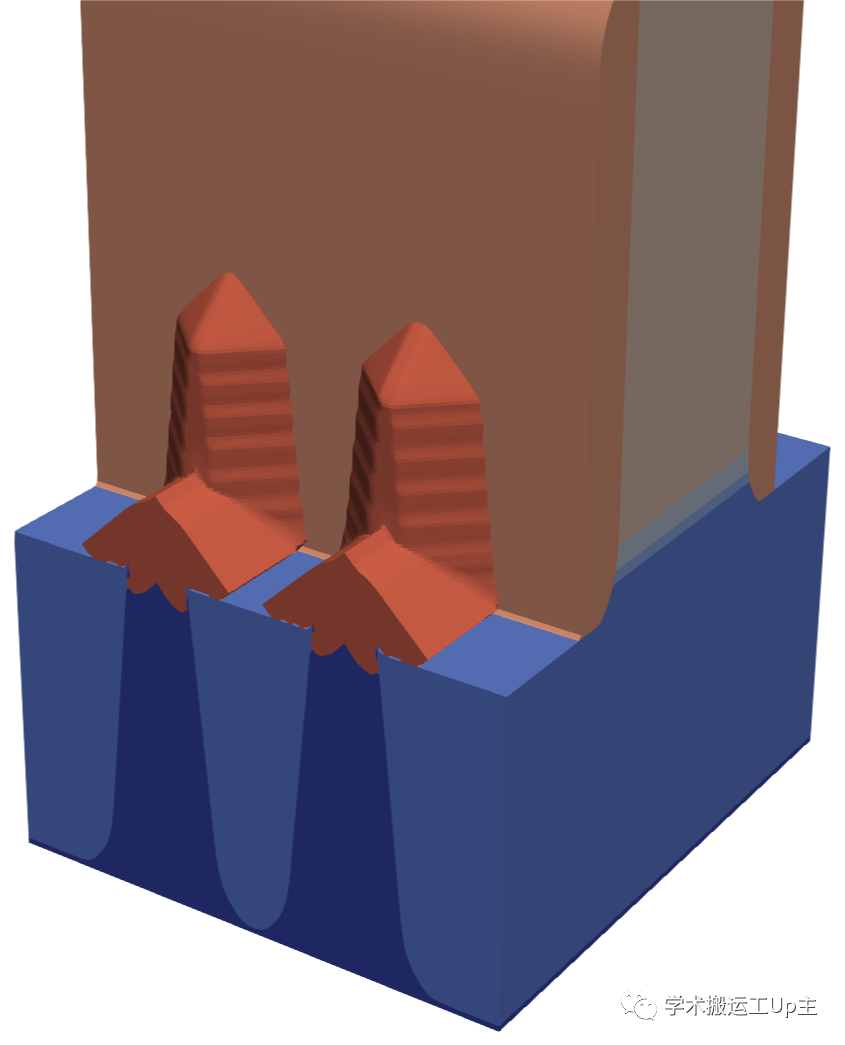

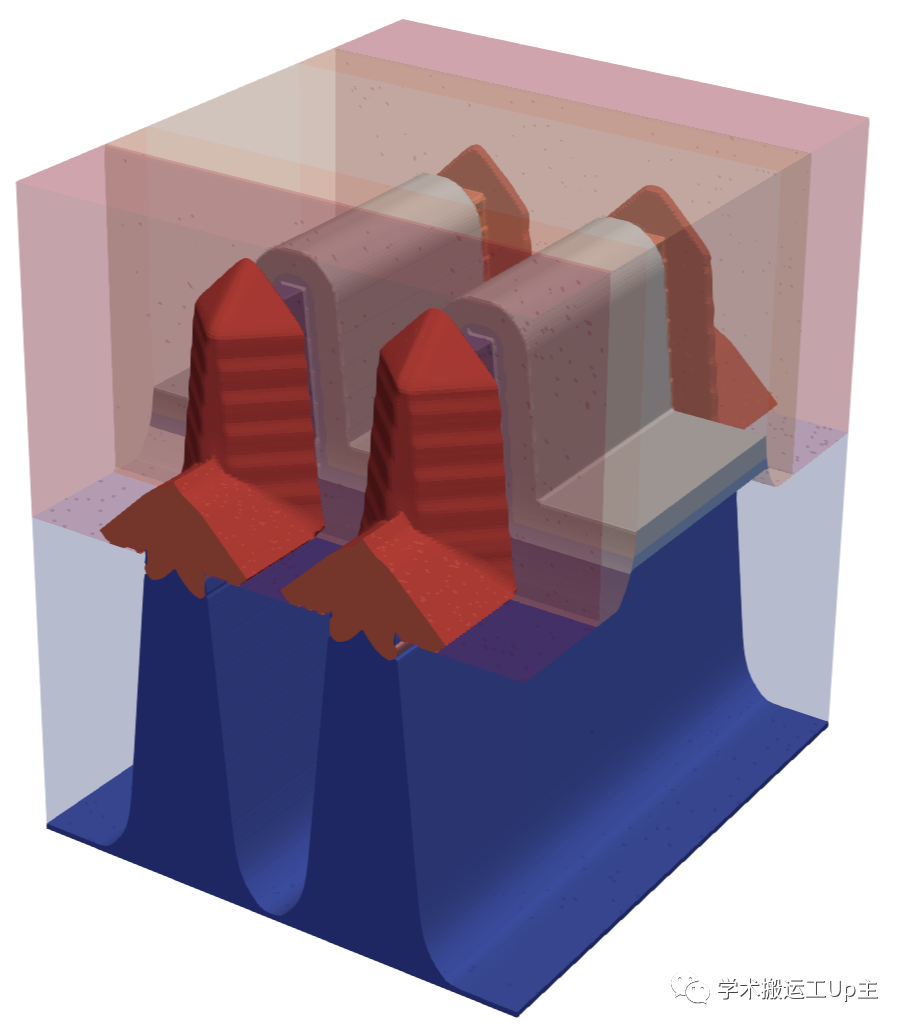

22 nm 技术节点的 FinFET图示(分别具有单个栅极和三个源极和漏极触点)

下面给出最重要的制造步骤的图示, FinFET制造的FEOL步骤通常类似于以下内容:

- 起始过程一般从清洁和抛光的晶体硅晶片开始。

- 光刻:为了形成未来的导电通道,即鳍片(fin),使用光刻技术制造掩模,其中只有某些区域被掩模材料覆盖。平版印刷工艺具有最大分辨率,这取决于所用光的波长。常用的193 nm波长的紫外光可以达到的最小尺寸约为30 nm。为了实现更小的特征,使用了自对准双图案化(SADP),通过使用化学气相沉积(CVD)各向同性地沉积薄层来产生更小的掩模。然后使用反应离子蚀刻 (RIE) 定向蚀刻该薄层,留下沉积材料的薄柱,然后用作掩模,如下图所示:

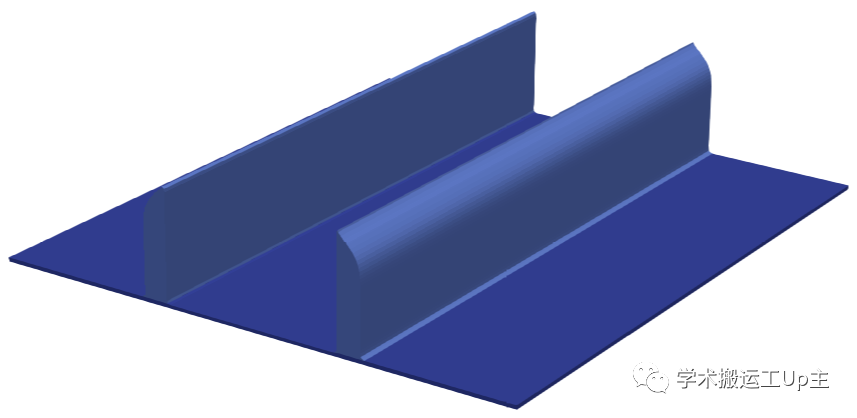

SADP掩模版在Si衬底上

使用生成的柱子作为初始掩码再次重复此过程称为四重图案 (QP)。为了避免这些复杂的多重图案化技术,一些制造商已经实现了极紫外(EUV)光刻技术。

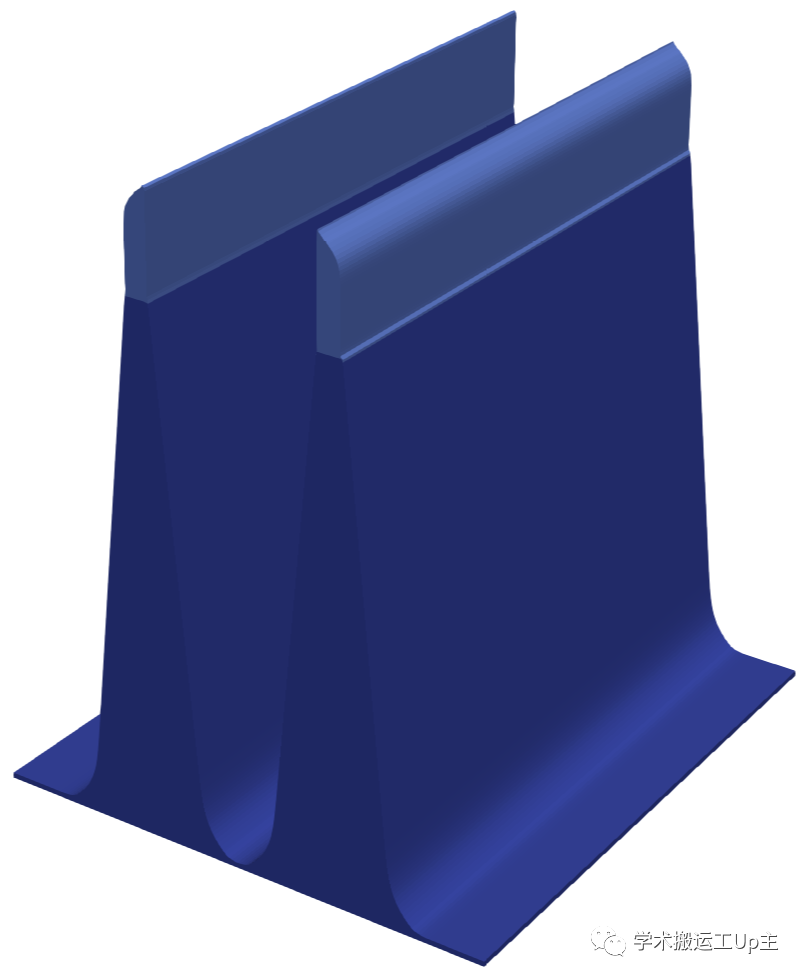

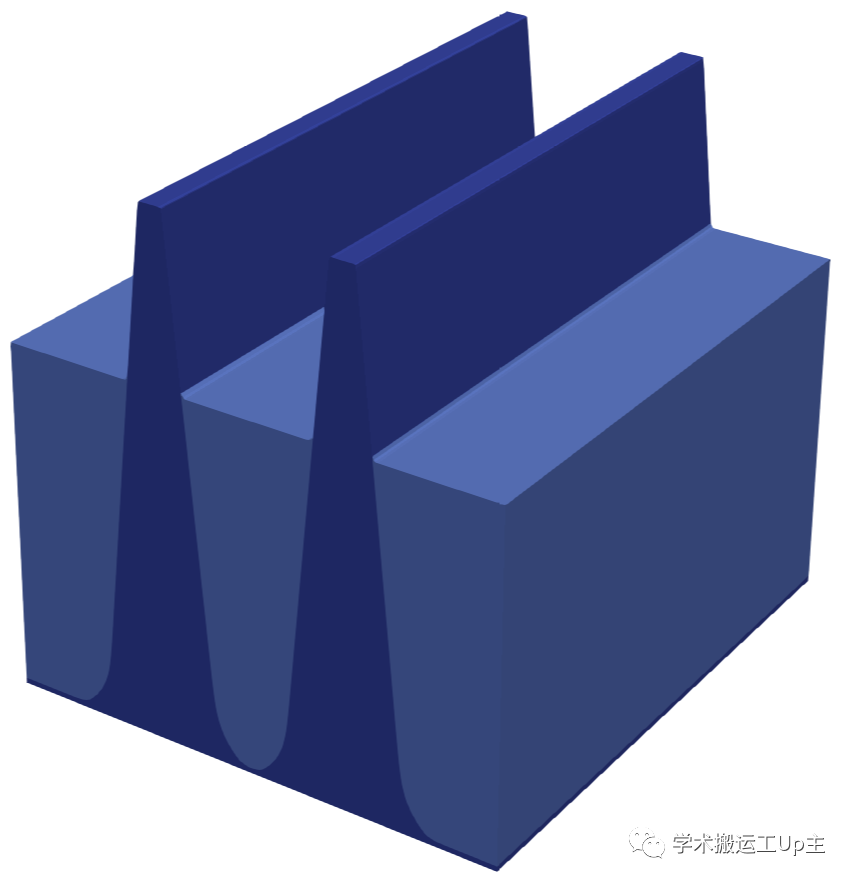

- fin图案化:在这个阶段,晶体硅衬底被蚀刻,在掩模下方留下fin,随后形成MOSFET的导电沟道。如下图所示,对蚀刻过程进行调整,使fin呈正锥形,从而向底部增加宽度。

硅fin通过刻蚀硅实现

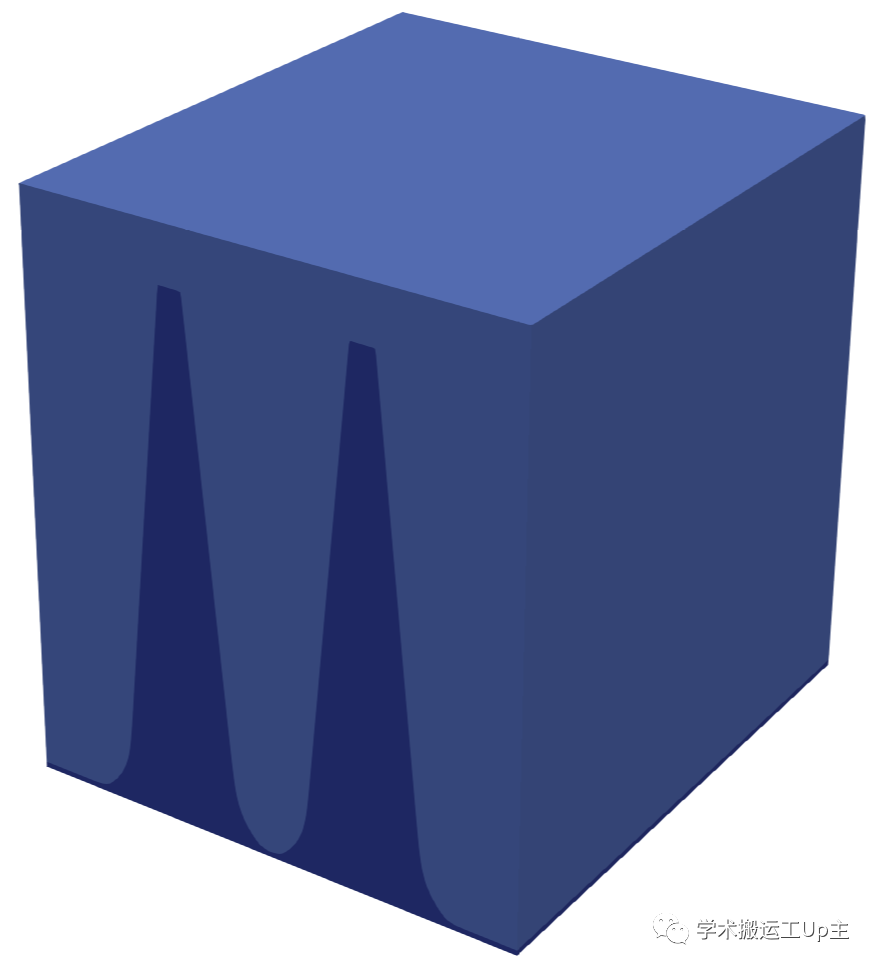

- 浅沟槽隔离 (STI):由于每个fin可能是不同晶体管的一部分,因此它们必须相互电绝缘。这是通过在各处沉积介电材料来实现的。然后使用化学机械平坦化 (CMP) 对晶圆进行抛光,以创建如下图所示的平坦化顶面。

STI沉积以电绝缘不同fin

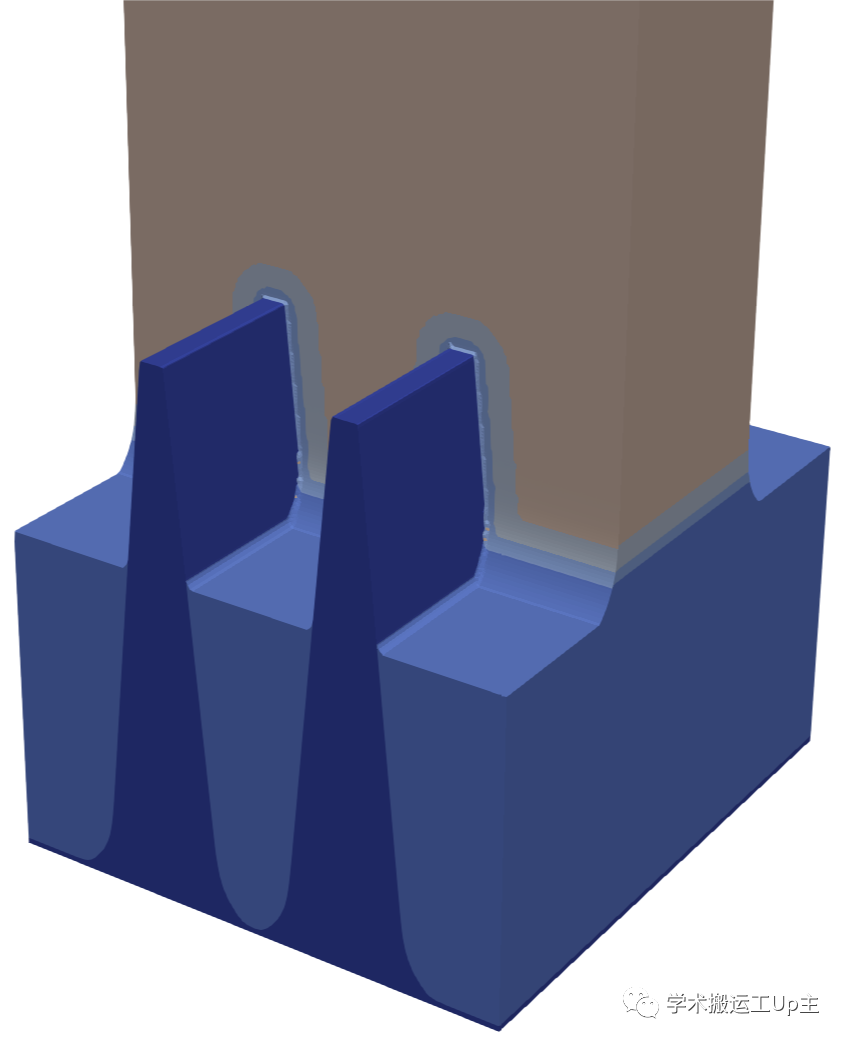

- fin释放:一旦表面抛光,就可以选择性地蚀刻介电材料,使晶体硅完好无损。因此,fin再次被释放并伸出介电材料,如下图所示,同时彼此隔离到足够的深度。

fin被释放以实现栅极与硅接触

- 金属栅极沉积:高介电常数金属栅极通常由三种不同材料的堆叠组成:fin周围具有高介电常数的薄层材料,通常表示为 κ,因此得名 high-k; 另一层稍厚的金属,称为栅极金属; 最后是一层更厚的栅极接触材料,通常是多晶硅(poly-Si)。这些材料使用CVD或原子层沉积(ALD)进行沉积。

- 栅极图案化:在栅极接触材料的顶部,使用光刻技术创建另一个掩模。然后对栅极材料一个接一个地进行蚀刻,使栅极仅覆盖硅fin的中心部分,如下图所示。

栅极沉积及图案化

- 栅极间隔物(Spacer):为了将栅极与源极和漏极 (S/D) 区域电气隔离,使用 CVD 各向同性沉积间隔物介电材料。与SADP类似,RIE随后将其定向去除,仅将聚合物留在浇极材料的侧面。从下图中可以看出,RIE不具有选择性,并且在此制造步骤中硅fin也会被侵蚀。

栅极spacer沉积以电绝缘S/D

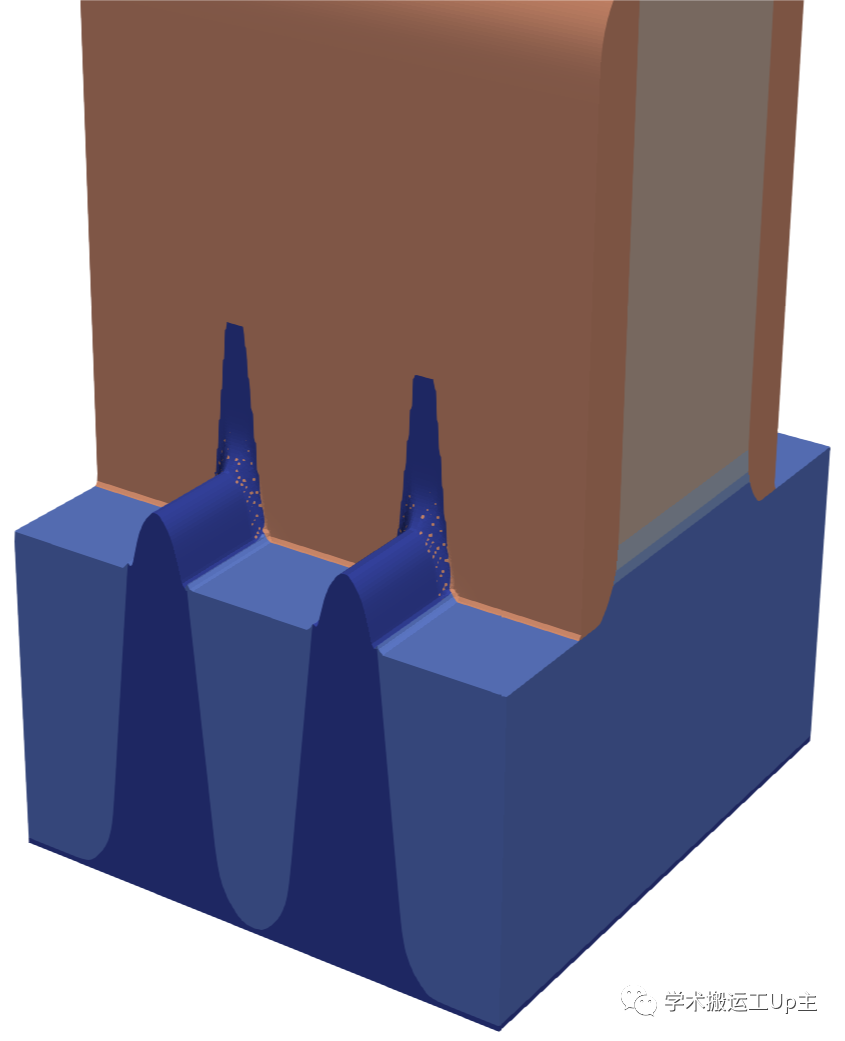

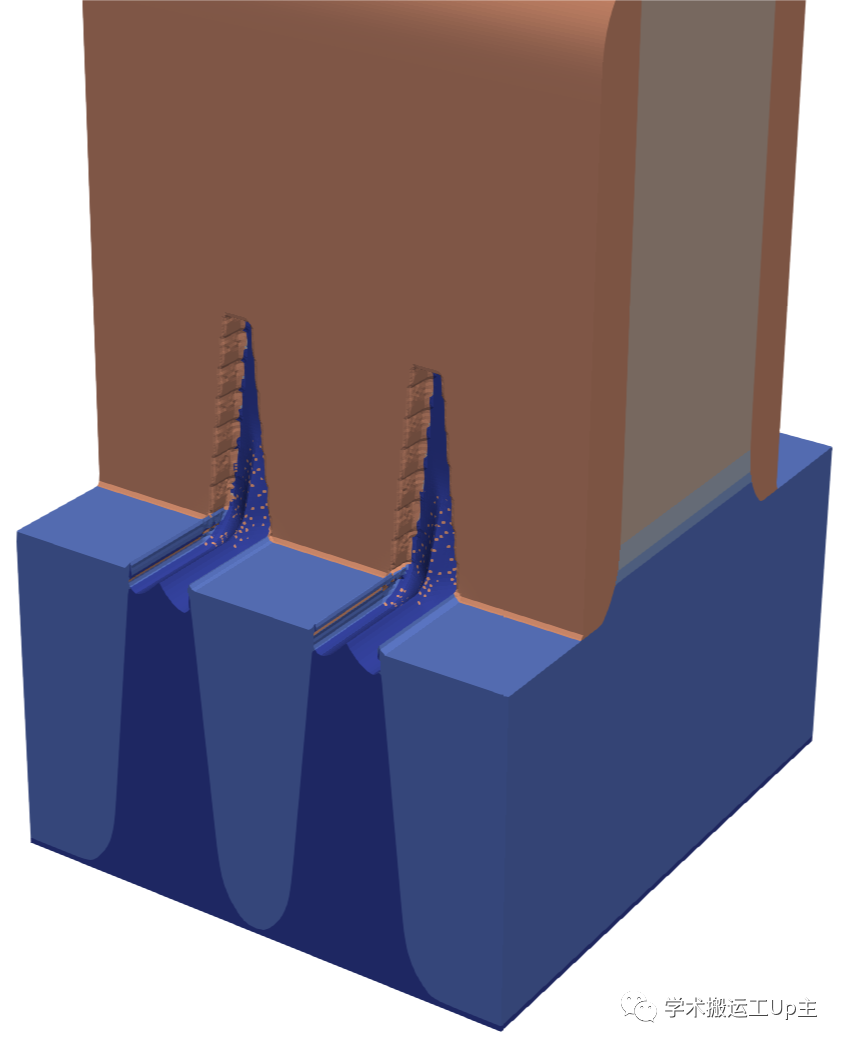

- fin凹槽:然后对硅fin进行蚀刻,以便清洁它们,为后续过程做准备,导致介电材料垫片下方的fin蚀刻不足,如下图所示。

硅fin被刻蚀成凹槽

- 源极和漏极外延:现在已经清洁了fin表面,可以使用外延生长创建晶体 S/D 触点。这种生长速率随晶体方向变化很大,导致在如下图中观察到的特征金刚石形状。

S/D 外延

- 层间介电材料:在使用CMP抛光晶圆之前,沉积另一层介电材料以隔离S/D触点,从而产生如下图所示的最终MOSFET结构,完成FEOL制造。

FinFET的最终结构

FEOL步骤完成后,所有晶体管在工艺金属化过程中连接以形成电路,这是半导体制造工艺后端(BEOL)的一部分。这是分几层进行的,每层的关键尺寸都会增加,最终提供足够大的金属触点,以将IC连接到外围元件。单个晶圆可能包含数百个同时制造的芯片。由于现在所有晶体管和互连都已形成,因此晶圆可以切割成单个芯片。然后,每个芯片都有适合特定应用的转接板(interposer)以完成最后的封装工艺。

-

制造工艺

+关注

关注

2文章

179浏览量

19764 -

22nm

+关注

关注

0文章

51浏览量

18007 -

工艺流程

+关注

关注

7文章

106浏览量

16292 -

半导体器件

+关注

关注

12文章

754浏览量

32069 -

FinFET

+关注

关注

12文章

248浏览量

90254

发布评论请先 登录

相关推荐

透视IVB核芯 22nm工艺3D技术终极揭秘

22nm平面工艺流程介绍

锐成芯微宣布在22nm工艺上推出双模蓝牙射频IP

液晶显示器制造工艺流程基础技术

Intel 22nm光刻工艺背后的故事

台积电又跳过22nm工艺 改而直上20nm

Achronix全球首款22nm FPGA,瞄准高端通信市场

现代集成电路芯片14nm节点FinFET的制造工艺流程详细资料说明

22nm技术节点的FinFET制造工艺流程

22nm技术节点的FinFET制造工艺流程

评论