Redistribution layer (再分布层,RDL),是添加到集成电路或微芯片中以重新分配电气连接的金属层。这种RDL技术是一种用于集成电路(IC)的先进封装解决方案,允许将多个芯片集成到单个封装中。它是在介电层顶部创建图案化金属层的过程,该金属层将 IC 的输入/输出 (I/O) 重新分配到新位置。新位置通常位于芯片的边缘,这允许使用标准表面贴装技术 (SMT) 将 IC 连接到印刷电路板 (PCB)。RDL 技术使设计人员能够以紧凑、高效的方式放置芯片,从而减少器件的整体尺寸。

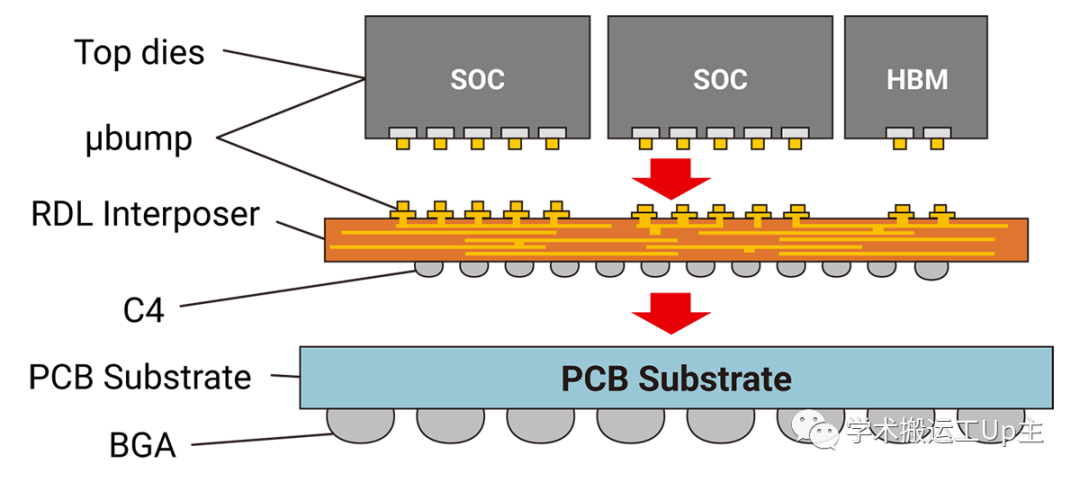

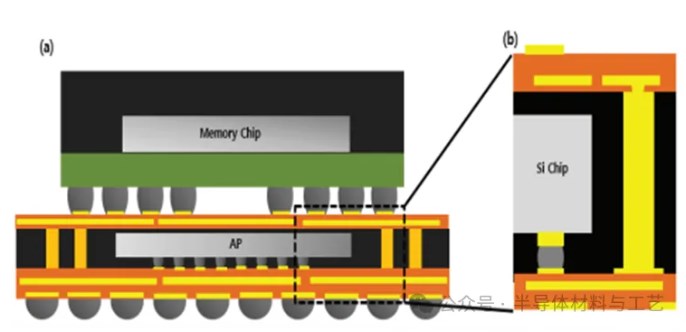

在芯片设计和制造中,再分布层 (RDL) 在扩展和互连 XY 平面方面发挥着关键作用。如下图是CoWoS-R的图示,这是台积电开发的一种3D集成技术,可在单个封装中堆叠多个芯片。(来源:台积电)

RDL 技术带来以下优势:

(1). 重新分配 I/O 连接: I/O(输入/输出)焊盘是芯片引脚处理模块,通常分布在芯片的边缘或外围。它们可以处理芯片引脚的信号,并在处理后将芯片的信号输出到引脚。RDL 有助于将 I/O 连接从芯片重新分配到封装。RDL 将芯片上的焊盘连接到封装引线或焊球,从而简化组装和提高 IC 的性能。

这对于键合线工艺来说自然是方便的,但对于倒装芯片来说却有些挑战。因此,RDL成为这一时刻的关键。它在芯片表面沉积金属层和相应的介电层,形成金属线,并将IO端口重新设计到一个新的、更宽敞的区域,形成表面阵列布局。

(2). 路由信号和电源: 此外,RDL还提供了一种在IC内路由信号和电源的方法。随着IC变得越来越复杂,需要更多的I/O连接,RDL的使用变得越来越重要。它们用于广泛的应用,例如微处理器、存储芯片和传感器。

(3). 减少占用面积: RDL 技术允许将多个芯片集成到单个封装中,从而减小器件的整体尺寸。这使设计人员能够创建更小、更紧凑的电子设备,这对于智能手机、可穿戴设备和物联网设备等应用至关重要。

(4). 提高电气性能: RDL 技术使设计人员能够以紧凑而高效的方式放置芯片,从而缩短互连的长度。这反过来又减少了信号延迟并提高了器件的电气性能。RDL技术还降低了寄生电容和电感,从而提高了器件的信号完整性。

(5). 降低成本: RDL技术消除了引线键合和倒装芯片键合的需要,这些工艺既昂贵又耗时。RDL技术还减少了器件所需的元件数量,从而进一步降低了器件的成本。RDL 技术是一种经济高效的解决方案,用于创建需要小尺寸的高性能 IC。

RDL 技术是一个复杂的过程,涉及许多步骤,例如介电沉积、金属沉积、图案化和蚀刻。再分布层技术基于工艺来说,一般有两种类型的再分布层 (RDL) 技术:扇入和扇出。扇入式 RDL 技术用于封装单个芯片,而扇出式 RDL 技术用于封装多个芯片。

(1). 扇入式 RDL 技术:扇入式 RDL 技术用于封装单个芯片。扇入式 RDL 技术也称为晶圆级封装 (WLP),它是直接在晶圆上建立封装的过程。扇入式 RDL 技术是一种经济高效的解决方案,用于创建小型和薄型封装。

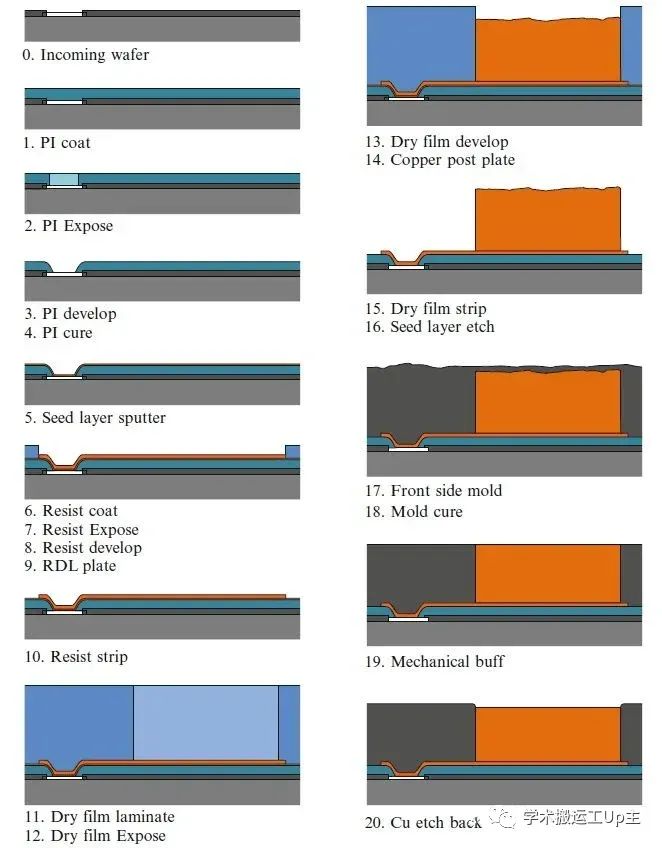

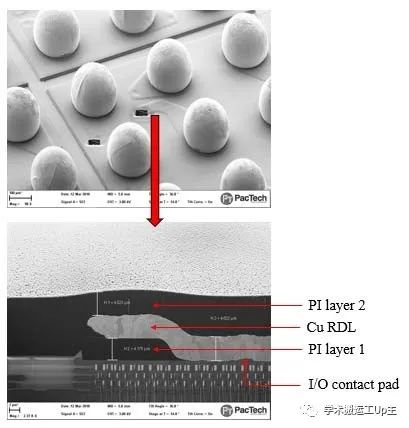

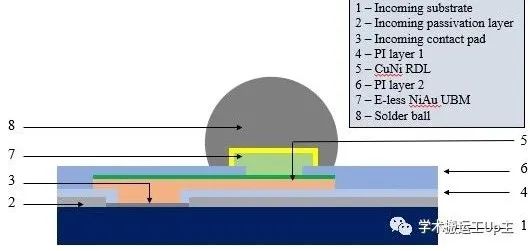

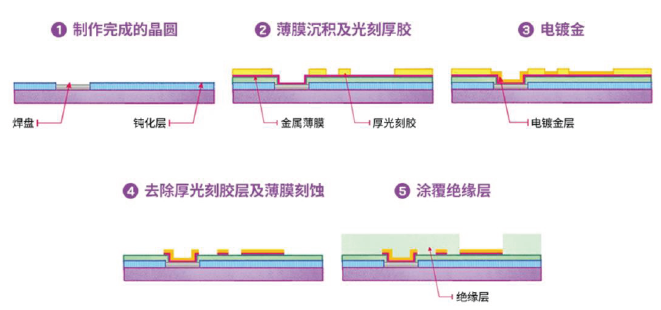

扇入式 RDL 工艺用于生产先进的封装解决方案,例如晶圆级芯片级封装 (WLCSP) 和系统级封装 (SiP) 设计。它允许更高的集成度、更小的外形尺寸和更高的半导体器件性能。该过程涉及以下多个步骤:

该过程从进料晶圆开始,然后在步骤 1 中涂覆 PI(光刻胶绝缘体)。接下来是第 2 步的 PI 曝光、第 3 步的 PI 显影以及第 4 步的 PI 固化。

在步骤5中,将种子层溅射到晶圆上,然后在步骤6中涂上抗蚀剂。然后在步骤7中暴露光刻胶,在步骤8中显影,并在步骤9中镀上RDL。

之后,在步骤10中剥离光刻胶,并在步骤11中将干膜层压到晶圆上。然后在步骤12中暴露干膜,并在步骤13中显影。接下来,在步骤14中将铜柱镀在晶圆上,并在步骤15中剥离干膜。

在步骤16中,对种子层进行蚀刻,在步骤17中,创建正面模具。然后在步骤18中固化模具,并在步骤19中对晶圆进行机械抛光。最后,在步骤20中,多余的铜被蚀刻回去,完成扇入式RDL工艺流程。

扇入式 RDL 技术适用于传感器、MEMS 器件、射频器件、微处理器和存储器件等应用。

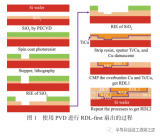

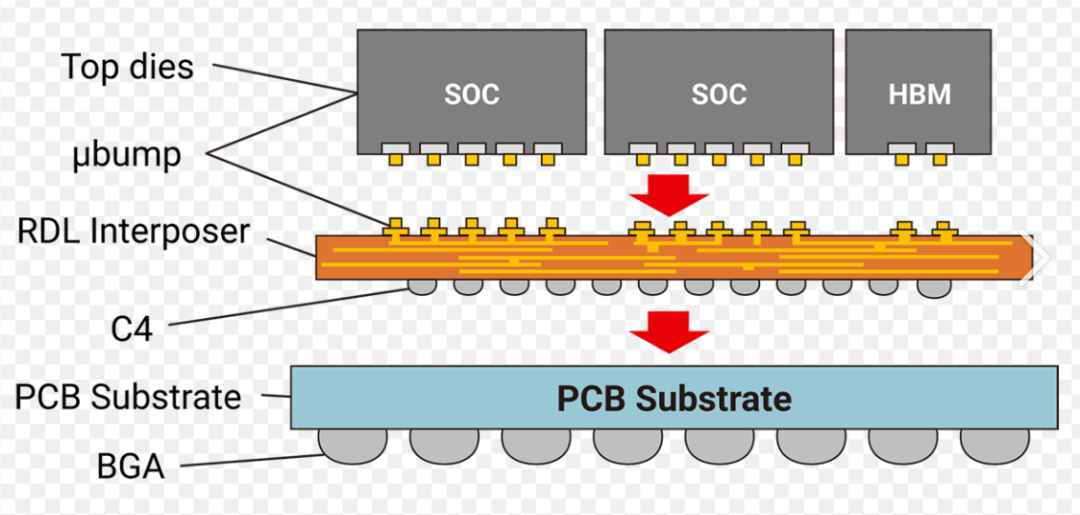

(2). 扇出 RDL 技术:扇出 RDL 技术用于封装多个芯片。扇出 RDL 技术也称为晶圆级扇出 (WLFO),它是在重组晶圆上创建封装的过程。扇出式 RDL 技术是一种经济高效的解决方案,用于创建具有小尺寸的高性能封装。

与扇入式 RDL 工艺类似,扇出式 RDL 工艺也是一种创建具有更多连接的更小、性能更高的芯片封装的方法。以下是制造步骤:

- 晶圆探针:这是对晶圆的初步测试,以确保其符合所需的规格,然后再进行后续的加工步骤。

- 晶圆背磨:将晶圆的背面研磨到规定的厚度,以减小封装的厚度。

- 晶圆切割:将晶圆切割成单独的芯片。

- KGD(已知合格芯片)拾取和放置:将合格的芯片拾取并转移到带有粘合剂的载体晶圆上。

5a. 晶圆模具:将芯片附着在载体晶圆上的晶圆用介电材料模制而成,形成扇出结构。

5b. 载体和临时胶粘剂去除:将载体晶圆从扇出晶圆上取下,并去除过程中使用的任何临时胶粘剂。

5c. 扇出晶圆清洁:扇出晶圆经过清洁以去除任何残留的颗粒或杂质。

- 聚合物1涂层:在扇出晶圆的表面涂上聚合物层,作为介电层。

- 聚合物1 成像/显影/固化:使用光刻技术对聚合物层进行图案化,以创建所需的 RDL 结构形状和尺寸。

- RDL种子层溅射:使用溅射在聚合物层的顶部沉积一层薄薄的铜或其他导电材料。

- 光刻胶涂层:在种子层上涂上一层光刻胶材料。

- 光刻胶成像/显影:使用光刻技术对光刻胶层进行图案化,以创建所需的 RDL 结构形状和尺寸。

- RDL铜图案板:使用电镀将铜沉积在种子层的暴露区域的顶部,从而形成所需的RDL图案。

- 光刻胶去除:去除剩余的光刻胶材料,只留下铜RDL图案。

- 种子层蚀刻:使用蚀刻去除种子层中不需要的部分。

- 聚合物2涂层:在RDL结构的顶部施加另一层聚合物层,作为介电层。

- 聚合物2 成像/显影/固化:使用光刻技术对聚合物层进行图案化,以创建所需的形状和尺寸的 UBM 结构。

- UBM晶种层溅射:使用溅射在聚合物层的顶部沉积一层薄薄的铜或其他导电材料。

- 光刻胶涂层:在种子层上涂上一层光刻胶材料。

- 光刻胶成像/显影:光刻技术对光刻技术对光刻胶层进行图案化,以创建所需的 UBM 结构形状和尺寸。

- UBM图案板:使用电镀将铜沉积在种子层的暴露区域的顶部,从而形成所需的UBM图案。

- 光刻胶去除:去除剩余的光刻胶材料,只留下铜UBM图案。

- 种子层蚀刻:使用蚀刻去除种子层中不需要的部分。

- 助焊剂贴印:将助焊剂材料应用于UBM焊盘。

- 锡球掉落:将锡球放在 UBM 焊盘上。

- 回流焊:将焊球加热熔化,并在 UBM 焊盘和外部引线或凸块之间形成连接。

- 扇出晶圆探针:对封装的IC进行测试,以确保其符合所需的规格。

- 激光标记:使用激光将唯一标识符或条形码蚀刻在IC表面。

- 晶圆切割:将扇出的晶圆切割成单独的封装。

- 编带包装:单个封装的 IC 安装在卷轴上,便于处理和运输。

-

集成电路

+关注

关注

5463文章

12669浏览量

375607 -

半导体

+关注

关注

339文章

31192浏览量

266321 -

晶圆

+关注

关注

53文章

5445浏览量

132713 -

芯片设计

+关注

关注

15文章

1170浏览量

56775 -

系统级封装

+关注

关注

0文章

44浏览量

9391

发布评论请先 登录

一种新型RDL PoP扇出晶圆级封装工艺芯片到晶圆键合技术

新型WLCSP电路修正技术

集微连线:板级封装潜力无穷 RDL工艺勇挑大梁

华为一种芯片堆叠工艺解读

高通量芯片流体分布层结构

Manz亚智科技RDL制程打造CoPoS板级封装路线, 满足FOPLP/TGV应用于下一代AI需求

Manz亚智科技RDL制程打造CoPoS板级封装路线,满足FOPLP/TGV应用于下一代AI需求

芯片设计中再分布层(RDL)技术的优势

芯片设计中再分布层(RDL)技术的优势

评论