尽管 FPGA 为嵌入式设计带来了强大的功能与灵活性,但额外的开发流程也给设计工作增加了新的复杂性和限制问题。整合传统的硬件-FPGA-软件设计流程并充分利用 FPGA 的可再编程功能是我们的一个解决之道。

随着 FPGA 技术逐步延伸至军事电子系统以及嵌入式电子产业的几乎全部领域,能发挥可编程逻辑优势的应用已经占据主流地位。通信、机载和控制系统尤其受益于 FPGA 的设计灵活性、现场重构和并行处理功能。同时,较短的设计周期和更加简化的验证过程则有助于加快应用投入现场的进程。

尽管 FPGA 无所不在,但能真正全面发挥FPGA 灵活设计潜力的应用却很少。之所以存在这种局限性,原因在于 FPGA 开发很大程度上只是简单地叠加,或者最多也只是连接于传统的软硬件工作流程上。这个孤立的 FPGA 开发阶段会导致整个设计流程的复杂性大幅上升——并最终限制软硬件领域可用的设计选择范围。

为了简化整体设计工作,并丰富设计选项,硬件设计、软件开发和可编程硬件设计等独立的设计过程需集成在一起,以作为一个整体的任务进行处理。只有在基础层面上让所有设计进程都能共享统一的设计数据库和通用的设计环境,FPGA 的可再编程性这一最主要的独特优势才能得到充分发挥,从而将 FPGA 设计推向前所未有的水平。全面发挥 FPGA 灵活性优势的关键在于了解其发展趋势及所面临的设计挑战,并掌握如何让包含 FPGA 系统中的三大设计方面(硬件、可编程硬件和软件)实现协调整合。

FPGA 从胶合逻辑向 SoC 方向发展

FPGA 刚进入嵌入式市场领域时,被认为是用于实施大量简单胶合逻辑的方便而有效的替代技术。在这种应用中,嵌入式硬件是主要软硬件设计的附属部分,其开发过程不涉及其他组件的设计流程,也不需要与这些流程进行交互。

不过,现在的 FPGA 器件及其使用方式已经在海量数字逻辑便捷容器概念的基础上发生了重大变化。大容量 FPGA 现在能承载整个 SoC 设计,其中处理器、内存以及高速数据处理等核心功能元素都在可编程领域实施。在军用嵌入式系统中,由于受产量相对较低的影响,很难采用 ASIC 设计方案,而 FPGA 则为充分发挥 SoC 设计方案的物理简单性和可靠性等优势提供了一条经济高效的可行之道。

相对于简单的胶合逻辑设计而言,SoC 实施的一个重大不同点在于,软硬件开发现在基本上都是关联于、且依赖于 FPGA 设计。这是因为 FPGA 器件和支持外设是物理设计的中心与核心元素,而嵌入式应用软件也要装载在 FPGA 上发挥作用。因此,FPGA 域的任何更改都会对软硬件域造成显著影响。

受限制的创新

如果将硬件、软件乃至当前的嵌入式硬件等设计的各个部分视作是彼此分开、互不关联的任务,则无论设计域之间如何相互依存,FPGA 产品设计的常规开发流程采用的仍然是传统方案。

某个设计域的变动往往会对其他域造成具有破坏性影响且耗时巨大的重新设计。也就是说,必须在设计阶段早期就做出(并且锁定)软硬件分区等重大决策,这与传统的非 FPGA 嵌入式设计别无二致。实际上,FPGA 器件和外设硬件等物理硬件和随后的可编程硬件元素在有意义的软件开发之前都被依次一一锁定了。

这些最初的决策决定了后续开发流程的参数和限制,因此设计的可选项会随着流程的逐步推进而越来越少。例如,选定的 FPGA 器件(和硬件外设)将定义包括确定采用哪种嵌入式 IP 等在内的性能上限,嵌入式硬件设计进而定义软件可用的功能。或者说,FPGA 器件只能支持该器件厂商提供的软处理器,这进而也定义了应用软件可用的编程选择。

此外,要想微调设计方案的性能,比如将软件算法转移到嵌入式硬件中、或者从嵌入式处理器转为硬连接的处理器、抑或是选择不同的 FPGA 类型等,都会导致对硬件、可编程硬件和软件等所有域进行大规模重新设计。对开发时间紧迫的军事/航空系统而言,这种重新设计对设计周期造成的中断影响极大,因此大多数工程师都会全力避免这种设计风险的发生。不过,高性能和设计稳定性同样至关重要,因此检查处理器选项并充分利用软算法的优势来替代硬算法也是必不可少的。

重建一体化

如前所述,简单地在现有的设计工作流程中添加 FPGA 开发流程难以充分发挥 FPGA 的全部优势。对于需要降低 NRE 成本、加快设计速度的应用而言,传统设计方法所带来的局限性会抵消这种优势;而这正是 FPGA 应当发挥最大作用的地方。

恢复设计选择和全面发挥 FPGA 优势的第一步就是让硬件设计、软件开发和可编程硬件设计等统一起来。通过使用来自整体设计统一数据模型中的一体化设计系统和应用,设计域可随各域中设计的变化而实现交互和及时响应。在实践中,各个域采用的都是同一设计和组件库数据中的子集。由于更改可以方便地(甚至是自动地)反映在所有设计领域中,因而可以显著简化设计更改,如在软件与硬件之间进行功能转移,或探索其他器件等。

例如,在统一设计数据池中,针对选定 FPGA 器件的设计数据和配置文件可同时适用于硬件和 FPGA 设计领域。如果 FPGA 器件或其引脚配置在 FPGA 设计阶段进行了更改,该信息会立即用于硬件设计的实施。这样,我们探索不同设计选择就能变得更加有效,而且硬件和FPGA设计域之间的引脚交换等高级设计功能也得以简化。

充分利用可再编程性

在这种一体化的设计环境中,开发人员终于能够充分发挥 FPGA 的灵活性了。例如在典型的环境中,物理硬件组件的大多数实际放置位置会造成 FPGA 与外设的连接极为复杂,而这一方面也是高密度 BGA 封装造成的问题。解决方法之一就是在 FPGA 内部来解决部件之间布线的复杂性,通过 FPGA 可重新配置的引脚和内部布线功能来实现板上连接线路的战略安排。

我们在这里用 FPGA 的引脚再分配和内部布线功能解决板上布线难题,还有可能减少板上空间占用和层数要求。这一理念同样依赖于平台级的软硬件与 FPGA 开发环境,只有这样才能支持硬件与 FPGA 域之间的智能和自动引脚交换。

此外,这种一体化设计方案还将实施可提升设计流程抽象程度的全局软件系统变成了一种可能,如可采用图表或图形化嵌入式设计方法,实现软硬件域的同步。由于数据已经作为贯穿于一体化设计环境所有域的统一实体而存在,所以与采用一系列独立工具的系统不同的是,单个域中较高级的设计抽象不会增加设计数据流的复杂性。

这种设计抽象的自然延伸的目的是实施软件元素与其所依附硬件能有效分离的高级嵌入式层。这些插入的层实现了处理器与其他硬件(如内存和外设)之间接口的标准化,因而无需再考虑 I/O 配置和总线系统的底层硬件复杂性问题。无论是进行传统设计更新、不同产品模式配置、现有 IP 重用,还是执行生产后期升级,FPGA 设计的再配置都将成为一个更简单、更低风险的过程。

在实践中,采用 Wishbone 总线架构、基于库的 FPGA 内核可同时支持处理器和外设。通过有效“包裹”器件,使其在架构上等同于其他处理器,该内核可以提取处理器接口,从而能够根据需要修改处理器,而不会影响与其相连的外设,或者造成设计方案的被迫大幅修改。除了基于 FPGA 的“软”器件之外,上述理念还可扩展适用于混合型硬内核处理器、外部处理器以及片外独立外设和存储器器件。

新一代 FPGA 设计

本文介绍的一体化高级设计方法是通过发挥 FPGA 主机的可再编程功能实现的。所有应用的层和接口以及功能设计本身都自动包含在 FPGA 系统中。因此,与适用于“固定”ASIC 类 SoC 设计的传统流程不同,功能相当的高级 FPGA 能在不严重影响设计方案其他部分的情况下动态探索不同的硬件设计选择。

欢迎关注至芯科技

至芯官网:www.zxopen.com

至芯科技技术论坛:www.fpgaw.com

至芯科技淘宝网址:

https://zxopen.taobao.com

至芯科技FPGA初级课程(B站):

https://space.bilibili.com/521850676

至芯科技FPGA在线课程(腾讯课堂):

https://zxopenbj.ke.qq.com/

至芯科技-FPGA 交流群(QQ):282124839

更多资料下载欢迎注册http://www.fpgaw.com

扫码加微信回复加群

邀请您加入FPGA学习交流群

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:FPGA为嵌入式设计带来了强大的功能与灵活性

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1630文章

21796浏览量

605847

原文标题:FPGA为嵌入式设计带来了强大的功能与灵活性

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

嵌入式和人工智能究竟是什么关系?

【「嵌入式Hypervisor:架构、原理与应用」阅读体验】+全文学习心得

飞凌嵌入式「在线文档」功能上线 | 开放灵活,尽在掌握

嵌入式热门领域有哪些?

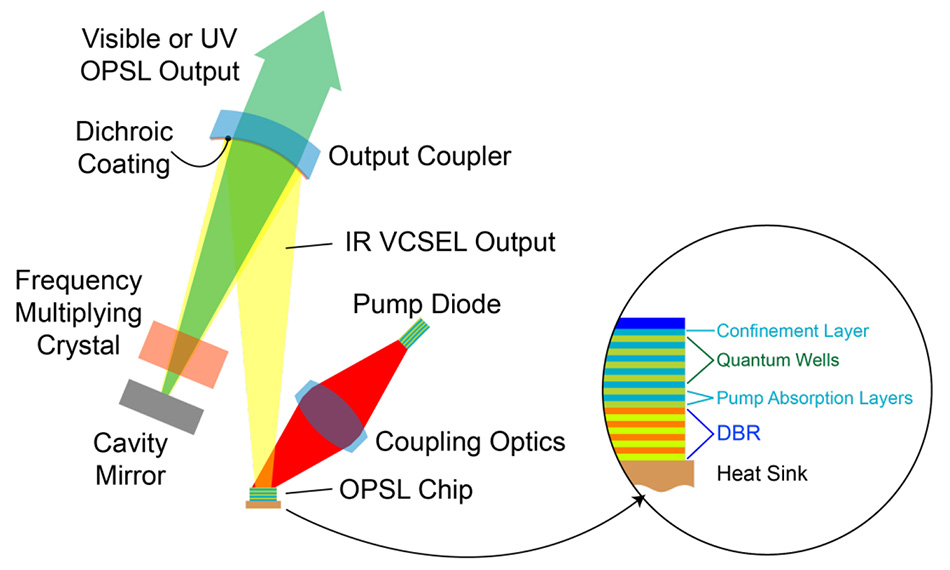

OPSL 优势1:波长灵活性

简谈Xilinx Zynq-7000嵌入式系统设计与实现

简谈Xilinx Zynq-7000嵌入式系统设计与实现

嵌入式可编程片上系统是什么

英特尔锐炫A系列显卡为客户提供了强大的性能和灵活性

FPGA为嵌入式设计带来了强大的功能与灵活性

FPGA为嵌入式设计带来了强大的功能与灵活性

评论