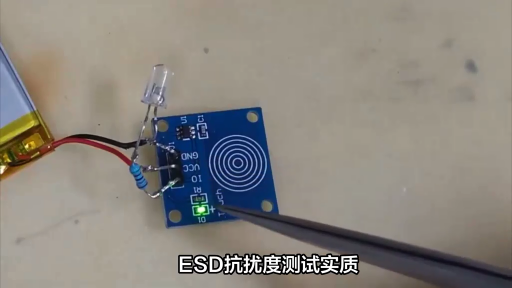

ESD抗扰度测试实质

从ESD测试配置可以看出,在进行ESD测试时,需要将静电枪的接地线接至参考接地板(参考接地板接安全地),EUT放置于参考接地板之上(通过台面或0.1m高的支架),静电放电枪头指向EUT中各种可能会被手触摸到的部位或水平耦合板和垂直耦合板,就决定了ESD测试时一种以共模为主的抗扰度测试,因为ESD最终总要流向参考接地板。

ESD干扰原理也可以从两方面来讲。首先,当静电放电现象发生在EUT中被测部位时,伴随着ESD放电电流也将产生,分析这些ESD放电电流波形的上升沿时间会在1ns以下,这意味着ESD是一种高频现象。ESD 电流路径与大小不但由EUT内部实际连接关系(这部分连接主要在电路原理图中体现)决定,而且还会受这种分布参数的影响。

一、静电放电可能产生的损坏和故障

1、穿透元器件内部薄的绝缘层,损毁MOSFET和CMOS的元器件栅极;

2、CMOS器件中的触发器锁死;

3、短路反偏的PN结;

4、短路正向偏置的PN结;

5、熔化有源器件内部的焊接线或铝线。

二、防护建议

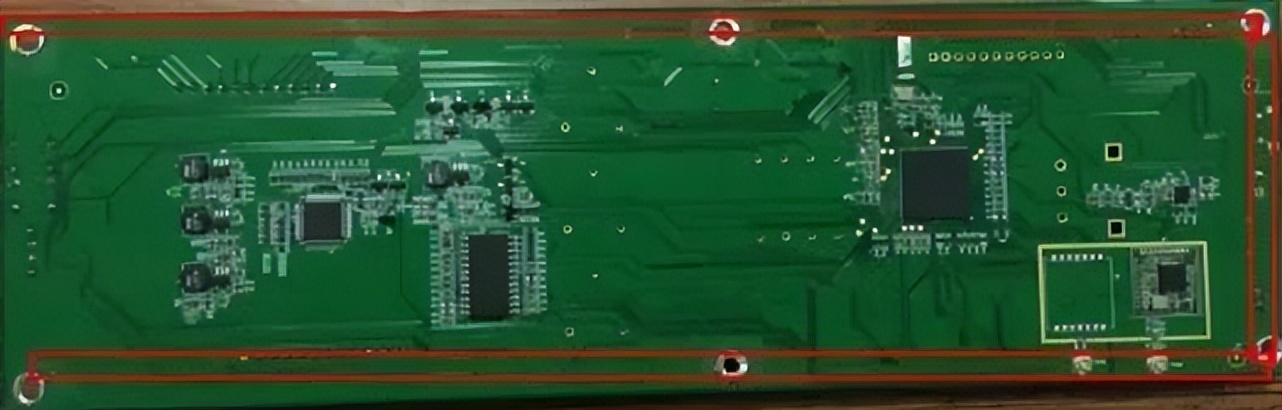

1、PCB周围的做一圈环地作为电源地(如下图所示),其它走线在内侧。

2、数字地和电源地进行隔离处理(加10nF电容)。

3、地尽量完整,如果条件允许的话,主芯片的地尽量不要分割,接地导体的电连续性设计对提高系统的抗ESD能力极为重要。

4、对于PCB上的金属体,一定要直接或间接地接到地平面上,不要悬空。另外,对于较敏感的电路或芯片,在布局时尽量远离ESD放电点。

5、针对比较敏感的电路或芯片,在信号线上加瞬态抑制保护器件进行保护,可以先预留保护器件的位置。

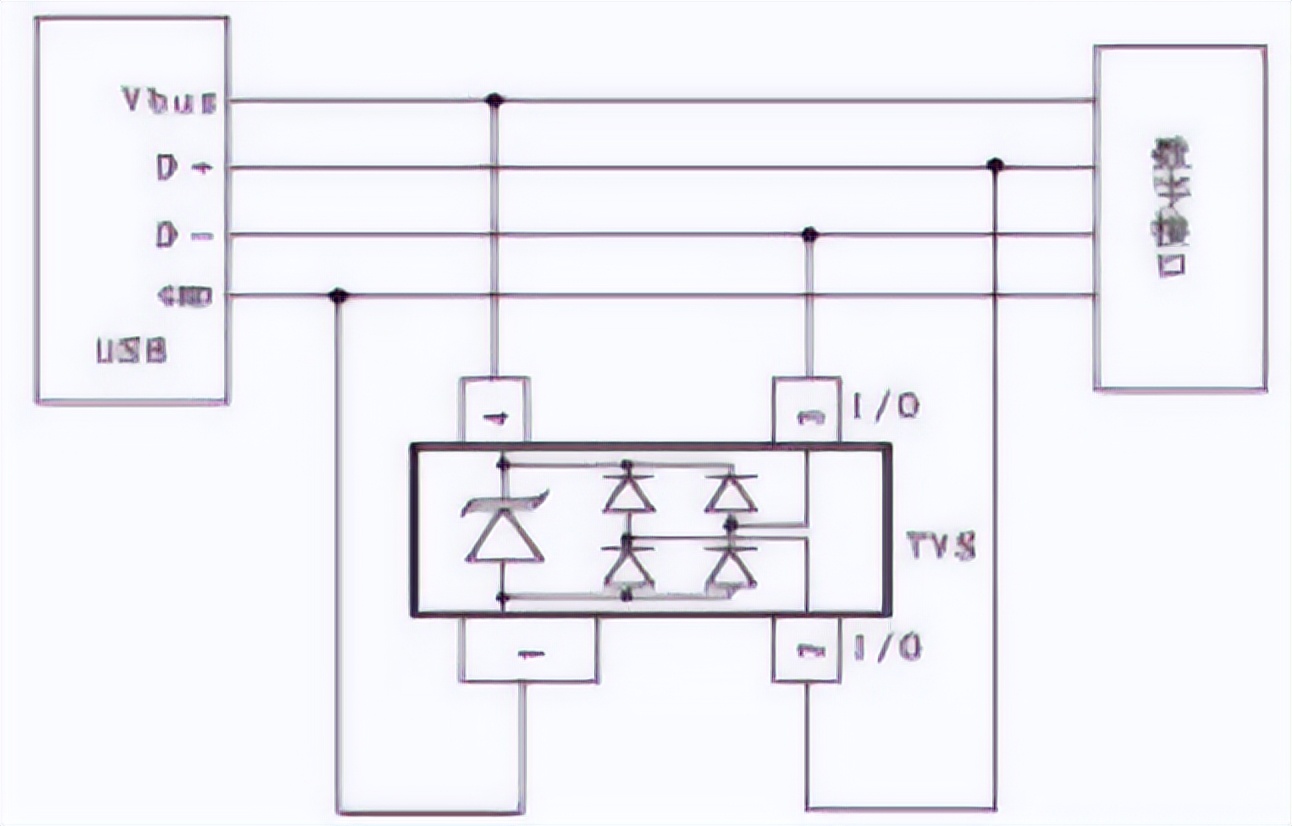

(1)USB口(两根信号线和一根电源线一根地线)

防护方案:

封装SOT-143,电压5V;

(2)DC 5V电源口正对地加双向保护器件(电压6V,封装SOD-214AA,功率720W);

(3)复位芯片:复位信号对地加超低容值ESD(电压5V,容值小于1pF,封装0402),上拉3.3V对地加低容值ESD(电压5V,容值10pF,封装0402);

(4)Flash芯片:1、2、3、5、6、7脚对地加超低容值ESD(电压5V,容值小于1pF,封装0402),8脚(电源脚)对地加低容值ESD(电压5V,容值10pF,封装0402);

(5)触摸IC:9、10、17、18脚对地加超低容值ESD(电压5V,容值小于1pF,封装0402);

(6)旋钮:信号口对地加低容值ESD(电压5V,容值10pF,封装0402);

(7)显示部分:信号口对地留ESD位置(电压5V,容值10pF,封装0402);

(8)温度采集IC:信号口对地加超低容值ESD(电压5V,容值小于1pF,封装0402)。

综上所述,相信通过本文的描述,各位对ESD静电的原理与整改建议都有一定了解了吧,有疑问和有不懂的想了解可以随时咨询深圳比创达这边。今天就先说到这,下次给各位讲解些别的内容,咱们下回见啦!也可以关注我司wx公众平台:深圳比创达EMC!

以上就是深圳市比创达电子科技有限公司小编给您们介绍的ESD静电的原理与整改建议的内容,希望大家看后有所帮助!

深圳市比创达电子科技有限公司成立于2012年,总部位于深圳市龙岗区,成立至今一直专注于EMC电磁兼容领域,致力于为客户提供最高效最专业的EMC一站式解决方案,业务范围覆盖EMC元件的研发、生产、销售及EMC设计和整改。

审核编辑 黄宇

-

ESD

+关注

关注

50文章

2437浏览量

180604 -

静电

+关注

关注

2文章

564浏览量

38420

发布评论请先 登录

EMC整改常遇到的问题和一些整改建议

微小医疗产品ESD静电整改问题

EMC整改常遇到的问题和一些整改建议

ESD整改方案—完整地对ESD静电管的作用

ESD静电整改之柱式蓝牙音箱死机案例

静电抗扰度(ESD)整改案例—蓝牙音箱整改

分析EMC整改常遇到的问题和整改建议

关于整改ESD静电保护的设计及建议

ESD静电的原理与整改建议?

ESD静电的原理与整改建议?

评论