共读好书

你即使从来没有学过物理,从来没学过数学也能看懂,但是有点太简单了,适合入门,如果你想了解更多的CMOS内容,就要看这一期的内容了,因为只有了解完工艺流程(也就是二极管的制作流程)之后,才可以继续了解后面的内容。那我们这一期就了解一下这个CMOS在foundry公司是怎么生产的(以非先进制程作为例子,先进制程的CMOS无论在结构上还是制作原理上都不一样)。

首先要知道foundry从供应商(硅片供应商)那里拿到的晶圆(也叫wafer,我们后面简称wafer)是一片一片的,半径为200mm(8寸厂)或者是300mm(12寸厂)的晶圆。如下图,其实就是类似于一个大饼,我们把它称作衬底。

但是呢,我们这么看不太方便,我们从下往上看,看截面图,也就是变成了下图这个样子。

下面我们就看看怎么出现我们上一期提到的CMOS模型,由于实际的process需要几千个步骤,我在这里就拿最简单的8寸晶圆的主要步骤来聊。

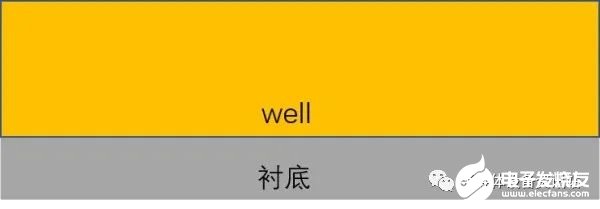

制作Well和反型层:

也就是通常说的阱,well是通过离子植入(Ion Implantation,后面简称imp)的方式进入到衬底上的,如果要制作NMOS,需要植入P型well,如果制作PMOS,需要植入N型well,为了方便大家了解,我们拿NMOS来做例子。离子植入的机器通过将需要植入的P型元素打入到衬底中的特定深度,然后再在炉管中高温加热,让这些离子活化并且向周围扩散。这样就完成了well的制作。制作完成后是这个样子的。

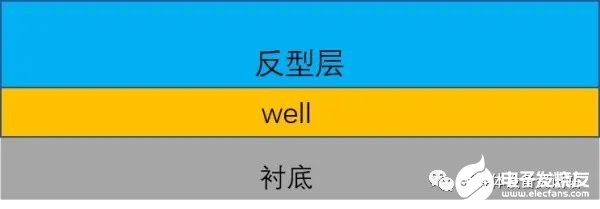

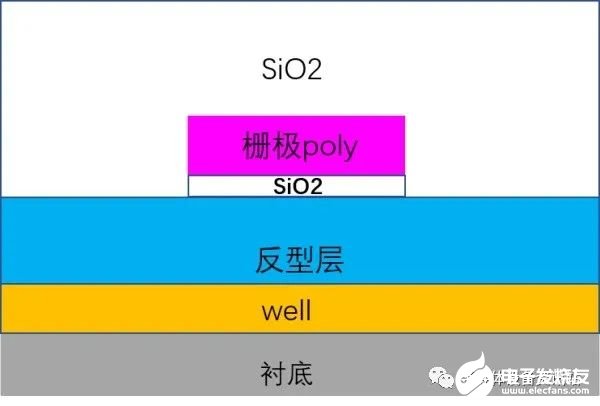

在制作well之后,后面还有其他离子植入的步骤,目的就是控制沟道电流和阀值电压的大小,大家可以统一叫做反型层。如果是要做NMOS,反型层植入的是P型离子,如果是要做PMOS,反型层植入的是N型离子。植入之后是下面这个模型。

这里面有很多内容的,比如离子植入时的能量,角度,离子的浓度等等,那些不在这一期当中,而且我相信你了解那一些的话,肯定是圈内人,你肯定有方法了解到。

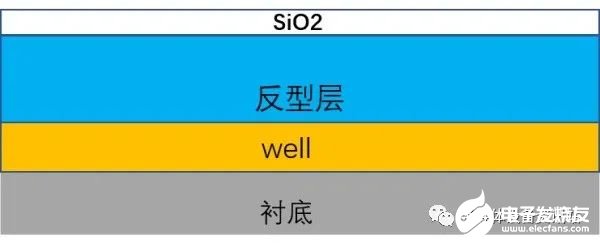

制作SiO2:

后面就会制作二氧化硅(SiO2,后面简称Oxide),在CMOS的制作流程中,制作oxide的方法有很多。在这里由的SiO2是用在栅极下面的,它的厚度直接影响了阀值电压的大小和沟道电流的大小。所以大多数foundry在这一步都是选择质量最高,厚度控制最精确,均匀性最好的炉管氧化方法。其实很简单,就是在通氧气的炉管中,通过高温,让氧气和硅发生化学反应,生成SiO2。这样就在Si的表面生成了薄薄的一层SiO2,如下面的图形。

当然这里面也有很多具体的信息,比如需要具体多少度啊,需要多少浓度的氧气啊,需要高温多长时间啊等等,这些都不是我们现在考虑的,那些太具体了。

栅端Poly的形成:

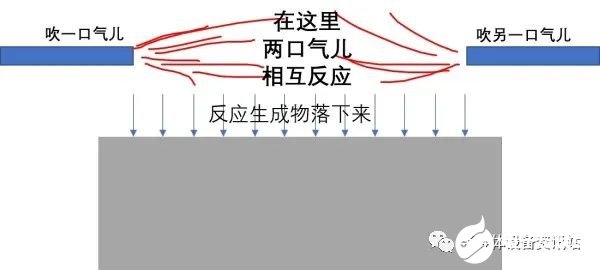

但是到这里还没结束,SiO2只是相当于螺纹,真正的栅极(Poly)还没有开始做呢。所以我们下一步就是在SiO2上面铺一层多晶硅(多晶硅也是单一的硅元素组成,但是晶格排列方式不同。你千万不要问我为什么衬底用单晶硅,栅极用多晶硅,这个有一本书叫半导体物理,您可以了解下,尴尬~)。Poly也是CMOS非常关键的一个环节,但是poly的成分是Si,不能像生长SiO2那样通过直接和Si衬底直接反应生成。这就需要传说中的CVD(化学气相沉淀,Chemical Vapor Deposition),就是在真空中发生化学反应,将生成的物体沉淀到wafer上,在这个例子中,生成的物质就是多晶硅,然后沉淀到wafer上(这里要多说一句,poly是用CVD的方法在炉管中生成的,所以poly的生成不是用的纯正CVD的机台)。

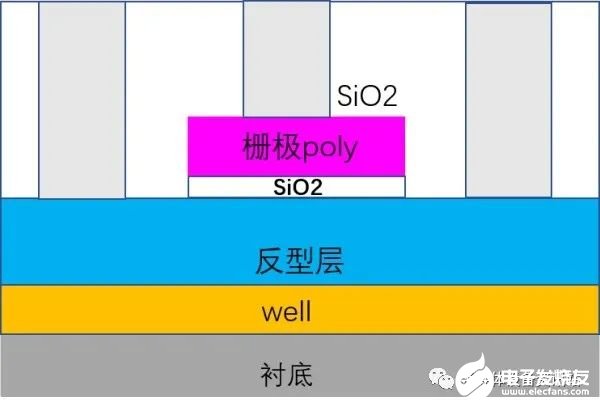

但是这种方法形成的多晶硅会在整片wafer都沉淀下来,沉淀之后是这个样子。

Poly和SiO2的曝光:

到了上面这一步,其实已经形成我们想要的垂直结构了,最上面是poly,下面是SiO2,再到下面是衬底。但是现在整片wafer都是这样,其实我们只需要一个特定位置是“水龙头”结构。于是就有了整个工艺流程中最最关键的一步—曝光。

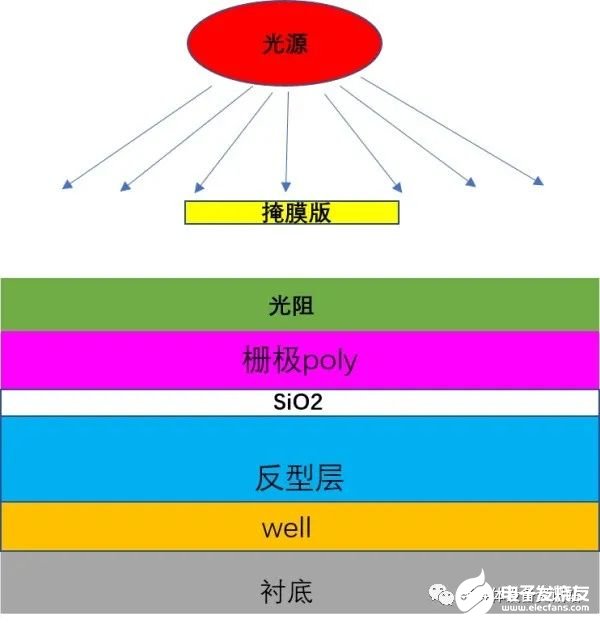

我们先在wafer表面铺一层光刻胶,也叫光阻(很难解释光刻胶的概念是什么,我相信你看着看着就懂了)就变成了这个样子。

然后再用定义好的掩膜版(掩膜版上已经定义好了电路图形)放在上面,最后用特定波长的光线照射,被照射的地方光阻会变活化,由于被掩膜版挡住的地方没有被光源照到,所以这块光阻没有被活化。

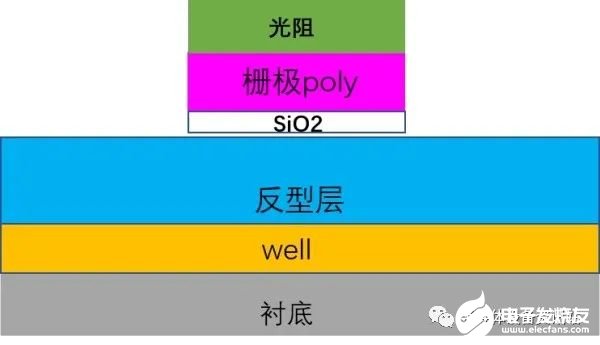

由于被活化的光刻胶特别容易被特定化学液体洗掉,而没有被活化的光刻胶不能被洗掉,所以通过照射后,再用特定的液体洗掉已经活化的

胶,最后就变成了这个样子,在需要保留Poly和SiO2的地方留下光阻,在不需要保留的地方除去光阻。

Poly和SiO2的刻蚀:

这之后就是把那些多余的Poly和SiO2刻蚀掉,也就是除去掉,这个时候使用的是定向刻蚀。在刻蚀的分类中,有一种分法是定向刻蚀和非定向刻蚀,定向刻蚀就是指在某个特定方向进行刻蚀,而非定向刻蚀就是不定向的(一不小心又说多了,总之就是通过特定的酸碱,在某个特定的方向除去SiO2)。在这个例子中我们采取向下的定向刻蚀除去SiO2,变成了这个样子。

最后再除去光阻,这个时候除去光阻的方法就不是上面提到的通过光的照射活化,而是通过其他方式,因为我们不需要在这个时候定义特定的大小,而是将光阻全部除掉。最后变成如下图所示。

这样我们就完成了保留特定位置Poly个SiO2的目的。

源端和漏端的形成:

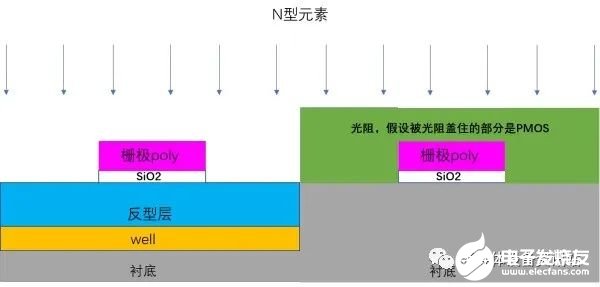

最后我们再考虑一下源端和漏端是怎么形成的。大家还记得在上一期中我们聊过,源端和漏端都是离子植入相同类型的元素。这个时候,我们可以在需要植入N型的源/漏区域上用光阻开口。由于我们是只拿NMOS做例子,所以上图中的所有部分都会开口,如下图

由于被光阻盖住的部份是不能被植入的(光阻挡着了嘛),所以只有在需要的NMOS上才会植入N型元素。由于poly下面的衬底被poly和SiO2挡住,所以也不会被植入,于是就变成了这个样子。

到这里,一个简单的MOS模型就制作出来了,理论上来讲,在source,drain,poly和衬底上加上电压,这个MOS是可以工作的,但是我们总不能直接在source和drain拿个探针直接加上电压吧。这个时候就需要MOS的布线,也就是在这个MOS上面,连导线,让很多MOS连在一起。我们就看看这个布线的过程。

制作VIA:

首先第一步就是在整个MOS上盖一层SiO2,如下图

当然这个SiO2是通过CVD的方式产生的,因为这样速度会很快,很节省时间。下面的话还是铺光阻,曝光的那一套,结束之后是长这个样子。

然后再用刻蚀的方法在SiO2上刻蚀出一个洞,如下图灰色的部分,这个洞的深度直接接触Si表面。

最后再除去光阻,得到下面的样子。

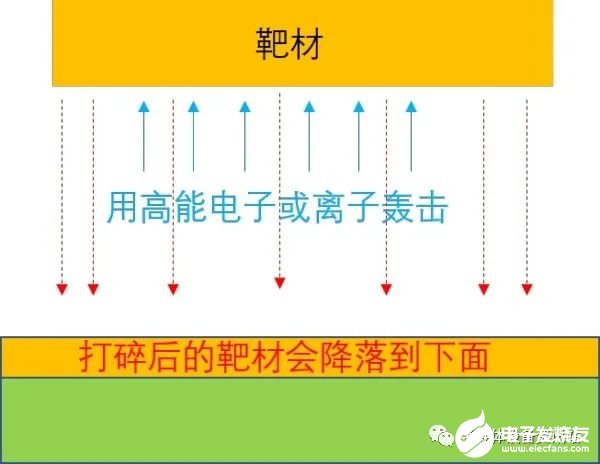

这个时候要做的就是在这个洞里填导体,至于这个导体是什么?各家都不一样,大部分都是钨(Tungsten)的合金,那怎么才能填好这个洞呢?用的是PVD(Physical Vapor Deposition,物理气相沉淀)的方式,原理类似于下图。

使用高能量的电子或离子轰击靶材,被打碎的靶材,会以原子的形式降落到下面,就这样形成了下面的镀膜。我们平时看新闻中提到的靶材就是指这里的靶材。

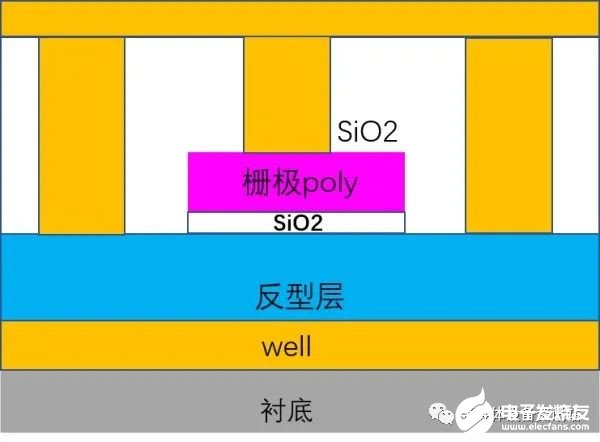

填完洞之后,就长这个样子。

当然我们在填的时候,不可能控制镀膜的厚度正好等于洞的深度,所以会多余一些,这样就用到了CMP(Chemical Mechanical polishing,化学机械研磨)技术,听起来很高大上,其实就是磨,将多余的部分都给磨掉。结果就是这个样子。

到了这里我们就完成了一层via的制作,当然,via制作主要是为了后面的金属层布线。

金属层制作:

在上面这个条件下,我们用PVD的方式再dep一层金属(metal)。这个金属主要是以铜为主的合金。

然后再经过曝光,刻蚀,得到我们想要的样子。然后不断的往上叠加,直到满足我们的需求。

我们在画layout时,会告诉你使用的工艺最多有多少层metal,多少层via,就是指它可以叠加多少层。

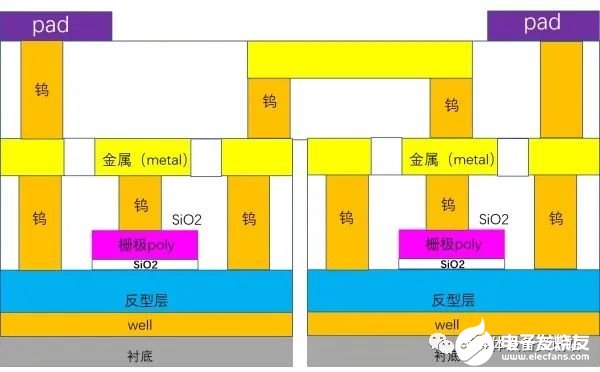

最终就得到这样的结构。最上面的pad就是这颗芯片的引脚,封装之后就成了我们能看到的管脚(当然我这是胡乱画的,没有什么实际意义,只是为了举例子)。

这就是一颗芯片制作的大概流程。这一期我们了解了半导体foundry中最重要的曝光,刻蚀,离子植入,炉管,CVD,PVD,CMP等等

审核编辑 黄宇

-

CMOS

+关注

关注

58文章

5680浏览量

235120 -

半导体

+关注

关注

334文章

26995浏览量

216110 -

光刻

+关注

关注

8文章

318浏览量

30112

发布评论请先 登录

相关推荐

简述半导体超纯水设备工艺流程及标准参考分析

SMT贴装基本工艺流程

倒装晶片的组装工艺流程

功率半导体分立器件工艺流程

半导体图案化工艺流程之刻蚀(一)

这可能最简单的半导体工艺流程

这可能最简单的半导体工艺流程

评论