锁存器的工作原理

锁存器(latch)是一种用于存储和记忆数字信号的电路。它被广泛用于计算机和数字电子电路中,用于实现内存存储、寄存器和其他计算单元。

锁存器的工作原理是通过反馈电路和放大开关的组合来实现的。在数字电路中,锁存器通常由逻辑门(例如与门或非门)组成。它可以采用不同的设计方式,包括SR锁存器、D锁存器和JK锁存器等。

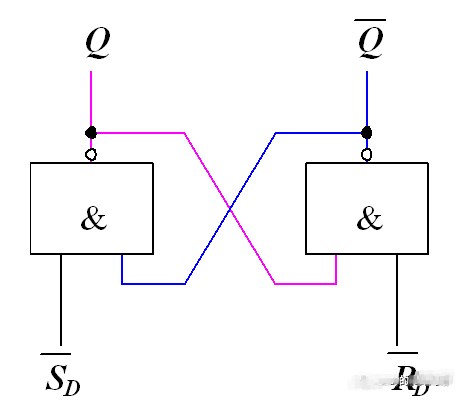

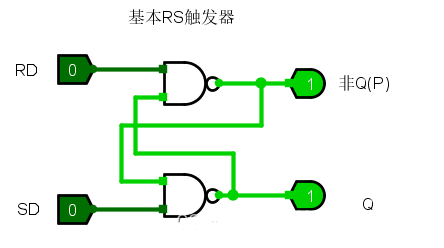

SR锁存器是最基本的锁存器类型之一。它由两个反馈连接的门电路组成,输入信号被存储在其中。SR锁存器有两个输入端(通常标记为S和R)和两个输出端(通常标记为Q和Q')。当S和R输入分别激活时,锁存器会将数据存储在输出端上。

具体来说,当S输入为高电平(1)时,Q输出为高电平,当R输入为高电平(1)时,Q输出为低电平(0)。当S和R都为低电平(0)时,锁存器保持之前的状态不变。当S和R同时为高电平(1)时,锁存器会处于未定义状态。

D锁存器是SR锁存器的一种变体,它只有一个输入端(通常标记为D)。D锁存器是通过使用一个与门和一个非门组合实现的。当D输入为高电平(1)时,锁存器将数据存储在输出端上。

JK锁存器是SR锁存器的另一种变体,它具有更灵活的功能。JK锁存器由两个输入端(通常标记为J和K)和两个输出端(通常标记为Q和Q')组成。当J和K输入同时为高电平(1)时,锁存器将翻转输出端的状态。当J输入为高电平(1)而K输入为低电平(0)时,锁存器将Q输出设置为高电平(1)。当J输入为低电平(0)而K输入为高电平(1)时,锁存器将Q输出设置为低电平(0)。当J和K都为低电平(0)时,锁存器保持之前的状态。

锁存器的输出取决于其当前状态和输入信号,并且可以通过适当的输入信号来改变其状态。这种能力使得锁存器成为实现存储和记忆功能的关键电路元件。在计算机和其他数字电子电路中,锁存器通常用于存储和操作数据,以实现不同的计算和控制任务。

锁存器的工作原理可以通过逻辑门的真值表和逻辑公式来推导。例如,对于一个SR锁存器来说,其真值表可以如下所示:

S | R | Q(t) | Q(t+1)

--+---+------+---------

0 | 0 | 0 | 0

0 | 0 | 1 | 1

1 | 0 | 0 | 0

0 | 1 | 0 | 1

1 | 1 | 0 | 0

其中,t表示当前时刻,t+1表示下一个时刻,Q(t)表示当前存储的数据,Q(t+1)表示下一个时刻存储的数据。从真值表中可以看出,锁存器的输出取决于当前时刻的输入和上一个时刻的输出。

锁存器的工作原理还可以通过逻辑门电路进行仿真和实现。例如,可以使用逻辑门(与门、非门等)来实现SR锁存器、D锁存器和JK锁存器。通过适当的选择和组合逻辑门,可以构建不同类型的锁存器电路。

总结来说,锁存器是一种用于存储和记忆数字信号的电路,它通过反馈电路和放大开关的组合来实现。不同类型的锁存器具有不同的功能和特性,例如SR锁存器、D锁存器和JK锁存器等。锁存器的工作原理可以通过逻辑门的真值表和逻辑公式进行推导和理解。锁存器在计算机和其他数字电子电路中被广泛应用,用于实现内存存储、寄存器和其他计算单元。

-

逻辑门

+关注

关注

1文章

142浏览量

24052 -

锁存器

+关注

关注

8文章

906浏览量

41502

发布评论请先 登录

相关推荐

RS锁存器的置位端口是哪个

Rs锁存器的工作原理、优缺点及应用

sr锁存器为啥q和q非不是反向

rs锁存器和sr锁存器有什么区别吗

RS锁存器的工作原理和应用实例

锁存器的工作原理

锁存器的工作原理

评论