随着电路仿真技术在原型设计行业的不断普及,仿真模型可能成为广大终端市场客户的一项关键需求。SPICE 和 IBIS 模型是非常受欢迎的两种仿真模型,有助于在电路板开发的原型设计阶段节省成本。本文将介绍SPICE与IBIS建模系统的区别,以及在制造电路板之前进行测试的重要意义。将讨论如何根据电路设计选择合适的模型。此外还将分析一些示例使用场景和常用的仿真工具,如 LTspice和HyperLynx。

简介

在这个技术飞速发展的数字时代背后,电子制造商源源不断地开发行业所需的基本元器件和工具,全力支持这一数字化发展进程。对于仿真而言,这意味着电路板开始开发后,设计人员可以在系统设计验证阶段通过仿真模型来确保其功能设计符合预期。在制造前测试设计时,SPICE和IBIS模型是常用的两种仿真模型。这两种模型本质上都是行为模型,但对于仿真中何时使用某种模型,根据具体情况有不同的建议。

使用仿真模型的好处

一般而言,仿真模型有助于系统设计人员在原型制作之前对电路设计进行仿真。使用IBIS和SPICE仿真模型时,目标不仅仅是仿真,还包括尽早发现与信号完整性和电路设计性能等相关的任何问题。这些问题通常是由电路板设计的特性(包括走线)引起的,或者也可能是元器件功能之类的简单问题。

IBIS模型不仅能表示元器件的箝位行为和驱动强度,还能表示数字输入/输出(I/O)缓冲器的阻抗,包括驱动器和/或接收器的输出和输入阻抗。这些并未在模型中直接说明,但都隐含在表示元器件行为的I-V数据中。在仿真过程中,确定缓冲器阻抗非常重要,因为这些阻抗是解决串扰和反射等信号完整性问题的关键。串扰是一种不需要的信号干扰,当一条走线上传播的信号与另一条走线上传播的信号耦合时就会发生串扰。另一方面,在制造电路板之前进行信号完整性仿真期间,也往往会遇到反射问题。众所周知,当输入或输出缓冲器的阻抗与走线的特性阻抗不匹配时,就会发生反射。理想情况下,进入器件并沿走线传播的信号应在没有任何干扰的情况下传输到走线的另一端。但实际上,这种情况通常不会发生。由于阻抗不匹配,信号完整性会受到影响。在发生反射期间,通常的情况是:沿传输线传播的信号一部分会传输到另一端,另一部分将会反射回来。解决此问题的一种办法是向缓冲器添加端接电阻。设计人员可以利用IBIS模型的阻抗特性来计算端接所需的串联或并联电阻,与引脚和传输线之间的阻抗相匹配,并解决信号反射问题。

SPICE模型通过预测电路行为,可以在构建原型之前发现、考虑并解决可能存在的问题,从而增强电路性能,这对于时间和资金的高效利用具有重要意义。成本和速度是SPICE模型仿真的两个主要优势。也就是说,在开发过程的早期避免电路错误,从而消除昂贵且耗时的原型返工,以免重新订购和重新焊接元器件。如今的仿真模型更加先进,可以提供准确的元器件性能近似值。设计人员可以轻松更换元器件,以评估采用不同物料清单(BOM)的电路设计。同时,设计人员不必花费很多时间制作电路组件原型,也不必在发现并纠正原型错误后重新焊接组件。

背景知识

什么是SPICE模型?

SPICE是Simulation Program with Integrated Circuit Emphasis(以集成电路为重点的仿真程序)的首字母缩写。它是一种通用电路仿真器,采用文本网表描述电路元件(晶体管、电阻和电容)及其连接,并使用节点分析将其转换为数学方程进行求解。相对而言,SPICE模型是一种基于文本的行为模型,SPICE仿真器使用这种模型通过数学运算预测器件在不同条件下的行为。

什么是IBIS模型?

IBIS是Input/Output Buffer Information Specification(输入/输出缓冲器信息规范)的首字母缩写。它是一种行为模型,描述器件的数字输入和输出缓冲器的模拟行为。它由表格数据组成,描述数字缓冲器内元器件的电流-电压(I-V)关系,以及输出或I/O缓冲器的电压随时间变化的(V-t)开关特性。它用于在制造之前对系统板进行信号完整性分析,并以纯ASCII文本格式的数据呈现。它不披露任何专有信息,因为IBIS模型就像一个黑盒模型,不包含可逆向工程的内部信息。

模型概述

模型看起来是什么样子?

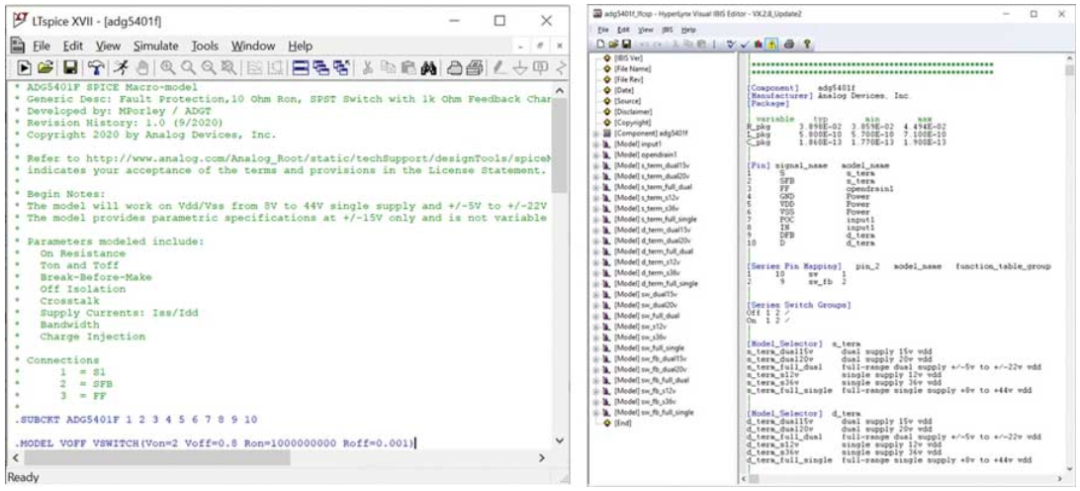

如图1所示,IBIS和SPICE模型都是基于文本的行为模型,可以使用记事本等简单工具查看其内容。不过,为了更方便地浏览模型,建议使用Cadence Model Integrity或Siemens的HyperLynx查看IBIS文件。另一方面,SPICE模型可以在各种SPICE仿真工具中打开并安装,例如LTspice、NI Multisim、OrCADPSpice或其他SPICE仿真器。

图1.左侧是使用LTspice打开的SPICE文件(.cir),右侧是使用Siemens的HyperLynx打开的IBIS文件(.ibs)

SPICE和IBIS模型都是不可执行文件,并且都是基于文本的描述文件。这两种模型大多数都由三个主要部分组成:

-

模型名称/标题:主要提及器件名称、引脚排列和/或引脚到缓冲器映射。对于SPICE,格式为:点子电路<空格>模型名称(.subckt ADGxx)<空格>引脚排列。对于IBIS,格式为:[Component] ADGxx。

-

模型结构:基于文本的模型表示。SPICE模型由不同的块组成,这些块展示器件的每个参数,包括引脚功能;各个块可能包括原始和原生元件,如电容、电阻、二极管、电压源和电流源等。另一方面,IBIS模型由I/V和V/T数据表组成,这些数据表是对每个数字I/O缓冲器建模的结果。

如何获取模型?

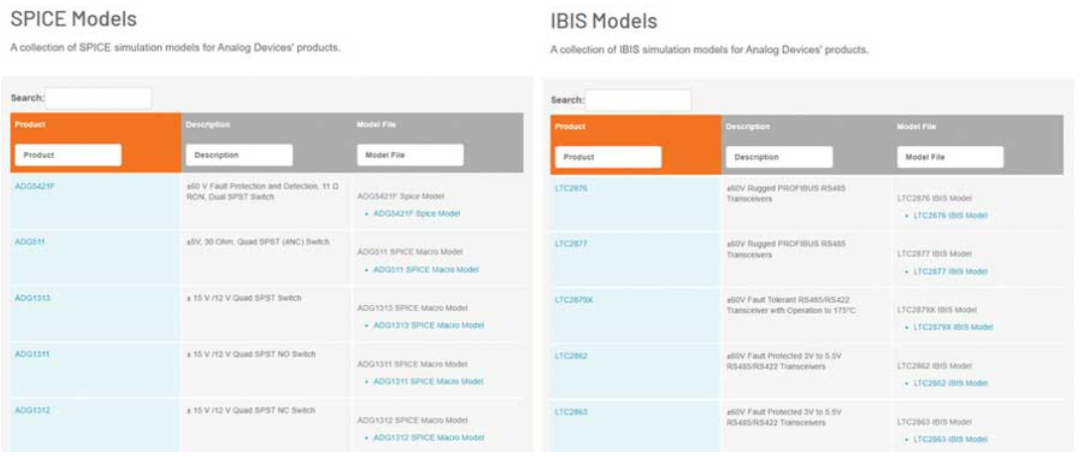

SPICE和IBIS模型大多位于各家半导体公司的网页上。如今,半导体制造商针对自己的产品开发仿真模型,同时保持模型的包容性、内容、准确性和模型支持。ADI公司网站提供了ADI产品的各种SPICE和IBIS模型,如图2所示。

图2.ADI网站中各种SPICE(左)和IBIS(右)模型

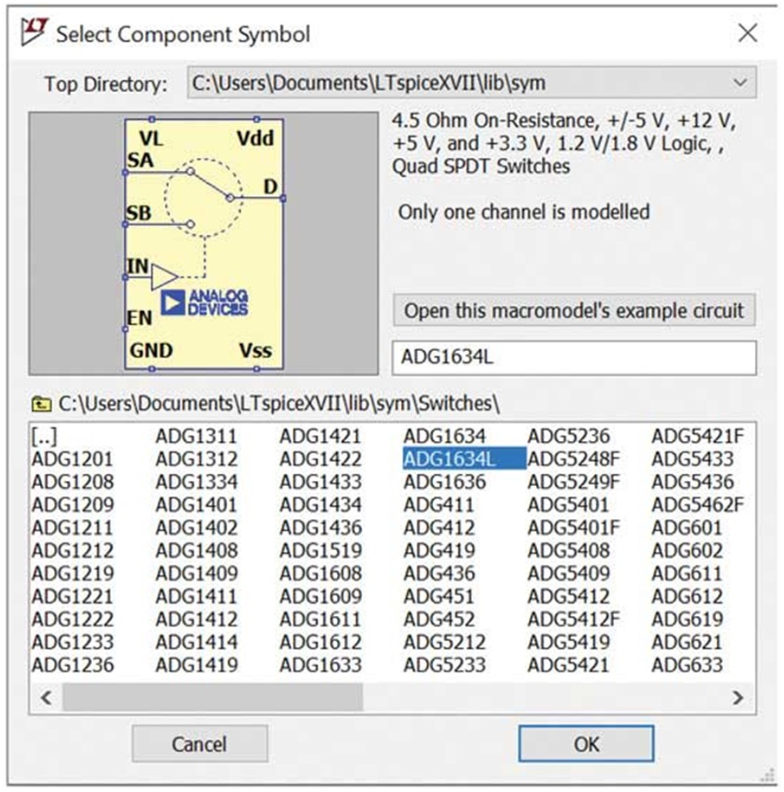

其他SPICE模型可以在制造商的SPICE仿真器库中找到。图3显示了LTspice的开关库,它涵盖了ADI公司的大部分开关产品。为了简化仿真方法,选择具有大量可用SPICE模型库的SPICE仿真器会很有帮助。

图3.LTspice中包含大量SPICE模型库示例

补充文件

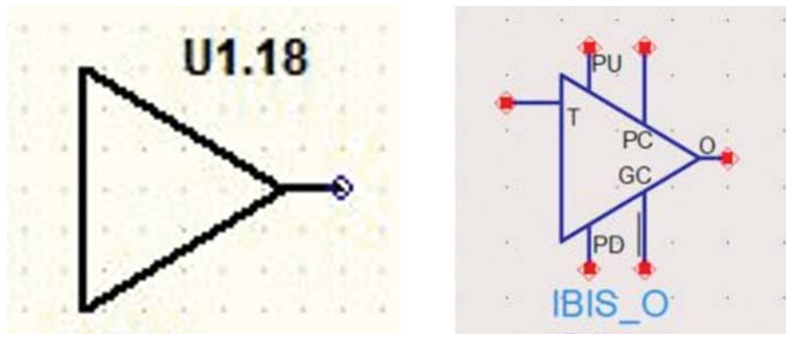

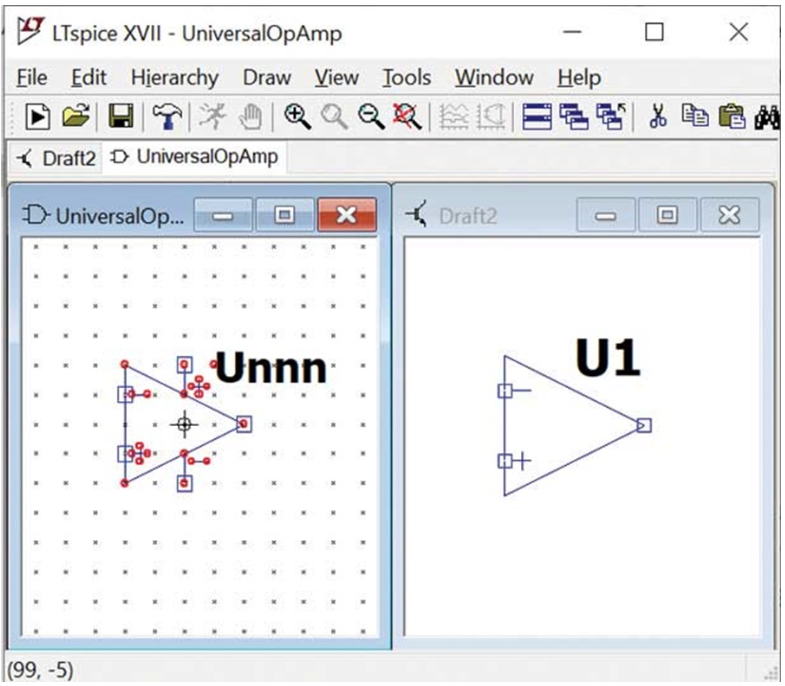

为了在仿真器中使用,SPICE和IBIS模型都需要随附一个符号文件。IBIS模型通常以基于文本的数据表示的形式出现,但为了使用电子设计自动化工具对其进行仿真,一般会将模型置于符号中,外部元器件可连接到该符号。与IBIS模型类似,SPICE模型也需要一个符号文件,该文件通常为点符号(.asy)格式,必须同时安装到SPICE仿真器库中。只需将模型和符号添加/安装到库中,设计人员就可以在电路仿真中使用模型。图4和图5显示了IBIS和SPICE模型中使用的符号文件示例。

图4.使用HyperLynx(左)和Advanced Design System(右)的输出缓冲器IBIS符号

图5.简单3引脚运算放大器的SPICE符号文件(右)模板,及其在LTspice电路仿真中使用的等效符号(左)

对于IBIS和SPICE,制造商均不提供符号文件,但大多数仿真器提供模板符号,设计人员可以根据引脚数量或器件类型使用这些符号。另外,SPICE符号文件还可以自动生成,此功能取决于SPICE仿真器。

模型比较

SPICE模型

一般而言,SPICE模型可复现元器件行为,包括引脚排列、引脚配置、功能和其他操作。这些模型没有标准架构,但其目标是创建一个准确复现元器件预期行为性能(包括其引脚功能)的架构。模型可能由电阻、电容、二极管和晶体管等无源元件组成,如果设计得当,这些元件就会产生目标元件行为。需要记住一点,由于SPICE模型可准确复现元器件的行为,因此可能会包含复杂电路,从而导致仿真周期变慢。SPICE模型可以是简单的单行文本,描述电阻之类的无源元件,也可以长达数百行,描述更复杂的电路和子电路。

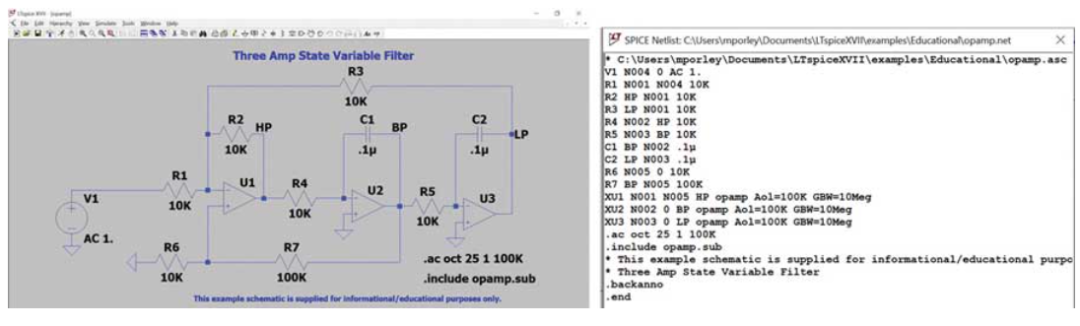

如上所述,SPICE模型可以使用基于文本的工具打开,但大多数最新的SPICE仿真器支持查看等效原理示意图,以便更轻松地进行电路分析。如图6所示,其中三放大器状态变量滤波器也可以转换为等效的描述电路元件及其连接的文本网表。

图6.三放大器状态变量滤波器的SPICE模型示例

在模型性能方面,根据经验法则,SPICE模型可提供与器件数据手册给出的规格和功能相近的行为性能。例如,开关SPICE模型应具有导通电阻和时序参数,而放大器很可能具有增益带宽和输入失调参数。相对而言,模型功能和规格必须接近数据手册中提供的典型值、最小值或最大值,或在这些值的范围以内。

IBIS模型

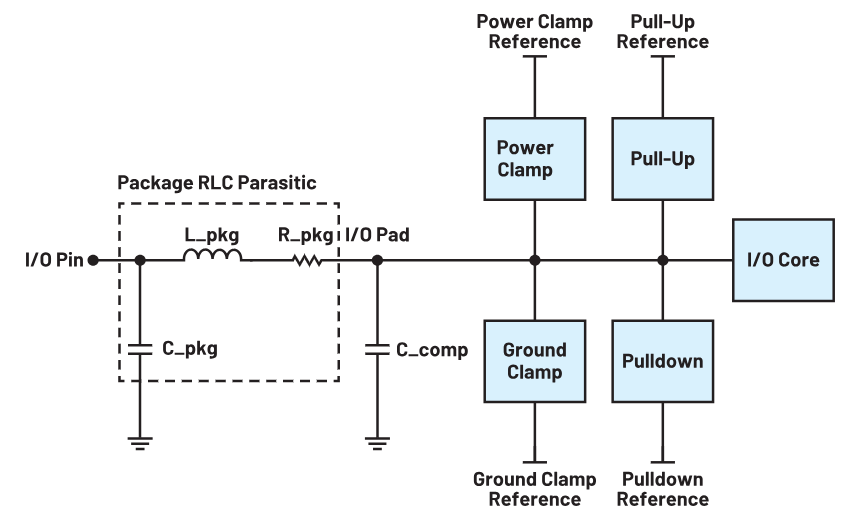

一般而言,IBIS模型以标准架构来表示数字I/O缓冲器。这通过IBIS关键词表示来实现,关键词用于描述数字缓冲器的每个组件,如图7所示。IBIS关键词以V-I查找数据表和V-t查找数据表的形式出现。

图7.典型I/O缓冲器的IBIS框图

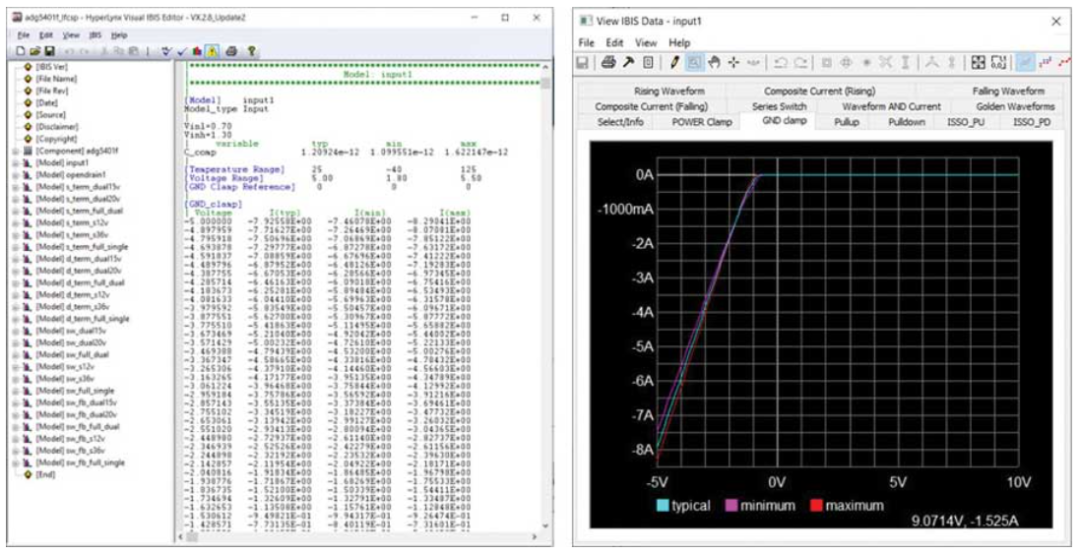

图8中的左图显示了IBIS模型中的V-I查找表示例,右图显示了使用Siemens HyperLynx绘制该V-I查找表得到的波形。它是在一组电压范围(通常从-VDD到两倍VDD)下进行的一系列电流测量,以表示特定IBIS元器件在三种情况(典型工艺角、慢工艺角和快工艺角)下的行为。这可通过改变器件的工艺角、工作电压和工作温度来完成。这些表以[Power_clamp]和[GND_clamp]关键词表示接收器的箝位保护元件,并以[Pullup]和[Pulldown]关键词表示I/O缓冲器的驱动强度。这4个V-I关键词在模型中单独表示,因为接收模式和驱动模式都是信号完整性仿真所必需的。

图8. ADG5401F的IBIS关键词的V-I数据(左);使用Siemens HyperLynx绘制的V-I曲线(右)

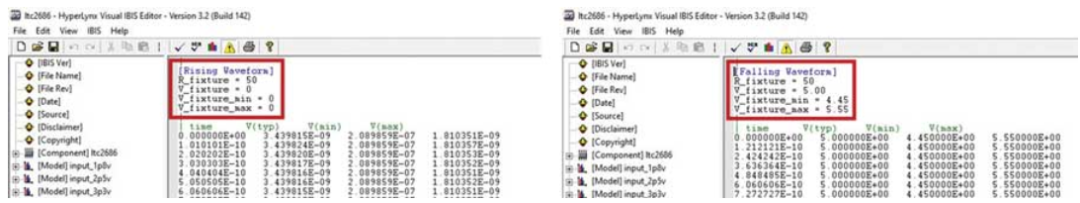

另一方面,V-t表以[Rising_Waveform]和[Falling_Waveform]的形式表示驱动器从一种状态转换到另一种状态时的开关特性(负载以VDD和地为参考时)。它还在IBIS关键词[Ramp]项下包含I/O缓冲器的摆率,该摆率是在转换边沿的20%到80%范围测量的。这些波形和斜坡数据描述了驱动器部件开启或关闭的速度与时间的关系。

虽然这些关键词在模型中是单独表示的,但在仿真期间使用时,电子设计自动化仿真工具会结合这些V-I和V-t数据,根据其工作区域构建缓冲器模型,并且会使用该模型执行印刷电路板的信号完整性仿真和时序分析。

此外,IBIS模型还包含器件的RLC引脚和/或封装寄生值,以及每个I/O缓冲器的缓冲器电容(C_Comp)。C_comp是从焊盘回到缓冲器的电容,不包括封装电容。

欲了解更多有关IBIS模型中的V-I和V-t数据表或关键词的信息,读者可以参阅之前发表的文章"IBIS建模——第1部分:为何IBIS建模对设计成功至关重要"。

仿真工具

现有各种各样的行业标准SPICE和IBIS仿真器,可为大多数高速设计系统以及模拟和混合信号电路提供设计仿真,适合专业人士和教培人员使用。SPICE仿真器通常根据电路连接/节点生成节点方程,然后尝试求解各个节点处的电流和电压值。另一方面,IBIS仿真器参照模型中提供的V-I和V-t查找数据表来预测信号的输出行为。业界常用的仿真器包括:

IBIS仿真器

-

Keysight的Advanced Design System是一款电子设计自动化工具,可用于各种设计流程,例如频域和时域电路仿真、原理图设计和布局、设计规则检查、电磁场仿真等。该工具常用于IBIS模型仿真。

SPICE仿真器

-

LTspice是一款高性能SPICE仿真器软件,包括原理图捕获图形界面。通过内置波形查看器可探测原理图以产生仿真结果。这款SPICE仿真器的图形用户界面(GUI)基于对原理图输入所需的键盘输入和鼠标动作的统计分析,与其他SPICE仿真相比交互性更强。LTspice包括一个庞大的SPICE模型库,其涵盖了大部分ADI产品和信号链产品,另外还有一个无源元件库。

-

NI Multisim具有交互式原理图环境,可即时可视化和分析电子电路行为。该仿真器具有虚拟示波器、数字万用表和其他基准测试设备,使电路仿真体验接近典型的工程师试验台评估环境。

-

OrCAD PSpice Designer集原理图输入、原生模拟、混合信号和分析引擎于一体,提供完整的电路仿真和验证解决方案。无论是制作简单电路原型、设计复杂系统,还是验证元器件良率和可靠性,OrCAD PSpice技术都能提供出色的高性能电路仿真,让您在进行布局和制造之前有效分析和完善电路、元器件及参数。

IBIS模型和SPICE模型用例

IBIS模型

IBIS模型通常以基于文本的数据表示的形式出现,但为了使用EDA工具对其进行仿真,一般会将模型置于符号中,外部元器件可连接到该符号。仿真器使用模型中包含的数据来分析和预测给定情况下的缓冲器行为。

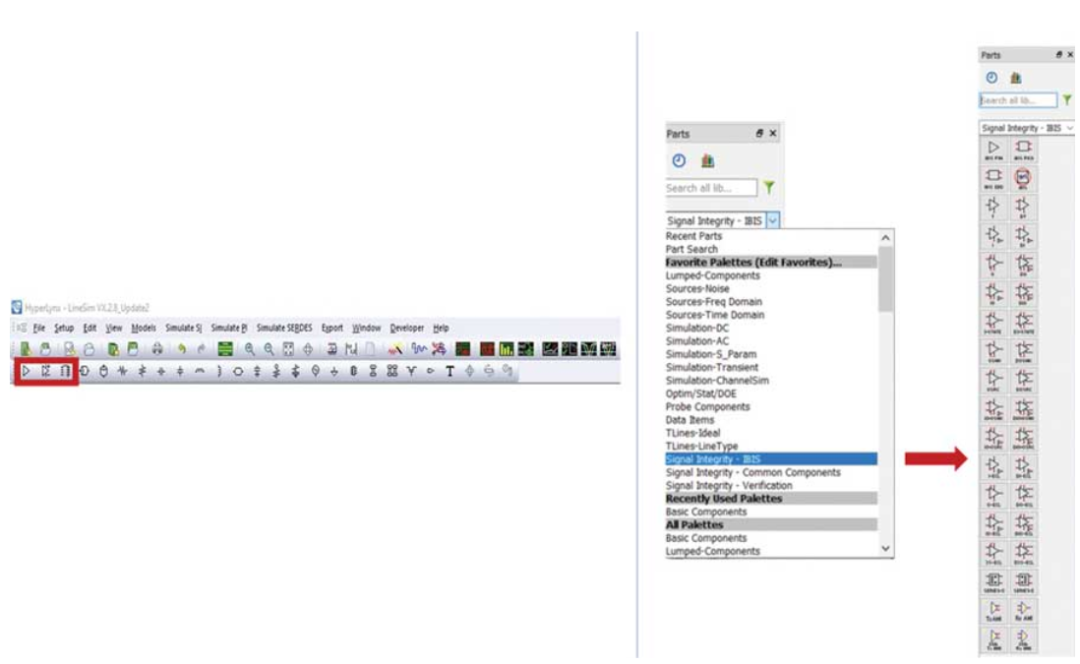

Siemens的HyperLynx和Keysight的Advanced Design System都具有IBIS符号,设计人员可以在仿真中使用这些符号。图9展示了这些符号在这些工具中的显示方式。

图9.HyperLynx工具栏显示了可用于IBIS模型仿真的单端缓冲器、差分缓冲器和IC器件的符号(左);Advanced Design System工具栏显示了可用于IBIS模型仿真的不同类型缓冲器的符号(右)

-

在HyperLynx中进行单端输入或输出缓冲器仿真时,可以使用左图第一个突出显示的缓冲器,然后加载IBIS模型并选择要仿真的具体缓冲器。如果选择输出缓冲器模型,工具会自动显示输出缓冲器。否则,如果要仿真输入缓冲器,工具会自动将符号转换为输入缓冲器符号。

-

在Advanced Design System中,"Signal Integrity - IBIS"(信号完整性 - IBIS)元件板会显示各种类型的缓冲器模型。如果需要开漏输出,必须选择标记为OSNK的符号;如果要仿真端接电阻,仿真中必须使用标记为T的符号。请注意,如果选择的符号不对,可能会导致错误。例如,如果需要输入缓冲器,却在原理图中放置了输出缓冲器符号,将无法看到IBIS中建模的输入缓冲器可用引脚,因为仿真器只允许符号中加载输出缓冲器引脚。

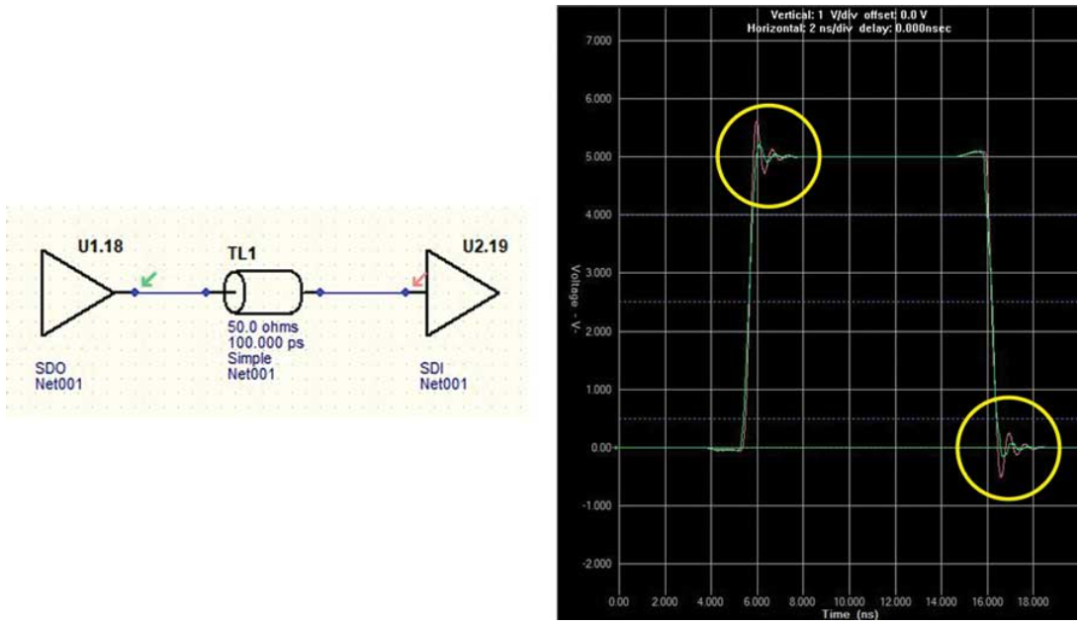

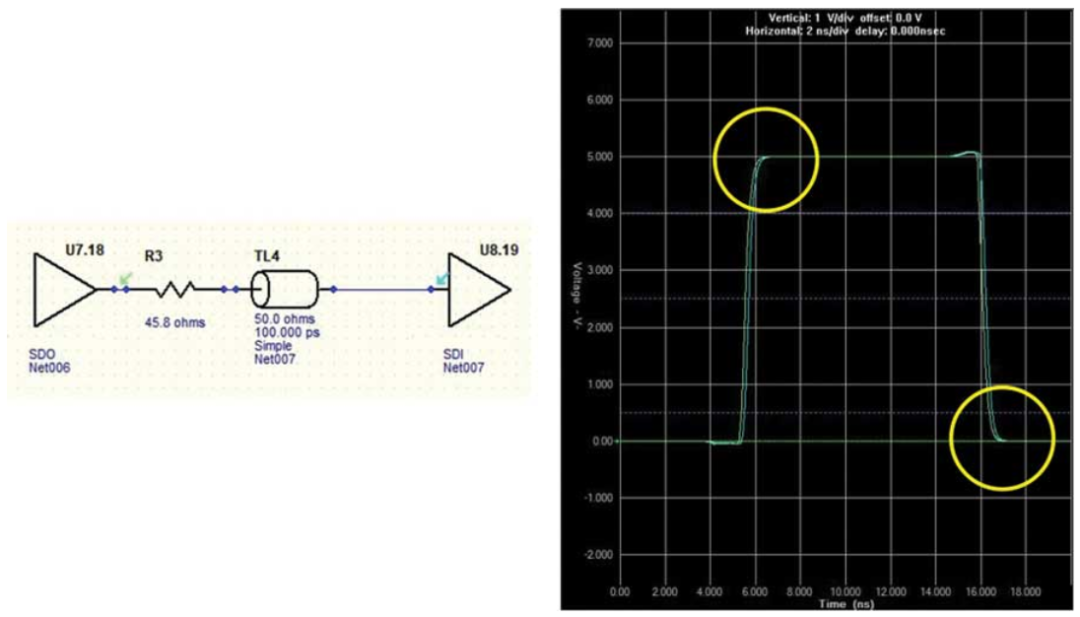

IBIS模型仿真的用途之一是解决不需要的信号行为,这些行为通常是由缓冲器和充当传输线的PCB走线之间的阻抗不匹配引起的。例如,图10中使用HyperLynx的原理图仿真。

图10.未采用端接电阻的原理图(左)及其相应的结果(右)

图10所示是使用50 Ω走线进行的未端接输出缓冲器仿真,它会产生不需要的过冲和欠冲信号。为了解决此问题,可以添加一个串联端接电阻,与缓冲器和走线之间的阻抗相匹配。但在此之前,必须先确定输出缓冲器的阻抗。

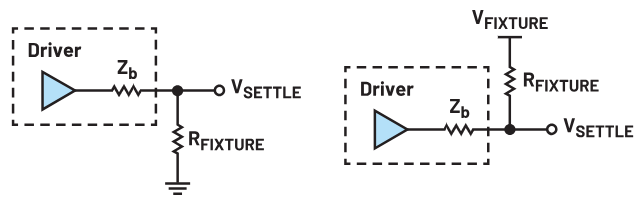

IBIS模型中的V-t表、相对于地的[Rising_Waveform]和相对于VDD的[Falling_Waveform]可用于计算缓冲器的输出阻抗,因为该参数是模型中表示的数据本身固有的。使用分压器定理可以推导出缓冲器阻抗值,然后使用此值来计算需要添加到模型中并与缓冲器和走线之间的阻抗相匹配的适当端接电阻。这将有助于解决阻抗失配问题,并消除信号中不需要的过冲和欠冲。

图11显示了分压器的原理图,其中Zb是缓冲器阻抗,R_fixture和V_fixture可在模型中找到,而VSETTLE是V-t波形稳定后的电压。

图11.分压器的原理图

图12.IBIS模型显示了提取V-T查找表所使用的电路:上升波形(左)和下降波形(右)

确定端接电阻值后,即可将其添加到原理图中。

图13显示了端接后的原理图及其相应结果,初始过冲和下冲问题已得到解决。

图13.采用端接电阻后的原理图(左)及其相应的结果(右)

上述方法只是用于计算缓冲器阻抗并解决不匹配阻抗问题的策略之一。还有其他方法,例如使用IBIS模型的下拉V-I表,并执行负载线路分析来确定工作点。由此可以推导出输出阻抗以及串联端接电阻的值。

SPICE模型

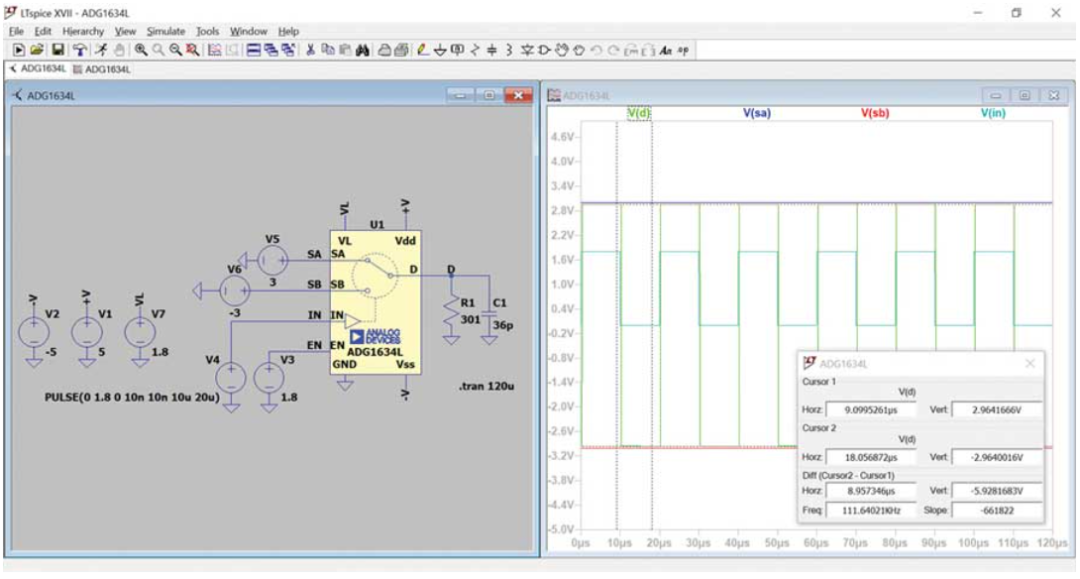

图14显示了瞬态分析中使用 ADG1634L 模型的SPICE仿真示例。设计人员可以评估ADG1634L的性能(在本例中)并对其进行仿真,以检查器件的时序和其他功能;绘图结果将在时域中显示。瞬态分析可预测器件在指定时间范围内的行为。SPICE模型还可以在不同类型的分析中进行仿真,例如直流分析和交流分析。直流分析根据一系列直流输入值计算电路的电压和电流。交流分析确定电路中节点的相位和幅度,这对于检查频域中的电路行为可能很有用。

图14.使用ADG1634L模型的SPICE仿真示例

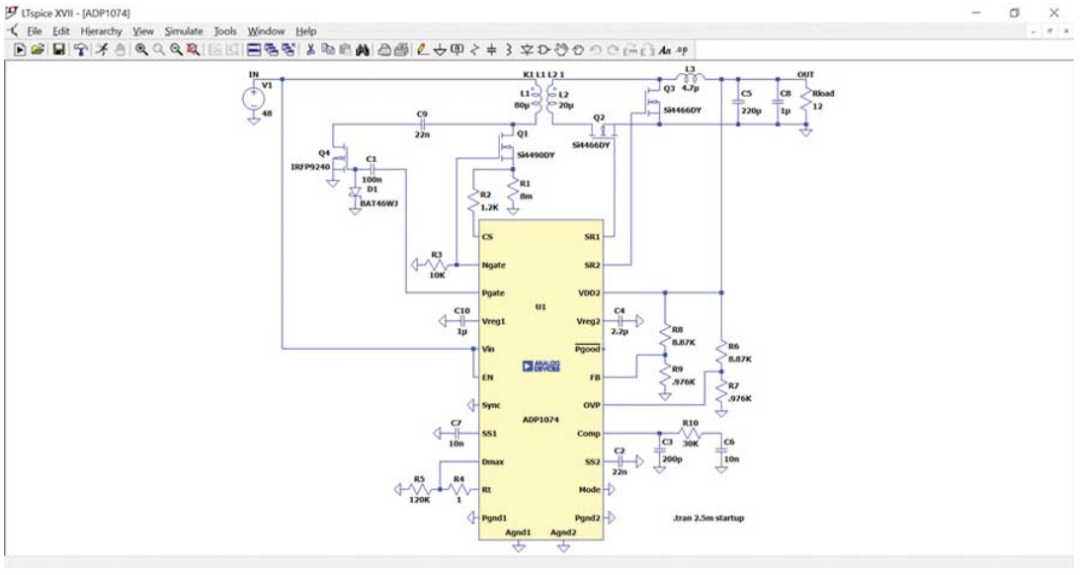

更进一步,可以对更复杂的电路设计进行SPICE仿真,从而确定设计的性能。参见图15中的示例。

图15.LTspice中的正激有源钳位电路SPICE仿真示例

哪种模型更适合您的仿真?

对于以下情形,IBIS模型可能非常适合电路仿真:

-

如果设计人员正在评估数字I/O缓冲器的行为特性,例如缓冲器阻抗、驱动强度、上升时间或下降时间

-

当您尝试评估数字器件(如FPGA)时

-

关注信号完整性或器件数字I/O引脚连接到PCB走线时可能出现传输线错误的设计

另一方面,如果需要通过电路仿真更全面地了解器件性能,包括模拟、数字和电源引脚功能以及其连接到电路中的多个器件时的行为响应,则建议使用SPICE模型。应使用SPICE模型而不是IBIS模型的其他情形包括:

-

如需要评估器件在电路中使用时的功能及其行为性能时

-

需要评估器件在不同分析和域(时域或频域)中的行为响应时

-

需要深入细致的节点分析并求解电路中的电流和电压节点的复杂设计

结语

SPICE和IBIS模型在业界越来越受欢迎,因为这些模型可以帮助设计工程师在原型制作之前和期间验证目标电路性能,从而节省设计成本和时间。这两种模型本质上都是行为模型。一般而言,SPICE模型可复现元器件行为,包括引脚排列、引脚配置、功能和其他操作。IBIS模型使用电压-电流和电压-时间表格数据形式的参数来模拟器件的数字I/O行为。为了在仿真器中使用这些模型,SPICE和IBIS模型都需要随附一个符号文件。SPICE模型仿真可预测器件的性能,包括其预期的引脚功能和配置,而IBIS模型仿真通常用于预测数字I/O引脚上出现的信号完整性问题,例如PCB仿真期间的阻抗失配、串扰、反射、下冲或过冲。选择使用哪种模型取决于设计人员使用模型的目的。对于关注信号完整性、驱动强度或器件数字I/O引脚连接到PCB走线时可能出现传输线错误的设计,强烈建议使用IBIS模型。另一方面,如果通过电路仿真了解器件性能,包括在电路中使用时其模拟、数字和电源引脚的功能,那么建议使用SPICE模型。

-

亚德诺

+关注

关注

6文章

4680浏览量

15951

原文标题:巧用SPICE与IBIS,为您的电路仿真选择更合适的模型

文章出处:【微信号:analog_devices,微信公众号:analog_devices】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

巧用SPICE与IBIS,为您的电路仿真选择更合适的模型

巧用SPICE与IBIS,为您的电路仿真选择更合适的模型

评论