当SoC上有超过80%的芯片面积被各种形式的存储器占用之时,存储器的DFT测试已经变得非常重要。

(一)存储器故障模型类型:

1.固定故障(SAF),即Stuck at Fault

存储单元stuck at 1或0。

2.转换故障(TF),即Transition fault

比如可以1->0,但是无法完成0->1的准换。

3.耦合故障(CF),即Couple Fault

由于邻接单元,许多单元共享字线和位线,写入一个单元可能导致另一个单元出现相同值。反向耦合(CFin, Inversion Couple Fault)是指当写入一个值到一个存储单元时,该值将反转另一个存储单元值。

比如,要测试CF,需在所有单元中写0,然后在存储单元A写1。读取所有单元值,检查除了单元A为1外,是否还有其他单元被耦合拉为1了。另外,对相反值也要采取此流程。

4.桥接故障(BF),即Bridge Fault

两个或两个以上位线短接在一起就造成了桥接故障(BF)。

(二)存储器测试算法

测试存储器测试算法的性能指标通常有两个:

测试时间

故障覆盖率

常用的确定性测试算法有:Checkerboard算法、March类算法、MSCAN(Memory Scan)算法、跳步 (GALPAT) 和走步 (Walking 1/0)算法,我们重点介绍Checkerboard算法、March类算法。

MSCAN算法

MSCAN 算法是一种最基本、最简单的测试算法。首先对所有待测单元写入全0,然后读取所有存储单元并判断是否有故障,接着写入全1,再读取所有存储单元并判断是否有故障,可以检测所有SAF故障,缺点是仅支持部分耦合故障的测试,故障覆盖率有限。

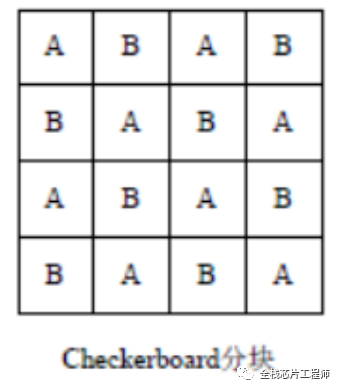

Checkerboard棋盘算法

Checkerboard 算法也叫棋盘算法,基本过程是对每个存储单元进行赋值,保证每一个存储单元的值都与相邻单元的值不同,这样就将整个存储阵列分为了两块:存储值是0的为A 块,存储值是1的为B 块:

Checkerboard棋盘算法分块后,按如下过程测试:

(1) 对A和B块分别写入0和1;

(2) 读所有存储单元;

(3) 对A和B块分别写入1和0;

(4) 读所有存储单元。

该算法的操作数为4N,N为存储单元个数,时间复杂度为O(N),可以检测固定型故障和部分桥连故障,在BIST 算法中应用广泛。

March 测试算法

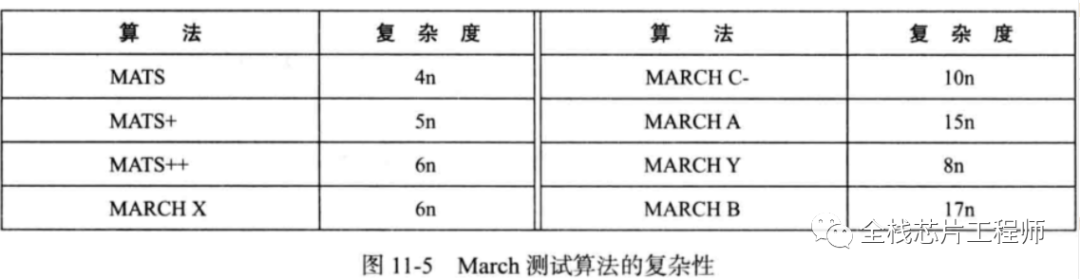

March算法是一系列的算法,具有较高的故障覆盖率、测试时间较短,已经广泛应用于大容量SRAM 和DRAM 的测试,目前的March 算法主要有MATS,MATS+,March X、March C、March C-、March C+、March LR 等类型。可以检测各种内存故障(Stuck-At、Transition、Address faults、Idempotent coupling faults)。

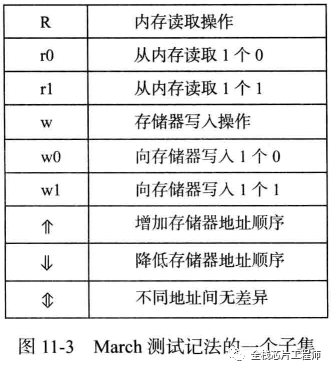

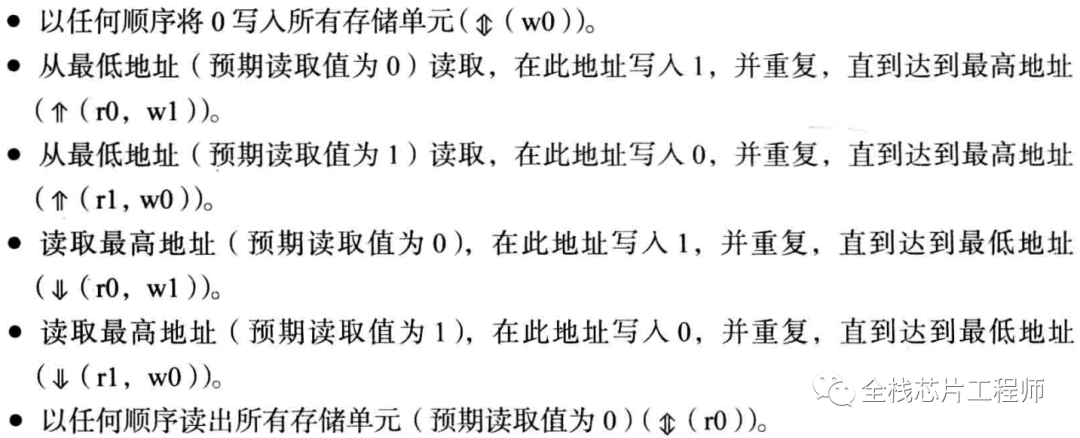

March-C 算法以任何顺序将0写入所有存储单元,然后从位置 0开始以地址升序排序的方法读取并检查数据是否是0,并将已读取的位置写入1,遍历后,所有的存储器位都为1。然后我们又从位置0开始以递增顺序读取 1,并将每次读取的位置写为0。然后重复类似的测试。详细步骤如下:

March-C 的测试步骤:

按照上图的解释,March算法执行步骤可以更简单的描述如下:

地址递增:

初始化写0

读0,写1,地址顺序递增

读1,写0,地址顺序递增

地址递减:

读0,写1,地址顺序降序

读1,写0,地址顺序降序

按降序读0

March-C读写一共进行10次,因此算法复杂度为10N。

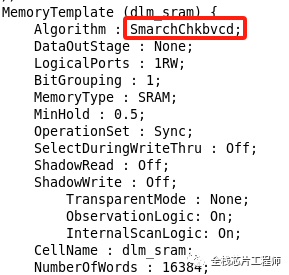

当前,大多数行业标准使用March和棋盘格算法的组合,通常称为SMarchCKBD算法。该算法使MBIST控制器能够进行快速行或列访问来检测内存故障。

我们可以看到景芯SoC训练营也是采用的SMarchCKBD算法:

审核编辑:刘清

-

控制器

+关注

关注

112文章

16317浏览量

177792 -

DRAM

+关注

关注

40文章

2309浏览量

183430 -

存储器

+关注

关注

38文章

7482浏览量

163757 -

DFT设计

+关注

关注

0文章

10浏览量

8881

原文标题:DFT设计—MBIST算法

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

DFT算法与FFT算法的优劣分析

Nvidia is hiring-Senior DFT Engineer

L220 MBIST控制器技术参考手册

CoreLink 2级MBIST控制器L2C-310技术参考手册

ARM L210 MBIST控制器技术参考手册

什么是DFT,DFT是什么意思

DFT的快速算法-FFT

滑动DFT算法在功率谱估计中的应用

基于BEM联合反馈分组DFT的信道估计算法

怎么配置DFT中常见的MBIST以及SCAN CHAIN

DFT如何产生PLL 测试pattern

DFT设计—MBIST算法测试

DFT设计—MBIST算法测试

评论