金属栅极的使用

随着铪基高k材料的引入,人们发现高k介质与多晶硅栅极的兼容性一直是影响高k材料使用的一个障碍。因为栅极的一个关键特性是它的功函数,即自由载流子逃逸所需要的能量。功函数决定器件的阈值电压Vt。传统的栅介电材料 SiO2或SiON采用多晶硅为栅极,功函数取决于多晶硅的掺杂浓度。半导体制造商可以根据设计需要很容易地改变多晶硅掺杂浓度来得到所需的阈值电压。然而随着铪基高k材料的引入,人们发现如果继续使用多晶硅作为栅极材料,铪基材料与多晶硅材料之间会形成Hf-Si键从而产生所谓的“费米钉轧现象”,即功函数被拉向多晶硅能带间隙中央,这种现象在PMOS器件中更为显著,这就使得阈值电压变得不可调制。而金属栅极的使用可以解决栅极和高k栅介质材料的相容性问题。

同时,栅极也面临等比例缩小的挑战。施加在栅极上的电压会将少数载流子从沟道区吸引到电介质和沟道的界面处,形成反型载流子分布。这时会在栅极的两侧形成载流子的累积,以维持电荷中性,这必将耗尽附近半导体的电荷。当半导体的电荷被完全耗尽时,半导体就等于绝缘体了,相当于增大了栅介质的有效厚度。尽管耗尽层厚度只有几个埃的SiO2厚度(对于NMOS为2~4Å,对于PMOS为3~6Å),但是当栅介质厚度降到十几个埃左右时,这一厚度的影响就变得十分显著。由于降低等效氧化层厚度是器件等比例缩小的关键, 因此多晶硅的耗尽就成了一个很大的障碍。

虽然可以通过提高多晶硅栅极的掺杂浓度来提高材料中自由载流子的浓度,以此来缓解多晶硅的耗尽,但是栅极中的掺杂已经接近饱和水平,尤其对PMOS来讲,高浓度硼穿透栅介质已经是十分严重的问题了。而金属中有大量的自由载流子浓度,不会受到耗尽的限制。

另外采用金属栅替代多晶硅栅还可以消除远程库仑散射效应,有效抑制高k栅介质中表面软声子散射引起的沟道载流子迁移率下降。与多晶硅栅/高k介质相比,金属栅/高k介质栅结构具有更高的电子和空穴迁移率,合适的阈值电压,在RMOS和PMOS器件中具有更高的驱动电流性能。

金属栅材料性能的要求

1、合适的有效功函数

有效功函数是高k/金属栅结构中最重要的参数之一,它是影响阈值电压的最主要的因素。其表达式为

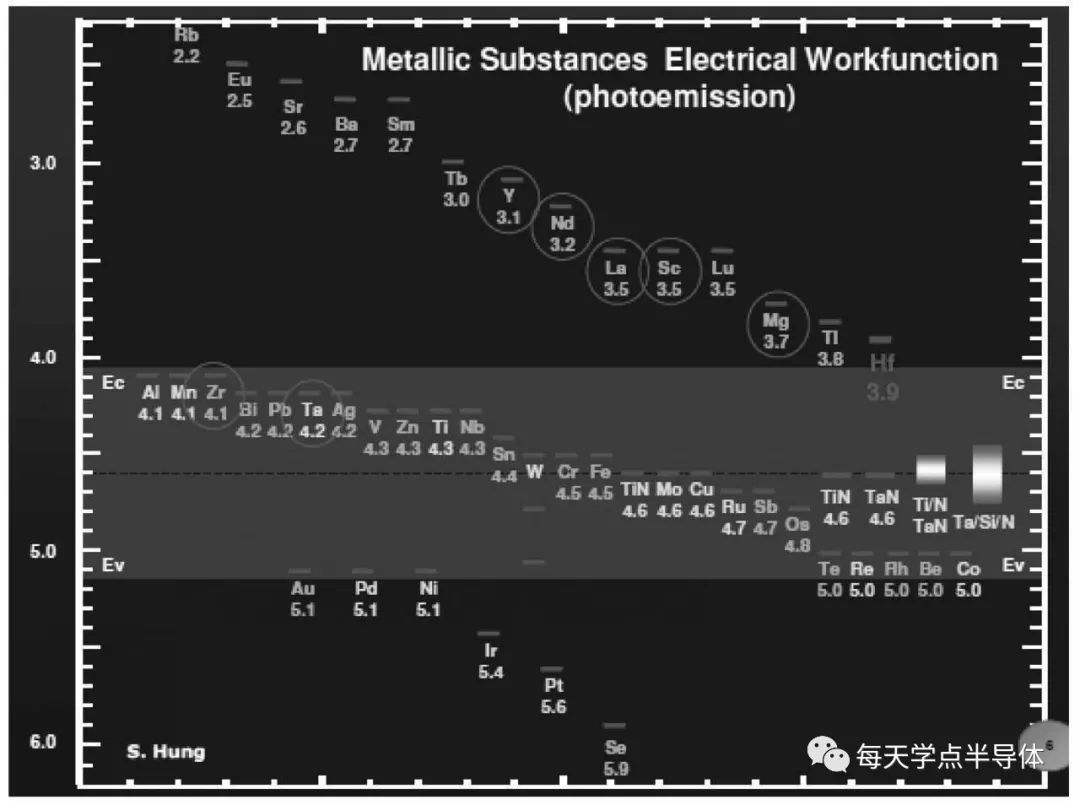

栅金属的功函数需要和沟道中载流子的能量相匹配,也就是说所选金属栅极的功函数必须分别能满足PMOS和NMOS的需求。图6.1所示为不同材料的功函数。除金属的组成外,金属的有效功函数会随沉积方式、晶体结构、底层的介质材料以及所经历的高温过程不同而变化。

图6.1不同金属的功函数

金属栅极的选择通常根据器件的要求不同而选用不同的功函数:一是选择近Si的禁带中央的同一种金属作为PMOS和NMOS器件的栅极,但由于其功函数不可调,通常只适于SOI、双栅晶体管以及 FinFET器件的应用需求;而对于高性能器件,需要选择双金属栅,即功函数分别靠近Si价带和导带的金属材料,作为PMOS(大约5.0~ 5.2eV)和NMOS(大约4.1eV)器件的栅极。双金属栅极工艺具有较高的挑战性,不仅需要选择合适功函数的材料,而且必须能够在不破坏第一层金属的情况下得到第二层金属。

2、较高的热稳定性

热不稳定性可能导致金属材料与高k介质间的相互扩散或化学反应,引发等效氧化物厚度(EOT)增加、阈值电压变化、漏电流增大等效应,使器件电学性能严重衰退。因此栅极金属必须具有高的热稳定性以避免金属沉积和退火过程中产生的氧空位及过度氧化导致的有效功函数偏移。尤其对于先栅极工艺中,栅极金属与高k材料必须经历传统CMOS工艺中激活掺杂杂质采用的1000℃左右高温热处理工艺,在高温退火条件下,获得合适的有效功函数极具挑战性。

3、较低的界面态密度

金属栅与高k介质之间,高k介质与SiO2之间存在着一定的界面态。较高的界面态密度会产生大量的界面固定电荷和陷阱电荷,造成器件性能及可靠性的降低,因此需要较低的界面态密度。金属栅极取代多晶硅在满足功函数和热稳定性要求的同时,不应对器件载流子迁移率、栅漏电流等电学性能和整体可靠性造成影响。

4、HKMG(高k介质层+金属栅极)整合工艺

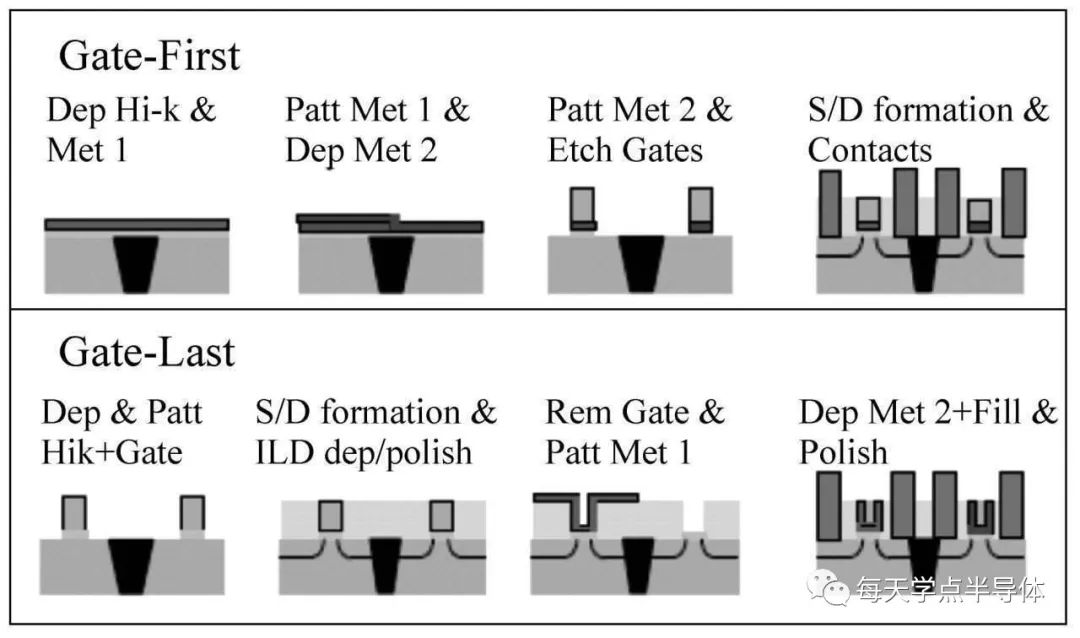

目前在制作HKMG结构晶体管的工艺方面,业内主要存在两大各自固执己见的不同阵营,分别是以IBM为代表的gate-first(先栅极)工艺流派和以Intel公司为代表的gatelast(后栅极)工艺流派(见图6.2)。后栅极工艺又分先高k和后高k两种不同方法,图6.2所示为先高k后栅极工艺,Intel公司在45nm采用,到32nm后转为后高k后栅极工艺。一般来说使用gate-first工艺,高k介质和金属栅极必须经受漏源极退火工艺的高温,因此实现HKMG结构的难点在于如何控制PMOS管的Vt电压(阈值电压);而gate-last工艺虽然工艺复杂,芯片的管芯密度同等条件下要比gate-first工艺低,但是金属栅极不需要经受高温过程,不论先高k还是后高k。因此先栅极金属栅材料的选择非常困难。

图6.2 HKMG整合工艺

5、金属栅极有效功函数的调制

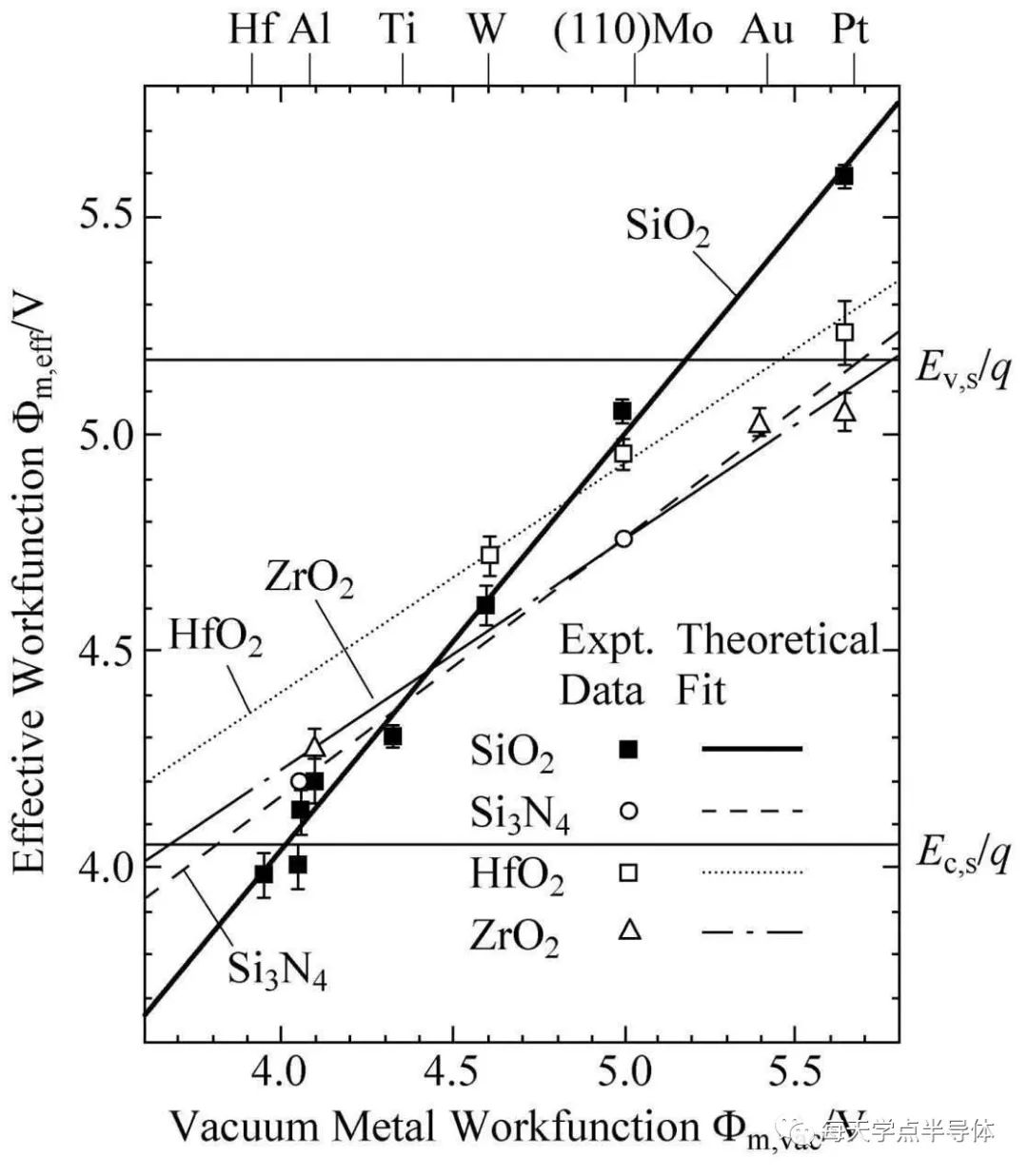

由于金属栅极功函数与栅介质材料有关。高k/金属栅结构界面处存在本征界面态,导致金属费米能级向高k介质的电荷中性能级移动,产生费米能级钉轧效应。这种效应使得有效功函数主要由高k介质决定,大幅缩小了金属栅在高k介质上的有效功函数调制范围(见图6.3),使高k介质上的金属栅有效功函数的调制变得困难。

图6.3不同金属栅极在不同栅介质上的有效功函数

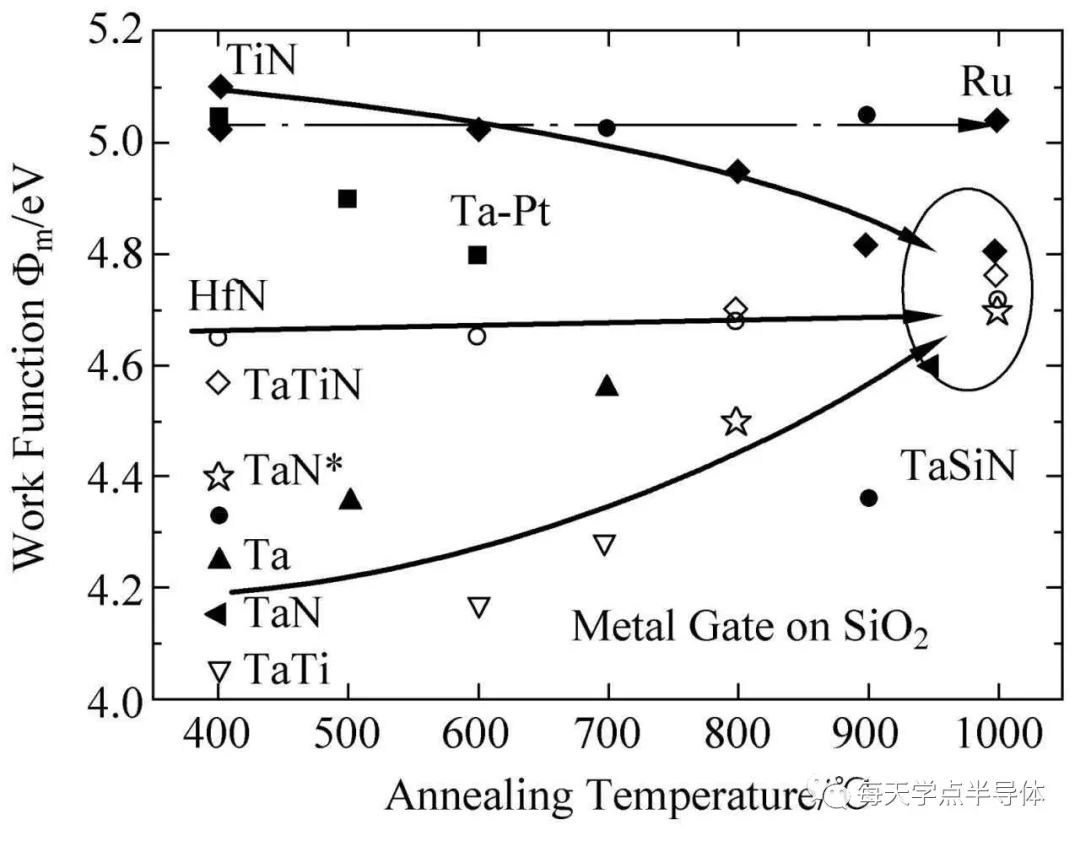

另外,高温退火可能导致金属栅与栅介质间的界面反应和相互扩散,造成有效功函数的严重漂移。图6.4所示为金属栅极/SiO2介质体系,在高温退火后,金属有效功函数移向Si的禁带中央。金属栅极/高k体系同样会遇到同样的问题。因此,金属栅材料的选择会因为HKMG整合工艺不同而不同。而先栅极金属栅材料的选择比后栅极工艺更加困难。

图6.4金属功函数随退火温度变化

早期的解决思路主要是通过改变金属栅极材料的成分获得合适的有效功函数和高的热稳定性与常规CMOS工艺兼容的镍的全硅化工艺是自对准工艺,而且几乎没有栅介质的损伤,是一种比较简单的形成金属栅的方法。由于NiSi的功函数接近硅能带间隙中央,可以通过掺杂(PtSix:5.1eV;Ni(20%)Ta(80%)Si:4.2eV)和改变硅化镍的相态(NiSi:4.5eV;Ni3 Si:4.85eV)对其进行调节。但是高掺杂浓度的硅化物和相控制都很难付诸生产,硅化处理的不完全和组分的微小偏差都会导致栅极功函数出现较大幅度的变化;而且用NiSi做栅极同时也会形成Hf-Si键,不能对阈值电压进行很好的控制。

单元素金属或者合金可以作为金属栅极,但是它们的热稳定性和抗氧化能力较差,只有少数像铂和铱这样的贵金属较好,但是这些金属极难刻蚀,很难与标准工艺集成。

具有良好导电性和合适功函数的金属氧化物如氧化铱(4.32eV)和氧化钌(5.0~5.3eV),同样可以作为MOS器件栅极的候选材料,然而金属氧化物的热稳定性差,并且其成分中的氧在高温退火条件下会向衬底扩散导致衬底被进一步氧化,使得有效功函数变化和等效氧化物厚度(EOT)增加,且金属氧化物对H2的退火气氛十分敏感。

氮的加入可以很大程度上提高金属栅的热稳定性和抗氧化能力。难熔金属的氮化物(TiN、TaN、HfN、WN)与高k栅介质之间有较好的热力学和化学稳定性,界面特性良好,与高k栅介质的集成表现出 良好的电学特性。但由于难熔金属氮化物与高k材料在源漏杂质激活过程中的界面反应、高k介质中的氧空位、偶极子层、金属诱生界面态等引起的费米能级钉轧效应,使金属栅的有效功函数一般被限制在禁带中央附近。

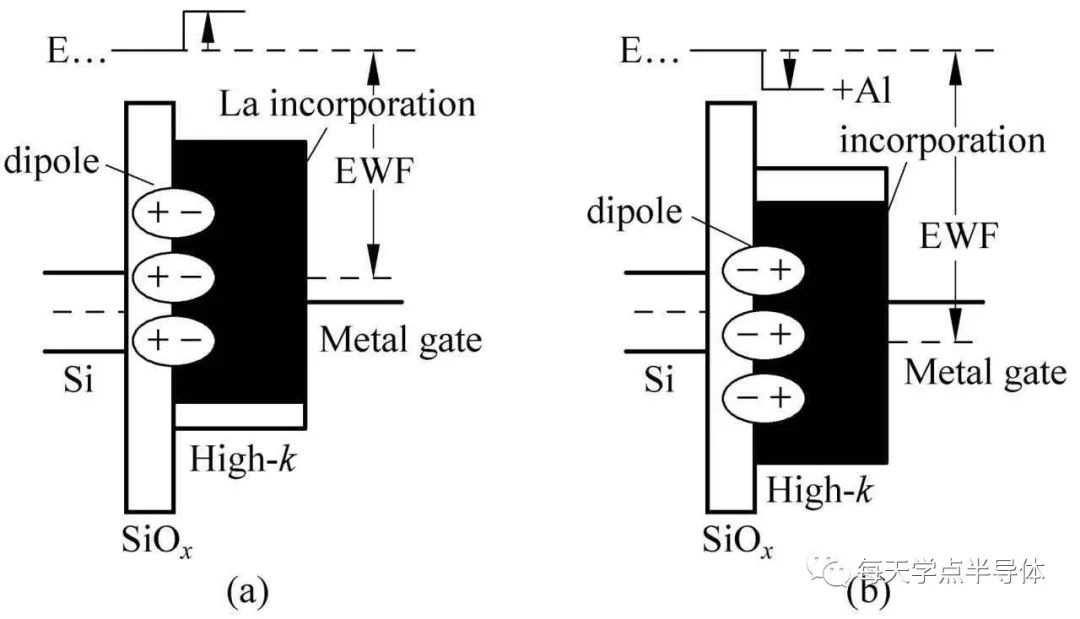

目前对于先栅极工艺,通常采用高k/金属栅的界面调制,通过在界面处引入偶极子层来调节有效功函数。通常采用功函数位于带隙中间的金属(如TiN),而通过在高k介质上(或下)沉积不同的覆盖层来调节Vt。通过覆盖层得到带边功函数的原理是覆盖层与高k材料在高温退火过程中发生互混,最后在高k/SiO2界面处形成偶极子层来实现的。La等适合调节NMOS管有效功函数是因为La2O3中氧的区域浓 度小于过渡层SiO2中的氧的浓度,所以氧会向高k方向移动,最后形成电场是由界面层SiO2指向高k介质的偶极子层,该电场的存在可以改变带边间的势垒差,使NMOS管金属栅的有效功函数从禁带中央附近向导带附近移动;而Al诱生的偶极子层的极性与La形成的偶极子层的极性相反,使PMOS管金属栅的有效功函数从禁带中央附近向价带附近移动,如图6.5所示。但是如前所述,这种方法对NMOS的作用十分明显,而对PMOS效果则不显著,而且由于Al2O3的k值较低,PMOS的EOT也会受到影响。所以高性能器件的PMOS的Vt调节目前仍是先栅极工艺中的主要挑战之一。而采用后栅极工艺,由于不需要经历高温的源漏激活过程,金属材料的选择相对较简单。目前量产的Intel公司主要采用TiN作为PMOS的金属栅极,而通过扩散形成TiAlN 作为NMOS的金属栅极。

图6.5 La、Al元素在高k/SiOx界面产生的偶极子层对有效功函数的影响

6、金属栅极的沉积方法

金属栅极的沉积方法主要由HKMG的整合工艺决定。为了获得稳定均匀的有效功函数,两种工艺都对薄膜厚度的均匀性要求较高。另外,先栅极的工艺对金属薄膜没有台阶覆盖性的要求,但是后栅极工艺因为需要重新填充原来多晶硅栅极的地方,因此对薄膜的台阶覆盖 性及其均匀度要求较高。

目前的功函数金属栅极沉积主要采用原子层沉积(ALD)或射频溅射物理气相沉积法(RFPVD)。两者相比,ALD的方法可以提供很好的阶梯覆盖性,可以得到均匀的金属栅极厚度,为得到稳定的功函数提供保证;而RFPVD的方法可以容易地通过调节反应参数获得不同功函数,同时获得比ALD更高的生产能力。因此先栅极工艺一般选择RFPVD方法沉积功函数金属,后栅极工艺随器件尺寸减小,会逐渐从RFPVD向ALD过渡。

通常情况下,功函数金属的厚度一般选择在50~100Å之间可以获得比较稳定的功函数。

在后栅极工艺中,功函数金属沉积后,需要再沉积金属Al将金属栅极连接出去。一般采用热铝的方法来完成。之前需要溅射法沉积Ti作为黏附层,CVD铝作为籽晶层。

自对准硅化物

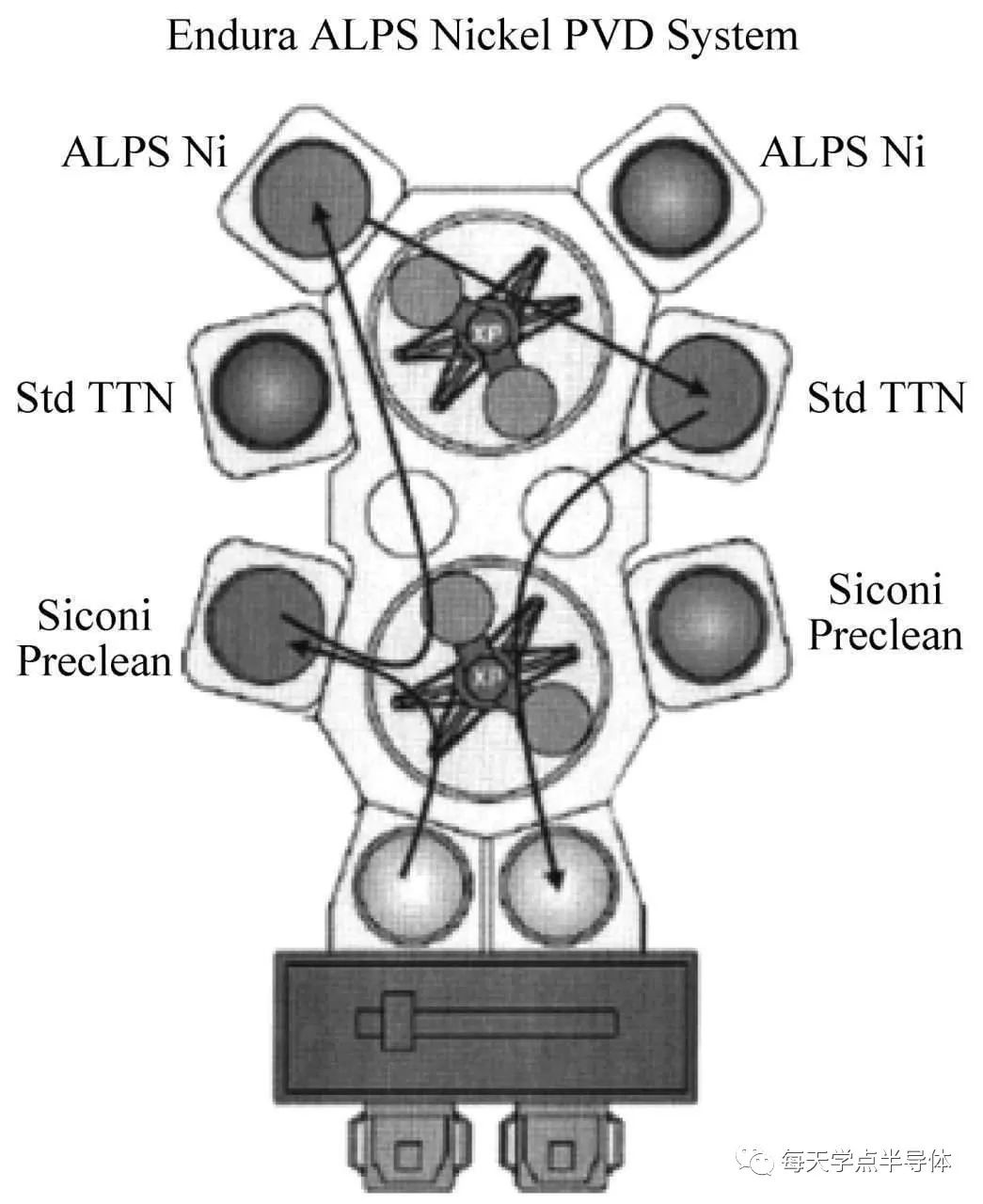

图6.6是标准的Endura物理气相沉积(PVD)镍-铂合金薄膜的机台结构,主要包括三部分:预清洁处理腔(preclean)、镍-铂(NiPt)合金薄膜沉积腔和盖帽层(cap layer)TiN沉积腔。其中根据具体工艺需要,每种腔室可以有一个或多个,以达到最佳的工艺速度。工艺过程中,硅片(wafer)先进入预清洁处理腔,以去除硅片表面的自然氧化物(native oxide),然后进入镍-铂合金薄膜沉积腔沉积一层镍-铂合金薄膜,最后进入TiN沉积腔生成盖帽层。下面对这三种 工艺腔进行详细描述。

图6.6标准的Endura物理气相沉积镍-铂合金薄膜机台

预清洁处理

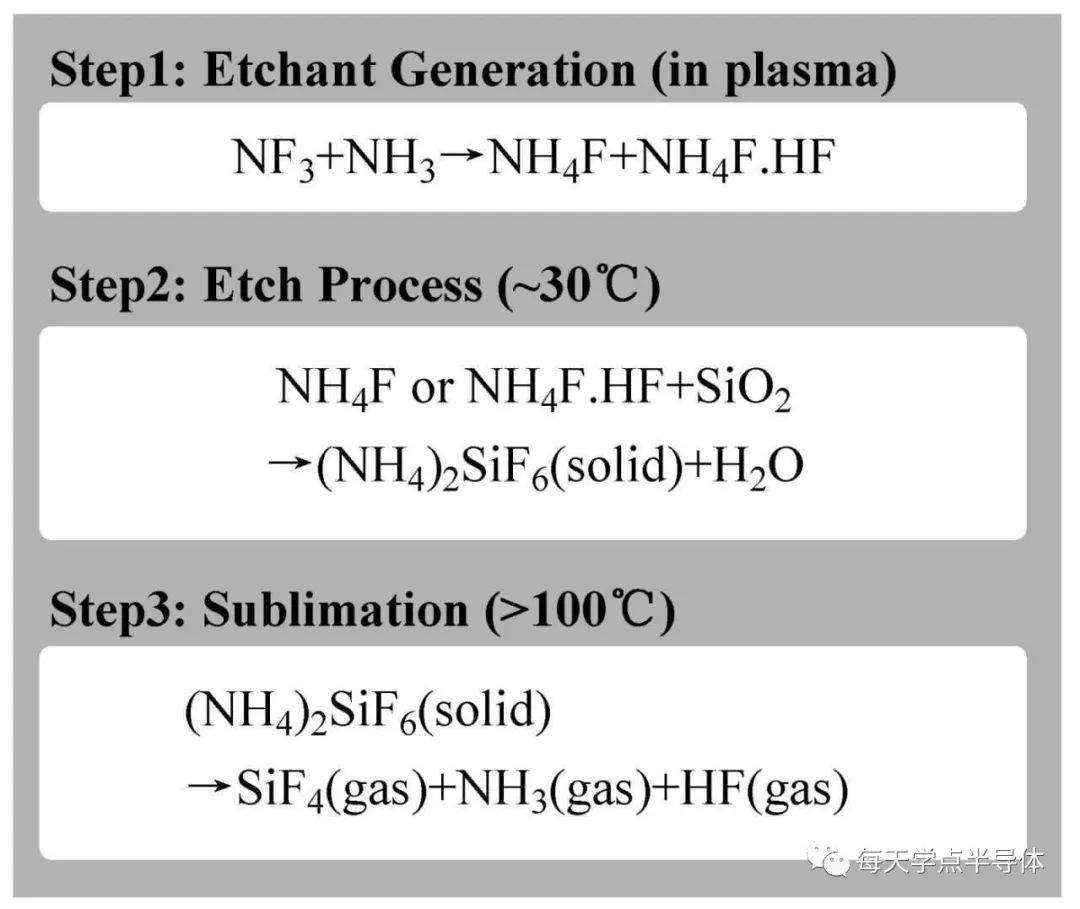

当集成电路技术发展到65nm以下时,传统的预清洁处理(preclean)方式HF dip和Ar sputter已经不能满足制程的需要了,必须采用先进的SiCoNi预清洁处理腔。它主要包括两个步骤:刻蚀(etch)和升华(sublimation)。NF3和NH3在plasma的作用下产生活性粒子,活性粒子在低温条件下与硅片上的SiO2发生反应生成易升华的化合物(NH4)2SiF6,然后在高温下将化合物(NH4)2SiF6升华以达到除去native oxide的效果。其反应机理如图6.7所示

图6.7 SiCoNi的反应机理

与HF dip和Ar sputter相比,SiCoNi具有诸多优点

(1)SiCoNi可以消除HF dip过程中存在的Q-time问题。由于HF dip与金属薄膜的生长必须在不同的机台上进行,在硅片传输的过程中,与大气接触使得硅片上重新生长一层薄薄的SiO2薄膜。

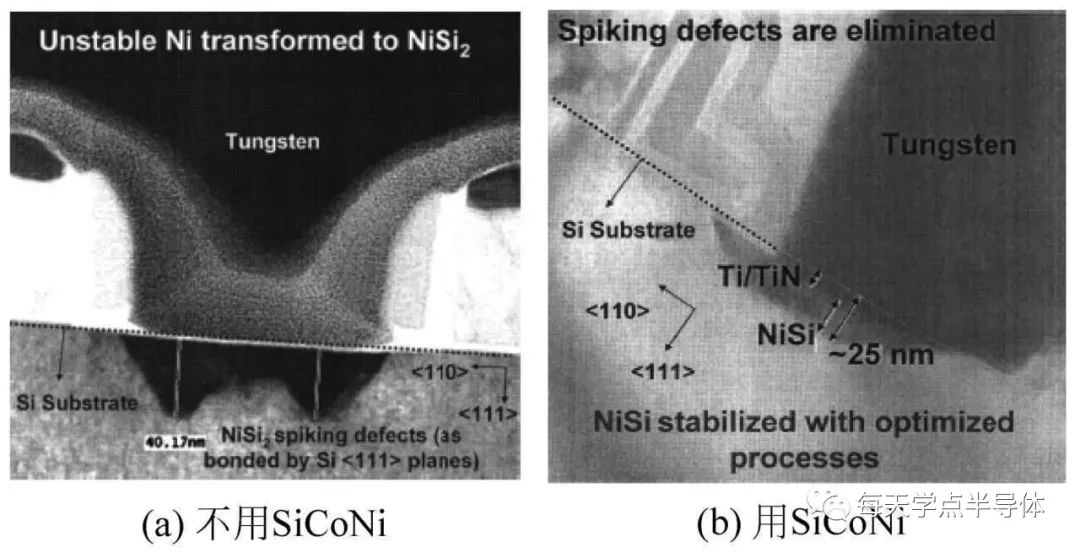

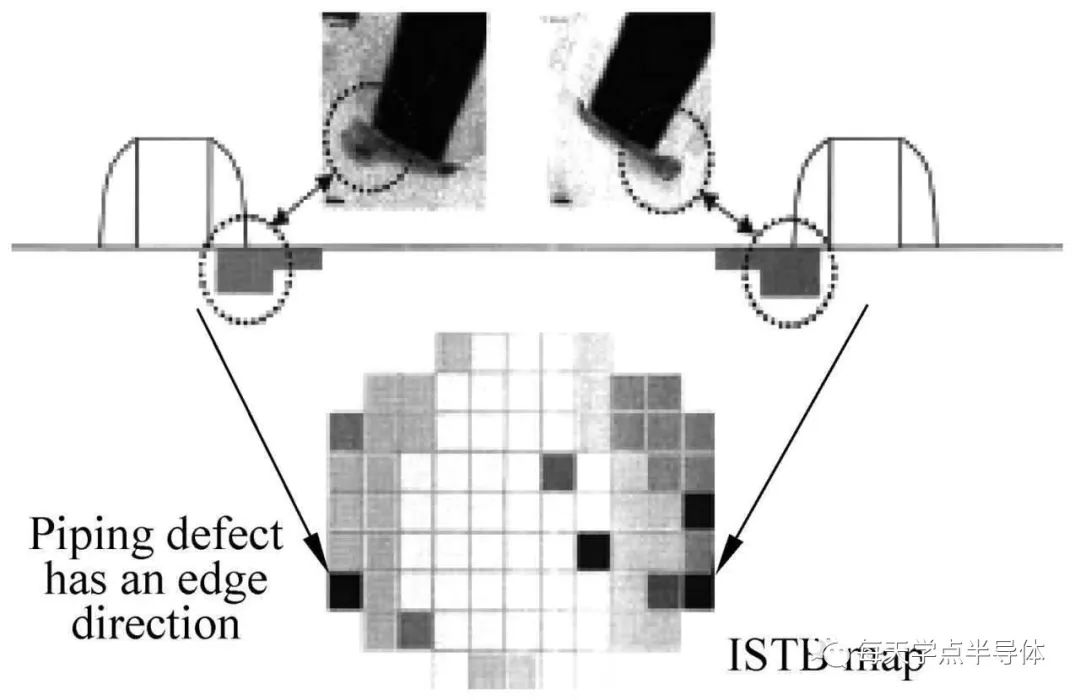

(2)SiCoNi是一种柔和的化学刻蚀的方式。Ar sputter preclean方式会在反应腔内产生比较强的plasma,对硅片表面产生强大的轰击效应,在除去SiO2的同时,也对硅片表面产生破坏作用,使硅片表面变得粗糙,缺陷增加,在形成硅化物的过程中容易形成尖峰状缺陷(spiking),见图6.8(a)。另外,反应腔内的plasma也会对硅片上的器件产生破坏作用。而SiCoNi采用remote plasma的方式,在反应腔内没有plasma,因此,对硅片表面和器件的破坏都较小,消除了尖峰状缺陷,见图6.8(b)。

图6.8 SiCoNi对PMOS上的spiking defect的影响

(3)SiCoNi是一种高选择性的预清洁方式,SiO2: Si>20:1,SiO2 : Si3N4>5:1。

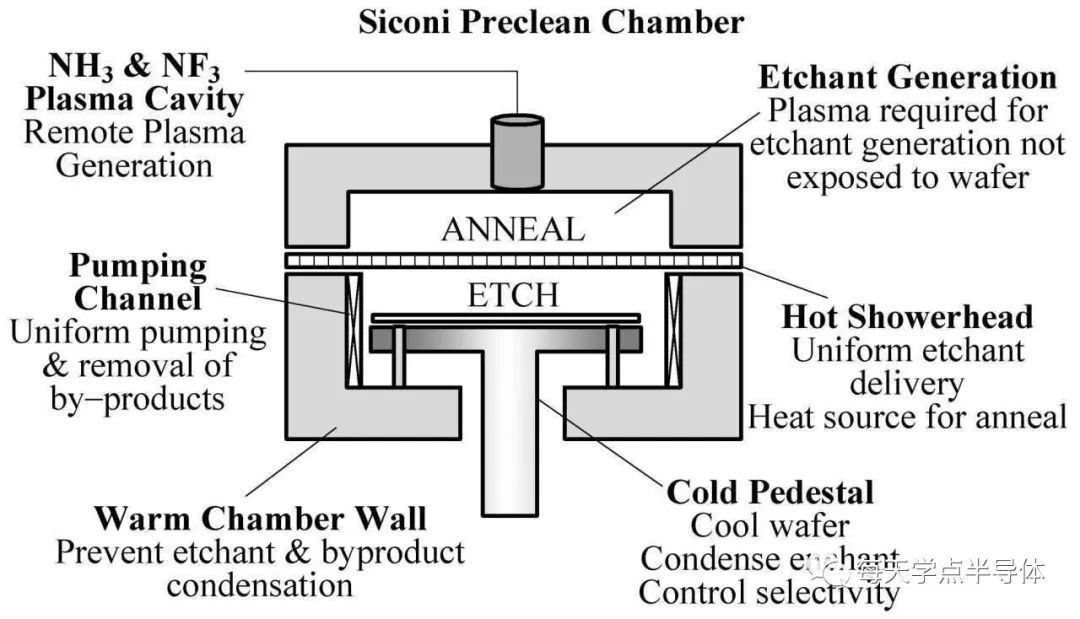

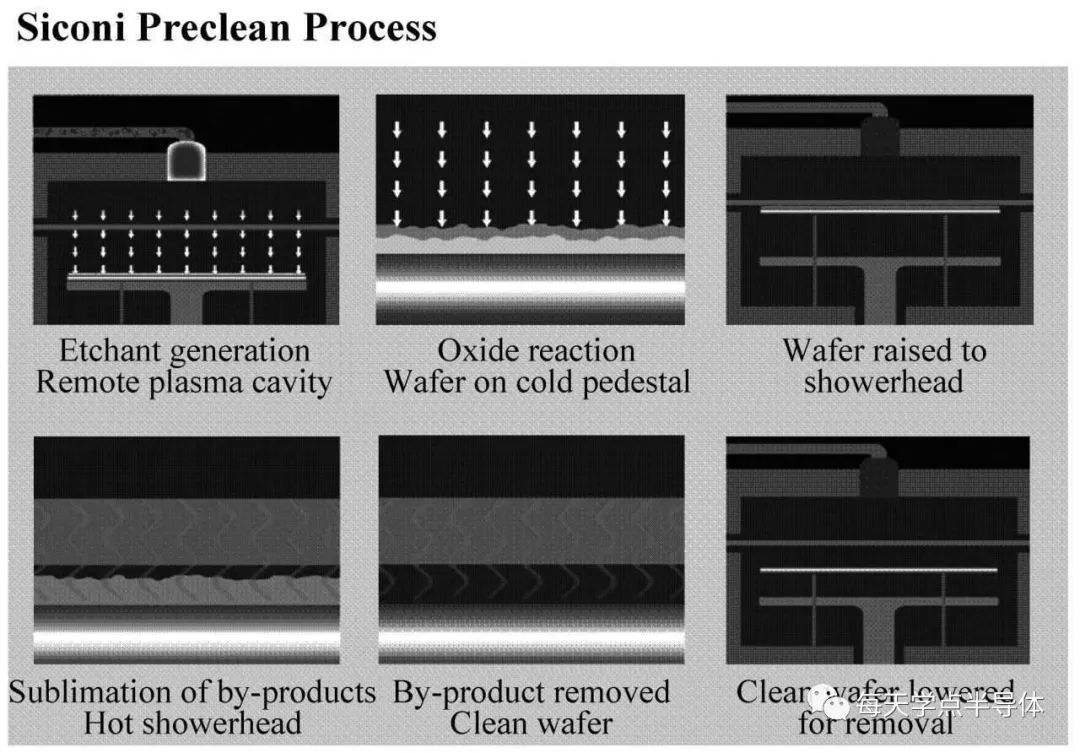

图6.9为SiCoNi反应腔的结构,主要包括remote plasma发生器、hot showerhead、cold pedestal等主要部件。remote plasma产生器的主要作用是将NF3和NH3的混合气体在plasma作用下生成活性粒子。hot showerhead的温度为180℃左右,硅片上的SiO2生成易升华的化合物(NH4)2SiF6后,会被升举而靠近hot showerhead,将(NH4)2SiF6升华。由于(NH4)2SiF6只有在低温条件下才会生成,因此,cold pedestal的温度较低,接近室温,为(NH4)2SiF6的生成提供条件。图6.10为SiCoNi工艺过程,硅片进入反应腔后,NF3和NH3的混合气体在remote plasma发生器中产生活性粒子,活性粒子进入反应腔后与 硅片表面的SiO2反应生成易升华的化合物(NH4)2SiF6,然后将硅片升举到hot showerhead附近,利用辐射加热的方式将硅片表面的(NH4)2SiF6升华,然后由真空泵将气体抽走。在实际工艺过程中,有时一步升华很难把硅片表面的副产物去除干净,往往采用两步或多步升华以达到彻底除去副产物的目的。

图6.9 SiCoNi反应腔的结构简图

图6.10 SiCoNi的工艺过程

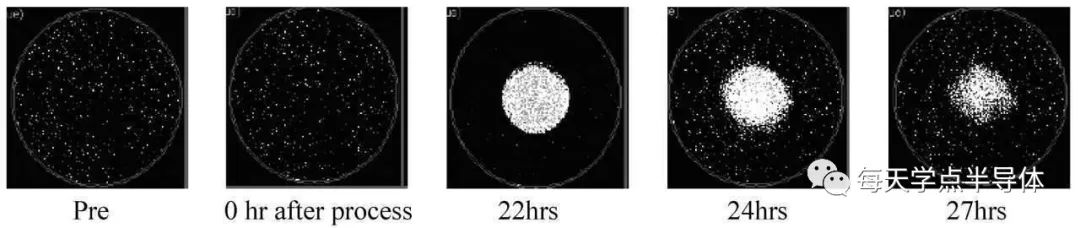

在实际的集成电路制造工艺中,为了确保机台在生产产品时不会出现问题,需要定期对机台进行测试(monitor),对于SiCoNi反应腔来说,当用长有SiO2的空白硅片测试在工艺过程中的颗粒(particle)缺陷时,发现将经过SiCoNi preclean的硅片放置一段时间之后,在硅片的中心会出现大量的particle,随着时间的增加,这种particle会自动减少,直至消失,这就是所谓的“幽灵(ghost)”缺陷,见图6.11,这会影响对机台实际状况的评估。为了克服这个缺陷,得到没有ghost效应的测试结果,可采用裸露的硅片作为测试硅片。

图6.11 ghost效应

镍铂合金沉积

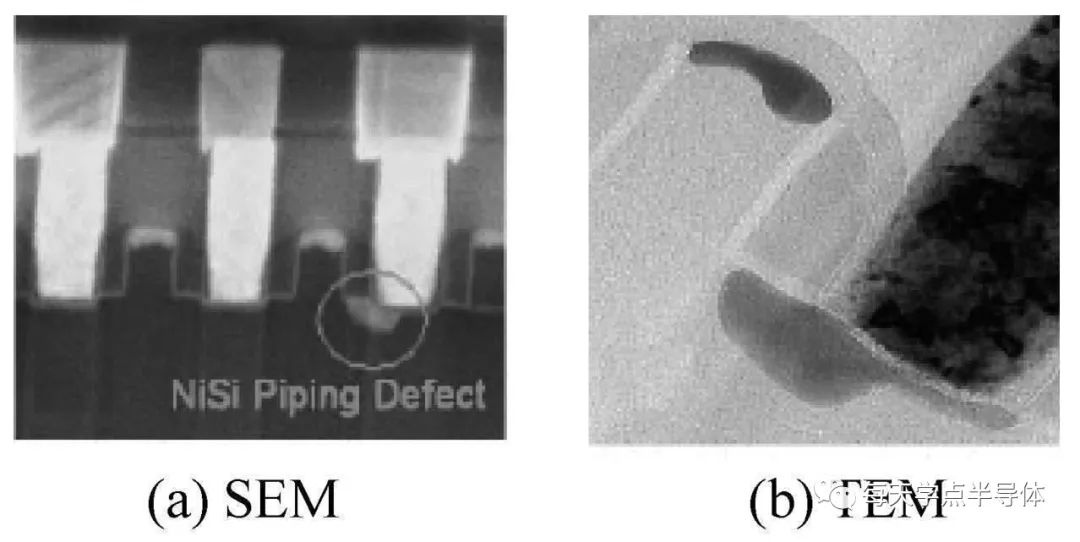

当集成电路技术发展到65nm以下时,必须使用Ni silicide。但如果使用纯镍的薄膜作为形成silicide的金属,由于镍原子的扩散能力很强,则会在源漏极上出现如图6.12所示的侵蚀(encroachment)缺陷。Encroachment缺陷会增加漏电,降低良率。因此,在实际的集成电路制造工艺中,常常采用含铂5~10atom%的镍铂合金作为形成silicide的金属。

图6.12 Encroachment缺陷照片

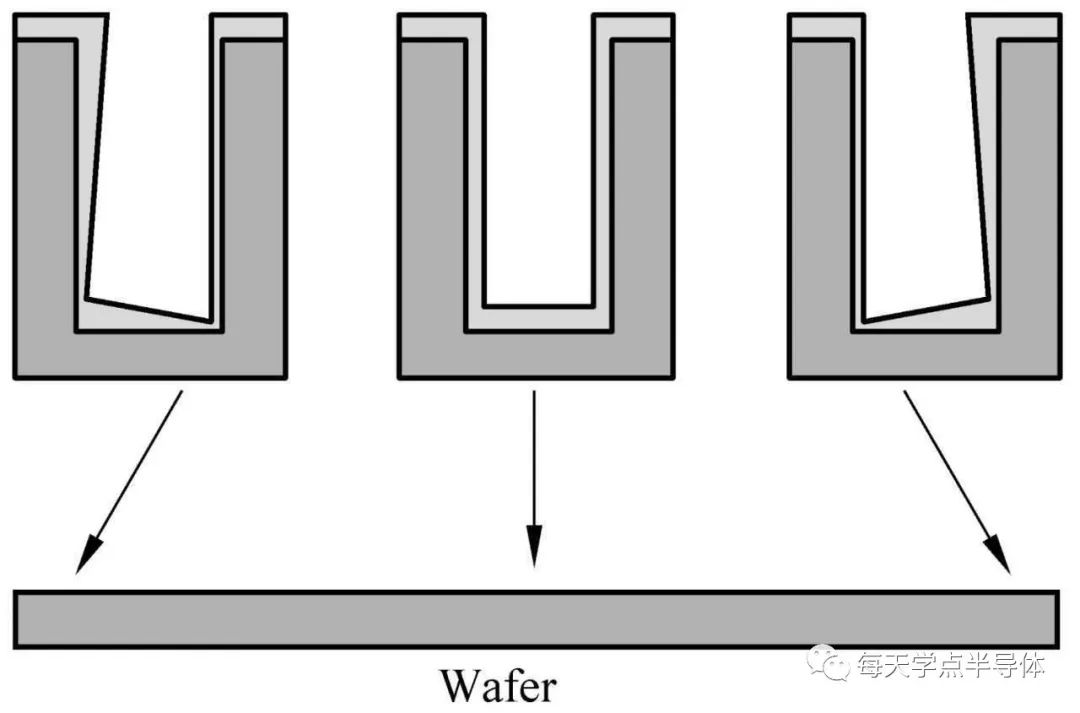

随着技术的发展,除了需要Ni-Pt合金之外,传统的PVD镀膜的机台已经不再满足制程的需要。尤其是当发展到65nm时,线宽进一步缩小,镀膜之前的深宽比(aspect ratio)进一步增加,这就要求镀Ni-Pt薄膜的机台具有比较好的台阶覆盖率(step coverage),另外,物理气相沉积长膜方式会受到硅片上几何结构的影响而存在不对称性(asymmetry),对于槽(trench)和通孔(via)而言,离硅片中心较远的一边比较容易沉积,厚度较厚,而离硅片中心较近的一边由于受到侧壁的遮挡效应(shadow effect),厚度较薄,如图6.13所示。在对Ni-Pt薄膜进行热处理形成硅化物的过程中,较厚的一边所形成的硅化物的厚度较厚,严重的情况下甚至会钻到栅极(gate)下面,形成如 图6.14所示的encroachment defect,增加漏电,严重降低器件的良率。

因此,必须使用型号为ALPS(Advanced Low Pressure Sputtering)的Ni-Pt沉积腔。

图6.13 Shadow effect和不对称性

图6.14 Encroachment缺陷在硅片上的分布

与传统的PVD相比较,ALPS主要有三个方面的改进以增强台阶覆盖率和降低不对称性。

(1)增加硅片和靶材之间的距离(long through),使从靶材上溅射出来的大角度的粒子沉积到反应腔的侧壁上,只有小角度的粒子可以到达硅片表面。

(2)降低反应压力(low pressure),压力越低,气体分子的平均自由程会越大,粒子的碰撞概率降低,这样可以确保更具有方向性的沉积。

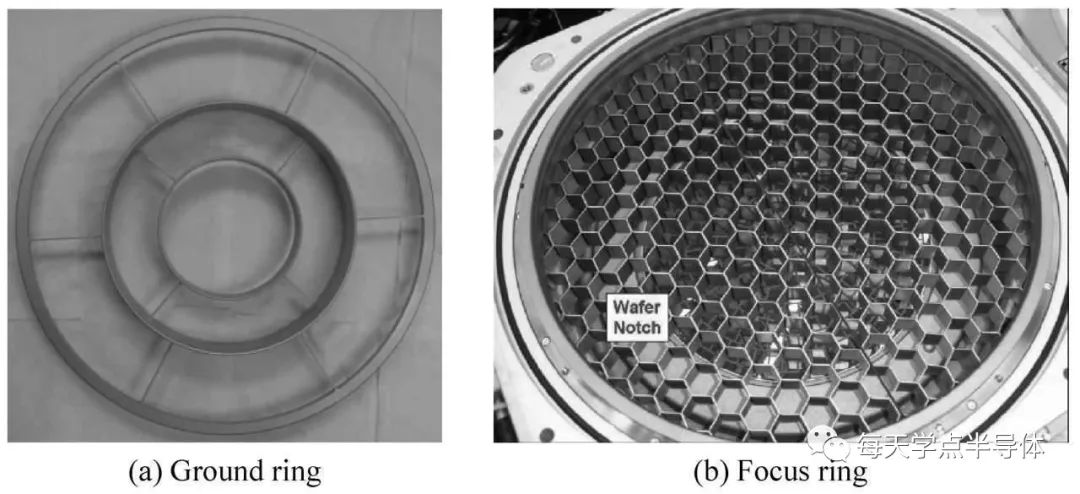

(3)在硅片和靶材之间安装基环(ground ring),如图6.15(a)所示。基环可以将一些大角度的粒子过滤,确保到达硅片表面的都是小角度的粒子,以增加阶梯覆盖率和降低不对称性。当制程发展到45nm时,线宽进一步缩小,ALPS不再满足阶梯覆盖率和不对称性的要求,此时,需要对ALPS进行改进,采用ALPS ESI(Extend Salicide Integration),用聚焦环(focus ring)替代基环,见图6.15(b)。

图6.15 Ground ring和Focus ring的实物图

盖帽层TiN沉积

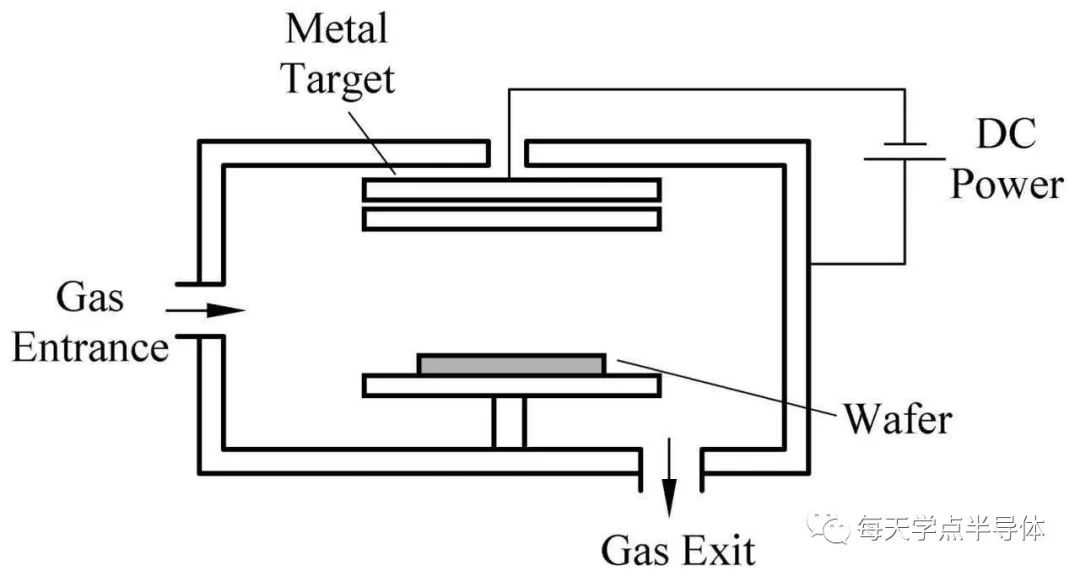

盖帽层(cap layer)TiN主要是为了保护Ni-Pt薄膜,对阶梯覆盖率和不对称性的要求较低,因此,常采用标准的PVD方式,其反应腔结构简图如图6.16所示。

图6.16标准PVD反应腔的结构简图

审核编辑:黄飞

-

集成电路

+关注

关注

5396文章

11643浏览量

363700 -

射频

+关注

关注

104文章

5627浏览量

168325 -

PVD

+关注

关注

4文章

51浏览量

17071 -

金属栅极

+关注

关注

0文章

5浏览量

5159 -

ALPS

+关注

关注

0文章

12浏览量

12226

原文标题:金属薄膜沉积工艺及金属化

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

一文详解金属薄膜沉积工艺及金属化

一文详解金属薄膜沉积工艺及金属化

评论