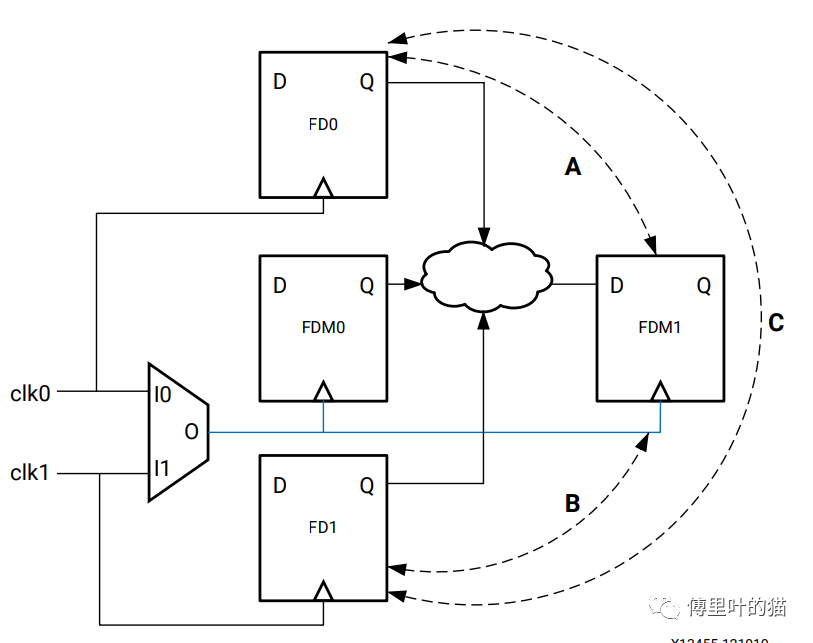

时序场景如下图所示,clk0和clk1两个时钟输入,经过BUFGMUX后,输出到后面的逻辑,但同时clk0和clk1还分别驱动了其他逻辑。

此时,如果路径A/B/C都不存在,其中A路径表示clk0与选择器输出的时钟之间的数据交互,B路径表示clk1与选择器输出的时钟之间的数据交互,C路径表示clk0和clk1之间的数据交互,那么使用下面的约束就可以了:

set_clock_groups-logically_exclusive-groupclk0-groupclk1

如果路径 A、B 或 C 仅有一个存在,那么 clk0 和/或 clk1 与多路复用时钟直接交互。

则需要使用下面的约束:

create_generated_clock-nameclk0mux-divide_by1 -source[get_pinsmux/I0][get_pinsmux/O] create_generated_clock-nameclk1mux-divide_by1 -add-master_clockclk1 -source[get_pinsmux/I1][get_pinsmux/O] set_clock_groups-physically_exclusive-groupclk0mux-groupclk1mu

logically_exclusive和physically_exclusive的区别在于:

-logical_exclusive

logical_exclusiveisusedfortwoclocksthataredefinedondifferentsourceroots. Logicallyexclusiveclocksdonothaveanyfunctionalpathsbetweenthem,butmighthavecouplinginteractionswitheachother. Anexampleoflogicallyexclusiveclocksismultipleclocks,whichareselectedbyaMUXbutcanstillinteractthroughcouplingupstreamoftheMUXcell. Whentherearephysicallyexistingbutlogicallyfalsepathsbetweenthetwoclocks,use"set_clock_groups-logical_exclusive".

-physical_exclusive

physical_exclusiveisusedfortwoclocksthataredefinedonthesamesourcerootby"create_clock-add". Timingpathsbetweenthesetwoclocksdonotphysicallyexist. Asaresultyouwillneedtouse"set_clock_groups-physical_exclusive"tosetthemasfalsepaths.

简而言之,logical_exclusive用于选择器的电路,两个时钟的source不一样;而physical_exclusive两个时钟的source是一样,比如在同一个时钟输入口,但可能会输入两个不同的时钟。

再回到最上面的问题,如果路径A、B和C有一条存在,说明时钟之间有交互,就不能简单的使用logical_exclusive,而是要为这两个时钟都创建一个衍生时钟,但这两个衍生时钟属于physical_exclusive。

审核编辑:刘清

-

时钟

+关注

关注

10文章

1716浏览量

131302 -

选择器

+关注

关注

0文章

106浏览量

14511 -

CLK

+关注

关注

0文章

127浏览量

17109

原文标题:经过BUFGMUX的时钟该如何约束

文章出处:【微信号:傅里叶的猫,微信公众号:傅里叶的猫】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

经过BUFGMUX的时钟该如何约束呢?

经过BUFGMUX的时钟该如何约束呢?

评论