近日,备受关注的 Arm TechSymposia 技术大会在上海圆满闭幕。在这次盛会中,作为国内首家数字 EDA 供应商的思尔芯成为焦点,其在台北、东京、深圳、北京和上海的巡回展出吸引了业界的广泛关注,为 Arm 外置支持方案提供了更高效的解决方案。

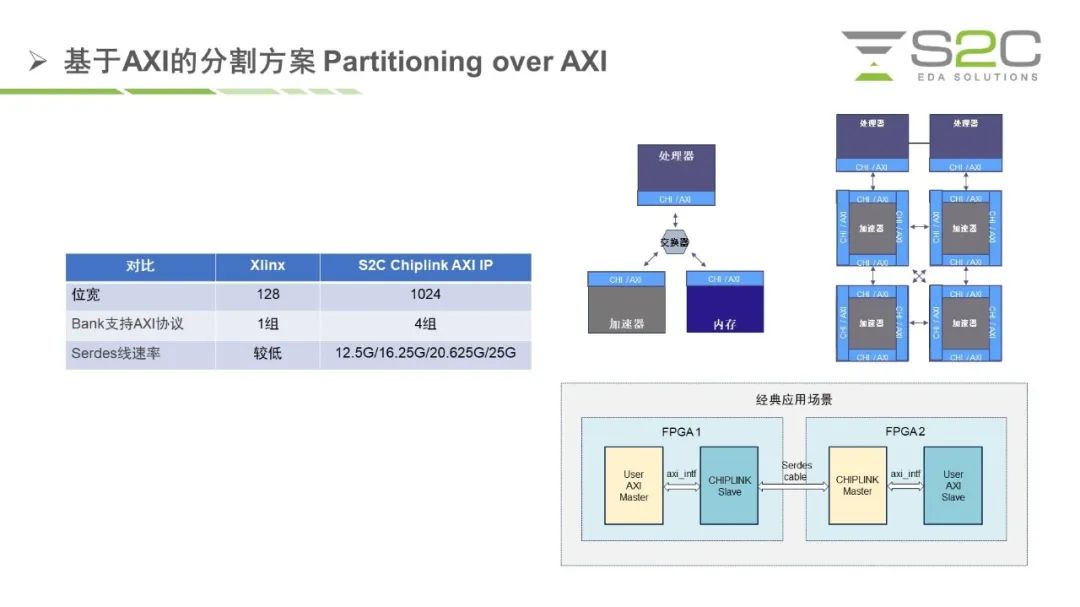

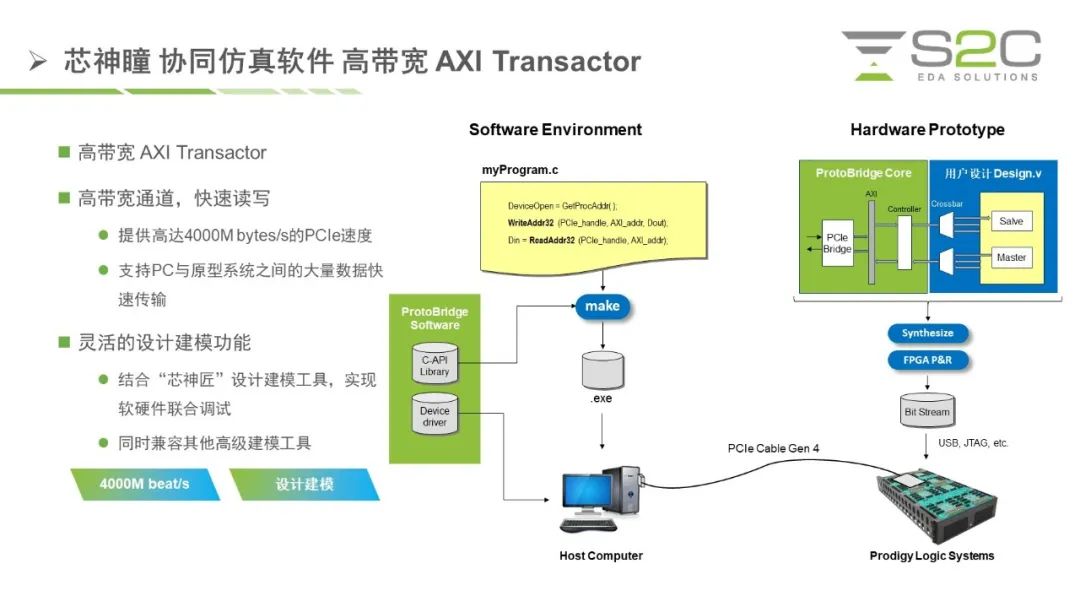

在 Arm 的外置支持方案中,通过 Thunder-bus IP 实现 Zynq UltraScale+ MPSoC 与原型验证系统之间的 AXI 接口通信。然而,思尔芯的 Chiplink AXI IP 方案在这方面取得了更显著的突破。在多核 Arm 验证方案中,思尔芯采用了低延迟的 AXI Chip to Chip IP,实现了基于 AXI 接口的多核 Arm 间高效通信。其 Chiplink AXI IP 方案支持高达 1024 位宽的 AXI DATA 位宽,并能够在每个 Bank 支持最多 4 组 AXI 协议,同时提供多种可配置的 Serdes 线速率(12.5G、16.25G、20.625G、25G),使得多核 Arm 之间的通信速度能够达到 100MHz。有参观者表示:“这个 Chiplink AXI IP 方案真是令人印象深刻,对于我们未来的项目将非常关键。” 此外,思尔芯还展示了芯神瞳协同仿真软件 ProtoBridge,它提供了一个高带宽的 AXI Transactor。提供高达 4000M bytes/s 的 PCIe 速度,实现快速读写。这个 Transactor 利用了业界广泛采用的 AXI-4 总线协议和独有的专利技术*(* 专利号:ZL201911239764.5),实现了 PC 软件到原型验证环境的无缝连接。它创建了一个高吞吐量的数据通道,允许在 FPGA 和 PC 主机之间进行大量的事务级数据交互。它还可以兼容其他高级建模工具例如思尔芯的“芯神匠”架构设计软件,实现软硬件联合调试。

此外,思尔芯还展示了芯神瞳协同仿真软件 ProtoBridge,它提供了一个高带宽的 AXI Transactor。提供高达 4000M bytes/s 的 PCIe 速度,实现快速读写。这个 Transactor 利用了业界广泛采用的 AXI-4 总线协议和独有的专利技术*(* 专利号:ZL201911239764.5),实现了 PC 软件到原型验证环境的无缝连接。它创建了一个高吞吐量的数据通道,允许在 FPGA 和 PC 主机之间进行大量的事务级数据交互。它还可以兼容其他高级建模工具例如思尔芯的“芯神匠”架构设计软件,实现软硬件联合调试。 在下午的技术分论坛上,思尔芯作为 Arm 生态伙伴之一,受邀发布一场重要的技术演讲。思尔芯产品经理秦英明就公司自主研发的芯神鼎硬件仿真系统进行了深入讲解。该系统已在基于 Arm 架构的芯片系统级验证中取得广泛应用。其提供的多种加速仿真模式,如电路内仿真(In-CircuitEmulator)、事务级仿真(Transaction Based Acceleration)和混合仿真(Hybrid Emulation)等,展示了思尔芯在 EDA 技术领域的深厚实力。特别是混合仿真模式,通过 Qemu 平台实现真实的 Arm 内核系统模拟,结合 TLM 模型和 SCEMI 协议,构建了一个完整的 Arm 内核+外设混合仿真环境。

在下午的技术分论坛上,思尔芯作为 Arm 生态伙伴之一,受邀发布一场重要的技术演讲。思尔芯产品经理秦英明就公司自主研发的芯神鼎硬件仿真系统进行了深入讲解。该系统已在基于 Arm 架构的芯片系统级验证中取得广泛应用。其提供的多种加速仿真模式,如电路内仿真(In-CircuitEmulator)、事务级仿真(Transaction Based Acceleration)和混合仿真(Hybrid Emulation)等,展示了思尔芯在 EDA 技术领域的深厚实力。特别是混合仿真模式,通过 Qemu 平台实现真实的 Arm 内核系统模拟,结合 TLM 模型和 SCEMI 协议,构建了一个完整的 Arm 内核+外设混合仿真环境。

在大会中,Arm 的高级副总裁 Mohamed Awad 强调了公司致力于打造完整且全面的解决方案,旨在加快合作伙伴产品上市的速度。这一战略使合作伙伴能够更专注于创新解决方案的开发,推出更多新产品和服务,以实现市场差异化。

作为 Arm 生态的合作伙伴,思尔芯在此次技术大会上的表现是这一战略的完美体现。公司展示的创新技术和解决方案,不仅展现了其对市场需求和未来趋势的深刻理解,也彰显了其在推动行业发展和技术创新方面的重要作用。思尔芯的贡献不仅加强了与 Arm 的合作关系,也为整个技术生态系统带来了新的活力和可能性。

-

ARM

+关注

关注

134文章

9104浏览量

367861 -

eda

+关注

关注

71文章

2764浏览量

173360 -

思尔芯

+关注

关注

0文章

123浏览量

1297

发布评论请先 登录

相关推荐

LoRaWAN网络在智慧水务中的创新解决方案

“2025 IC风云榜”揭晓,思尔芯获“年度最佳解决方案奖”

锐成芯微亮相Arm Tech Symposia年度技术大会

2024 Arm Tech Symposia圆满落幕,思尔芯创新方案备受瞩目

Arm为用户带来卓越的 AI 体验

Arm成功将Arm KleidiAI软件库集成到腾讯自研的Angel 机器学习框架

面向未来的智能视觉参考设计与汽车架构,思尔芯提供基于Arm技术的创新方案

思尔芯亮相IIC Shenzhen,创新解决方案赋能RISC-V芯片设计

Arm邀您相约2024全球CEO峰会

Arm Tech Symposia年度技术大会即将来袭

思尔芯亮相芯和半导体大会,以数字前端EDA解决方案应对设计新挑战

梯度科技入选2023年信息技术应用创新解决方案名单

思尔芯受邀参加CCF Chip 2024大会

兆芯金融方案入选工信部2023年信息技术应用创新典型解决方案

Wi-Fi 7射频IP验证系统发布!思尔芯EDA助力Sirius Wireless加速芯片设计

思尔芯在Arm Tech Symposia大会上展现基于 Arm 的 Chiplink AXI IP 创新解决方案

思尔芯在Arm Tech Symposia大会上展现基于 Arm 的 Chiplink AXI IP 创新解决方案

评论