本文翻译转载于:Cadence blog

作者:Reela

在身处技术驱动的大环境中,半导体设计需要做到更迅速、更节能以及更稳健。为了满足这一需求,半导体制造企业需要不断突破技术创新。通过对更多参数及其影响的分析,客户才能实现较现行设计方法更优秀的 PPA 目标。例如,全局额定值或全局的裕度会造成性能和功耗的显著浪费。

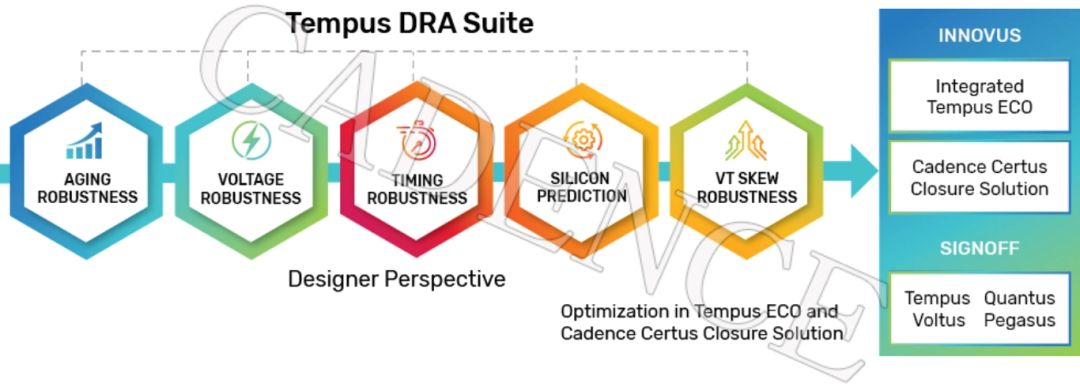

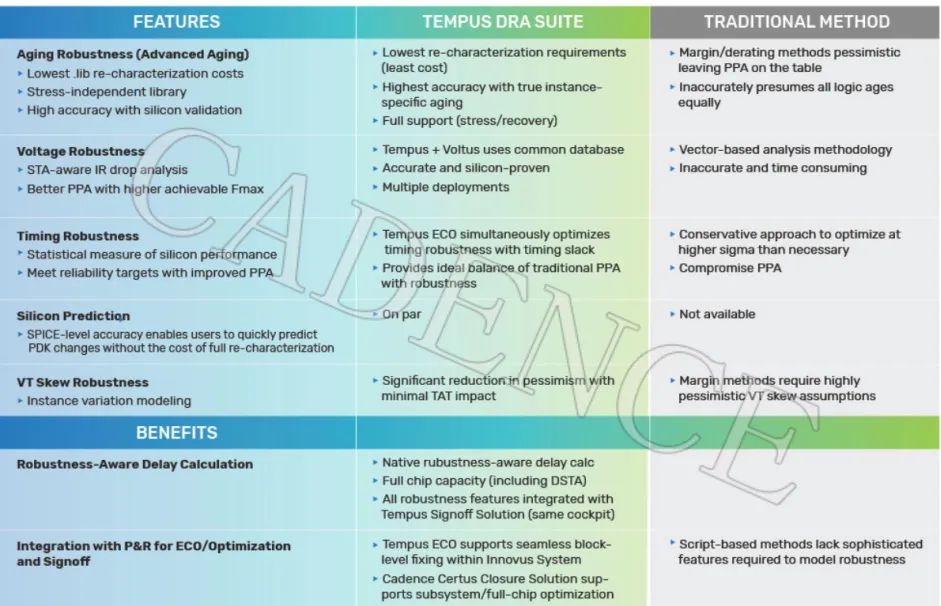

为了应对类似挑战,Cadence 持续创新并开发了 Cadence Tempus 设计稳健性分析(DRA)套件,提供解决上述问题所需要的分析能力。该套件采用先进的建模算法,赋能工程师分析,识别并纠正对变化极为敏感的关键设计要素,包括适用于模块级的 Tempus ECO Options 和子系统/全芯片级的 Cadence Certus 收敛解决方案,两者皆可在 Innovus 设计实现系统中调用。通过充分发挥套件的高级分析特性,客户可以强化设计稳健性,优化功耗、性能和面积(PPA)目标,较传统基于裕度的方法实现最高达 10% 的 PPA 目标提升。

TempusDRA 套件

Tempus DRA 套件集合了卓越的分析能力,针对老化效应、电压降和阈值电压偏斜等不同类型的时序偏差,解决设计层的稳健性问题。该套件包括 5 种高级分析能力,分别适用于稳健半导体设计的特定流程。

老化稳健性

01

Tempus DRA 套件以其卓越的老化稳健性分析能力在业界独树一帜,PPA 目标最高可提高 10%,适用于汽车、航空航天、消费者电子、移动设备和大规模计算等领域。该套件允许工程师在 Cadence Liberate Library 表征化流程工具内控制老化表征环境及参数,提供老化环境的完整分析结果,并通过统计学图表直观呈现应力和恢复状态。

与老化感知时序和限制结合,老化稳健性可以实现 SPICE 级精度的卓越 PPA 结果。在台积电 TMI 和其他 SPICE 可靠性模型的支持下,可以跟踪任意场景下的静态时序分析(STA)、实例老化、非统一老化及恢复模型选择,并且能调节 STA 的最优设置。得益于此,老化效应导致的非必要延迟被清除,进一步加速设计收敛。

电压稳健性

02

电压稳健性分析与 Tempus 电源完整性(PI)和 Voltus IC 电源完整性解决方案无缝集成,大幅提升了现有的签核解决方案。该集成采用了新一代(IR)压降分析和修复技术。电压稳健性分析通过 Tempus ECO Option 实现修复流程的自动化,并通过优化 Victim 及 Aggressor 信号路径解决压降问题。值得注意的是,该分析可以识别传统 IR 压降签核方法容易忽略的时序违例,防止可能导致高昂成本硅片失效的发生。最大 IR 压降设计裕度的降低也可以帮助实现更优的 PPA 目标。

时序稳健性

03

时序稳健性分析是 Tempus DRA 套件的第三项分析能力。这项强大的能力可以通过对硅片性能的统计学测量而达到时序的准确性,在符合 Sigma 可靠性要求的同时显著提高设计 PPA。其用户友好的界面可以加速设计局部更改(ECO)流程,提供相较于传统 SPICE 蒙特卡洛分析更直截了当的方法。

硅预测

04

硅预测是 Tempus DRA 套件的第四项分析能力,专注于硅片特性的持续调优,可以对硅片的设备模型、库和目标设备模型提供快速反馈,帮助设计工程师对设计进行快速调整。硅预测支持包括 PBA(物理设计、构建和分析),GBA(全局构建与分析)等设计的各个阶段,并在 Tempus 时序解决方案、Tempus ECO Option 和 Innovus 设计实现系统中可用。

设计工程师可以用硅预测功能建立模型与硬件的相关性,获得理想的硅片性能,并在 Tempus 时序和 Liberate 表征化流程期间实现精准的统计学建模,在硅前静态时序分析(STA)签核时识别离散参数。该分析能力可以赋能设计团队,助其达成确凿的收敛和优化,利用硅预测预判延迟,并提高 PPA 和良率。

电压阈值偏斜稳健性

05

电压阈值(VT)偏斜稳健性是 Tempus DRA 套件的第五项分析能力,用于应对目前 STA 方法固有的时序悲观。Tempus DRA 套件帮助工程师更灵敏的分析 TT(温度和电压)corners,为每个 VT 类型执行快速降额以将延迟优化至慢 corners 和快 corners(SSG 和 FFG)。设计师可以将库与 VT 类型捆绑,为每个 VT 类型定义慢和快降额。Tempus DRA 套件可以执行优化排列,并根据 VT 类型的启动和捕捉路径找出最差的松弛变量。

Tempus DRA 套件是一套高级分析能力的完整合集,致力于增强设计层稳健性,对比传统方法实现更卓越的 PPA 提升。得益于其对老化稳健性、电压稳健性、时序稳健性、硅预测和 VT 偏斜稳健性的专注,该套件可以助力设计团队在快速迭代的技术环境下创建更高效、可靠、具有竞争力的半导体解决方案。这是实现新一代半导体设计的关键一步。

Tempus DRA 套件是广泛 Cadence 数字与签核工作流程的组成部分,支持 Cadence 智能系统设计战略,助理实现卓越的片上系统(SoC)设计。

点击文末“阅读原文”,了解更多 Tempus 时序解决方案的高级分析特性。

关于 Cadence

Cadence 是电子系统设计领域的关键领导者,拥有超过 30 年的计算软件专业积累。基于公司的智能系统设计战略,Cadence 致力于提供软件、硬件和 IP 产品,助力电子设计概念成为现实。Cadence 的客户遍布全球,皆为最具创新能力的企业,他们向超大规模计算、5G 通讯、汽车、移动设备、航空、消费电子、工业和医疗等最具活力的应用市场交付从芯片、电路板到完整系统的卓越电子产品。Cadence 已连续九年名列美国财富杂志评选的 100 家最适合工作的公司。如需了解更多信息,请访问公司网站 www.cadence.com。

2023 Cadence Design Systems, Inc. 版权所有。在全球范围保留所有权利。Cadence、Cadence 徽标和 www.cadence.com/go/trademarks 中列出的其他 Cadence 标志均为 Cadence Design Systems, Inc. 的商标或注册商标。所有其他标识均为其各自所有者的资产。

-

Cadence

+关注

关注

65文章

923浏览量

142222

原文标题:Tempus DRA 套件加速先进节点技术

文章出处:【微信号:gh_fca7f1c2678a,微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

为DRA71x、DRA79x和TDA2E-17供电的LP8733-Q1和LP8732-Q1用户指南

TPS659039-Q1为DRA74x、DRA75x、TDA2x和AM572x供电的用户指南

CoWoS先进封装技术介绍

DRA74x、DRA75x和DA2x系列设备的服务质量(QoS)旋钮

DRA75x、DRA74x信息娱乐应用处理器器件版本2.0数据表

DRA75xP、DRA74xP信息娱乐应用处理器芯片版本1.0数据表

DRA77xP、DRA76xP信息娱乐应用处理器芯片版本1.0数据表

CDN节点是什么

Tempus DRA 套件加速先进节点技术

Tempus DRA 套件加速先进节点技术

评论