引言

基于GaN的高电子迁移率,晶体管,凭借其高击穿电压、大带隙和高电子载流子速度,应用于高频放大器和高压功率开关中。就器件制造而言,GaN的相关材料,如AlGaN,凭借其物理和化学稳定性,为等离子体蚀刻技术提供了典型应用。蚀刻工艺对器件特性有着较大的影响,尤其是在精确控制蚀刻深度和较小化等离子体损伤的情况下影响较大。

场效应晶体管中凹陷栅极结构的电流水平和动态电流崩溃特性或二极管在很大程度上取决于蚀刻表面的凹陷深度和陷阱状态。尽管传统的等离子体蚀刻方法,例如反应离子蚀刻(RIE)和电感耦合等离子体(ICP)-RIE,但涉及(Al)GaN的O2等离子体氧化结合基于HCl:H2O溶液的氧化物去除的数字蚀刻工艺由于相关的低蚀刻损伤和容易控制凹陷深度而受到相当大的关注。

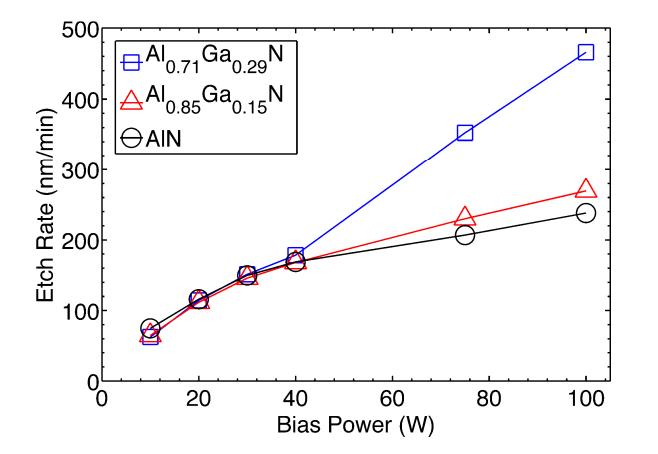

然而,由于等离子体氧化和湿法蚀刻工艺的结合,该工艺是劳动密集型的,并且涉及低蚀刻速率。在这种情况下,原子层蚀刻(ALE)工艺的实现是原位数字蚀刻工艺,并且具有相对高的蚀刻速率和低的蚀刻损伤,是可取的。为了利用ALE工艺的优点,必须优化工艺条件以较小化等离子体引起的蚀刻损伤,并获得自限制特性以精确控制蚀刻深度。

实验与讨论

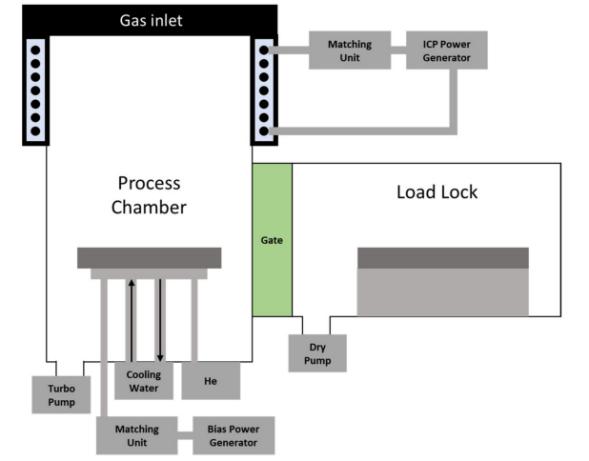

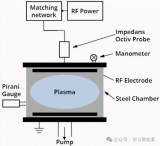

ALE工艺在ICP蚀刻系统中进行,其中使用氦背面冷却系统将卡盘温度设定为5℃,并且使用涡轮泵抽空腔室。详细的系统图如图所示1。

图1:电感耦合等离子体(ICP)蚀刻器示意图

图1:电感耦合等离子体(ICP)蚀刻器示意图使用O2等离子体氧化AlGaN层,并且使用BCl3等离子体去除氧化层。O2和BCl3的气体流速分别为50和10sccm。在O2和BCl3等离子体步骤之后,进行泵送步骤30秒,以避免任何残余O2或BCl3气体污染样品。

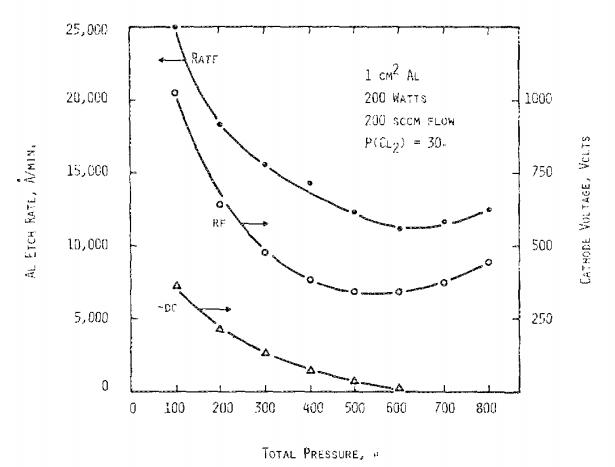

O2和BCl3等离子体处理过程中的压力分别为50毫托和10毫托,研究了ICP和偏置功率对DC自偏置的影响,如图所示2。观察到DC自偏压分别随着偏压功率和ICP功率的增加而增加和减少。尽管考虑到无法消除的浮动电势,在系统中测量的DC自偏置值似乎太低,但是很明显,用较低的偏置功率和较高的ICP功率可以实现较低的DC自偏置。在系统中无法测量浮动电位的准确评估。

使用在蚀刻的n-GaN表面上制造的肖特基二极管来评估蚀刻损伤。我们采用的n-GaN-on-Si晶圆由300 nm n-GaN漂移层(a-Si掺杂浓度为2.5 1017 cm)、700 nm高掺杂n-GaN接触层(a-Si掺杂浓度为(2–3)1018 cm3)、3900 nm GaN缓冲层和Si衬底组成。使用丙酮、甲醇和异丙醇进行溶剂清洗,开始制造装置。

随后,沉积200 nm的SiNx钝化层作为掩模层。随后通过Ti/Al金属化和在N2环境气氛中在550℃快速热退火1分钟形成欧姆接触。通过20 W的基于SF6的RIE打开SiNx层,并且通过使用两种不同的方法,即ALE和数字蚀刻,将暴露的GaN层蚀刻到5 nm的深度。在SiNx开口工艺之后,通过电子枪蒸发沉积Ni/Au (40/200 nm)金属电极。圆形电极的直径为50 m,并与同心触点隔开15 m的间隙。装置横截面如图所示7。

结论

在ICP-RIE系统中使用O2和BCl3等离子体的ALE被开发以实现具有低蚀刻损伤的自限制蚀刻工艺。O2等离子体步骤的ALE工艺条件如下:400 W的ICP功率、3W的偏压功率、50 mTorr的室压、4V的DC自偏压和60s的等离子体时间。BCl3等离子体步骤的ALE工艺条件包括400W的ICP功率、2W的偏压功率、10mTorr的室压、3.8V的DC自偏压和45s的等离子体时间,这导致0.7nm/周期的蚀刻速率。

使用包括AFM、PL和XPS在内的各种评估方法对蚀刻损伤进行了研究,并将嵌入式肖特基二极管的I-V特性与使用O2等离子体氧化和基于HCl溶液的氧化物去除的传统数字蚀刻工艺获得的I-V特性进行了比较。

与使用O2等离子体和HCl溶液的传统数字蚀刻工艺相比,使用O2和BCl3等离子体的ALE导致肖特基二极管的更好的电特性,以及更高的PL强度、增加的N/(Al + Ga)比和更平滑的蚀刻表面。此外,ALE技术表现出优异的自限制特性,并确保蚀刻深度和循环次数之间的高线性。提出的ALE工艺被认为有希望应用于(Al)GaN腐蚀,其中腐蚀深度的精确控制和低腐蚀损伤是必要的。

审核编辑 黄宇

-

蚀刻

+关注

关注

10文章

431浏览量

16700 -

GaN

+关注

关注

21文章

2391浏览量

84876 -

离子

+关注

关注

0文章

110浏览量

17549

发布评论请先 登录

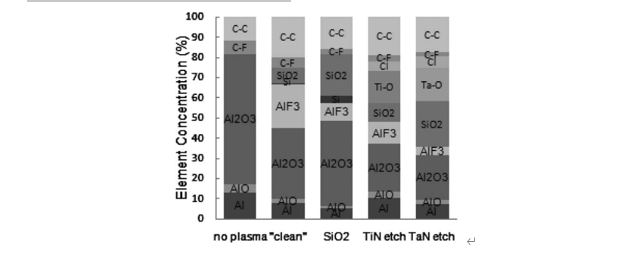

金属蚀刻残留物对对等离子体成分和均匀性的影响

等离子体蚀刻和沉积问题的解决方案

PCB多层板等离子体处理技术

PCB电路板等离子体切割机蚀孔工艺技术

PCB板制作工艺中的等离子体加工技术

PCB多层板等离子体处理技术

低温等离子体废气处理系统

TDK|低温等离子体技术的应用

等离子体应用

电磁波在等离子体层中衰减的数值分析

空间等离子体鞘层的时域特性研究

针对氧气(O2)和三氯化硼(BCl3)等离子体进行原子层蚀刻的研究

针对氧气(O2)和三氯化硼(BCl3)等离子体进行原子层蚀刻的研究

评论