SiC MOSFET芯片的短路能力是非常差的,目前大部分都不承诺短路能力,有少数在数据手册上标明短路能力的几家,也通常把短路耐受时间(SCWT:short circuit withstand time)限制在3us内。

这个相比Si基IGBT动辄6us甚至10us的时间,降低了很多,最近看了一些资料,尝试着理解一下。

从最基本的逻辑出发,芯片发热是芯片内部的电流做功引起的,因此主要考虑电流和芯片内部的结构。

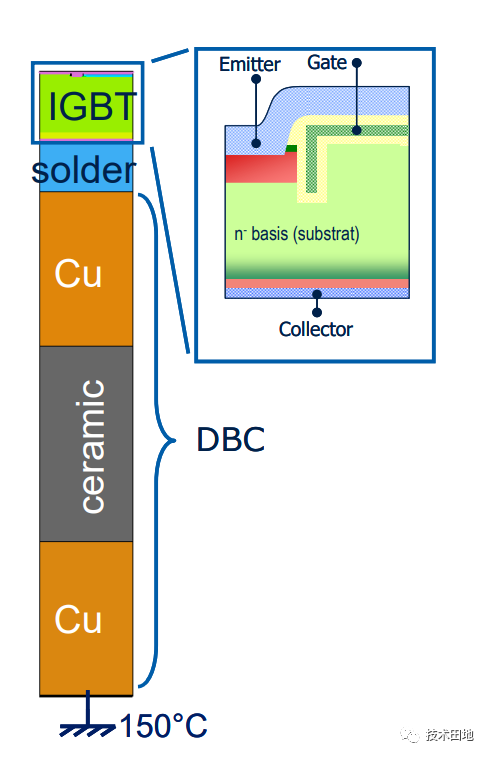

先看Si IGBT模块的结构:

我们可以看到,一颗IGBT芯片焊接在DBC衬板上,芯片底部是集电极(Collector),和散热的铜连接,顶部是发射极(Emitter),和键合线相连(图中未画出),电流方向从C到E。

我们都知道,IGBT工作的时候,本来电阻较高的N-漂移层,由于电导调制效应,载流子被注入,这就导致N-漂移层的电导率很高,因此大电流流过这个区域的时候,压降ΔV drift很小,此区域的发热功耗P=ΔV×I就很小,因此在N-区不会产生大量的热量。

IGBT的压降主要是来自哪里?其实主要是衬底的P到N这个场截止层,从下图的红色电场分布看得出来,电场主要是由靠近集电极的PN结来承受。

根据发热功率P=ΔV×I,这个ΔV很大,因此这个P很大,发热主要是靠近IGBT芯片底部的集电极。

再看第一张图,IGBT芯片底部,那不正好是散热的覆铜板吗?所以这个热可以很快扩散,相对来说容易散出去。

再看SiC MOSFET的结构:

大家不要被这张图骗了,图是对的,但是下面那个N+SUBSTRATE厚度比例不对,图中N-DRIFT层的厚度是10um,而N+SUBSTRATE的厚度,是200um左右!

MOS结构就很简单了,导通的时候没有PN结,是通过MOS沟道导电的,因此,哪个地方发热严重完全取决于哪个地方的电阻大!

直接上图(感谢Anant Agarwal教授的资料)

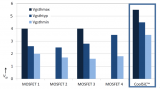

可以看到,沟道电阻和外延层占比遥遥领先!根据最简单的安培定理

可以得出,SiC MOSFET芯片发热最严重的区域是MOS沟道和外延层,也就是芯片的顶部区域!

对于沟槽SiC来说也差不多,因为沟槽SiC电阻最大的区域是外延层,也靠近芯片的顶部。

这下就不太好搞了,因为散热板在芯片底部,但是发热集中在芯片顶部,因此SiC MOSFET芯片短路时的散热天然要差一些,毕竟导热铜衬板离热源还有点远。

当然,不能完全只看压降和电阻,Si IGBT和SiC MOSFET芯片本身的尺寸以及电流大小也要看的。

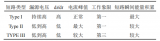

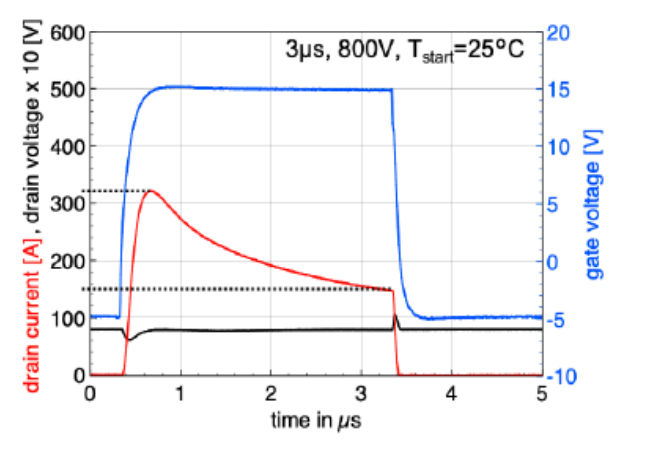

上图是英飞凌做的一个对比,我们简单算一下,一个标称300A的IGBT芯片,尺寸10mm×10mm,短路电流差不多2000A。

一个标称120A的SiC MOSFET芯片,尺寸5×5mm,短路电流差不多1200A来算。

IGBT短路电流密度:2000/100=20A/mm2

SiC MOSFET短路电流密度:1200/25=48A/mm2

仅仅是电流密度大了2.5倍,再加上发热位置是芯片散热较差的顶部,SiC 芯片短路能力比IGBT差也是情理之中。

如图,可以看到,大部分发热集中在SiC MOSFET芯片顶部。

图源:英飞凌

再看看IGBT的温度分布,就要均匀很多。

-

芯片

+关注

关注

463文章

54463浏览量

469595 -

MOSFET

+关注

关注

151文章

10834浏览量

235040 -

IGBT

+关注

关注

1291文章

4453浏览量

264499 -

SiC

+关注

关注

32文章

3874浏览量

70193

发布评论请先 登录

如何实现SiC MOSFET的短路检测及保护?

为何使用 SiC MOSFET

SiC-MOSFET的应用实例

SiC-MOSFET与Si-MOSFET的区别

SiC-MOSFET的可靠性

SiC-MOSFET有什么优点

SiC功率器件SiC-MOSFET的特点

SiC MOSFET:经济高效且可靠的高功率解决方案

SiC MOSFET的器件演变与技术优势

为什么SiC MOSFET的短路耐受时间比较小

SiC MOSFET短路失效的两种典型现象

浅谈SiC MOSFET芯片的短路能力

浅谈SiC MOSFET芯片的短路能力

评论