1、RR轮询调度?

在设计中,我们经常会用到RR(Round-Robin,RR)轮询调度,用于保证在一个时间段内的多个请求信号都能得到公平响应。

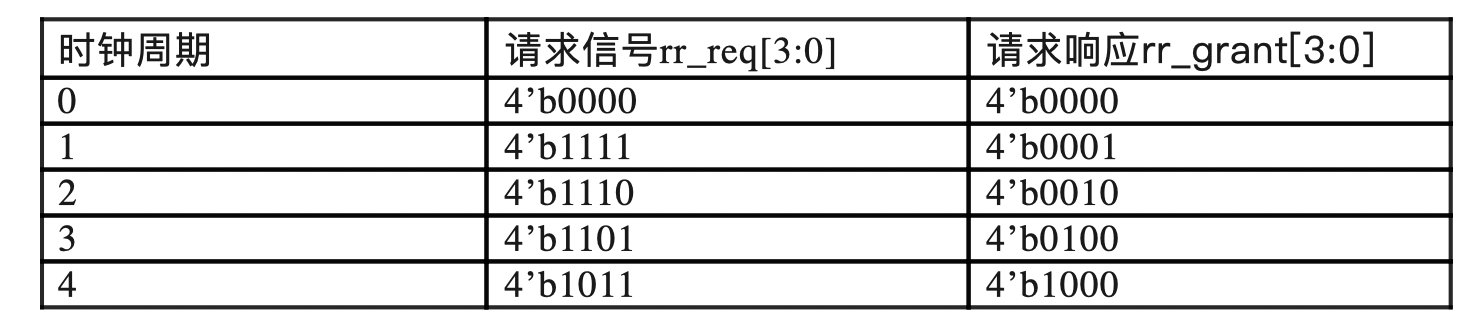

如下所示:输入rr_req[3:0]为4个请求信号,输出rr_grant[3:0]为4请求信号对应的4个响应信号:rr_req[n]表示第n请求申请响应,rr_grant[n]为1表示第n个请求被响应。如表所示,T1周期,所有请求均有效,首先响应低bit的请求,所以rr_grant[0]=1。T3周期,请求rr_req[0]有效,但是在T2时刻中被响应(rr_grant[1]=1),因此此次不再响应,而是响应rr_req[2],所以rr_grant[2]=1.

| 时钟周期 | 请求信号rr_req[3:0] | 请求响应rr_grant[3:0] |

| 0 | 4’b0000 | 4’b0000 |

| 1 | 4’b1111 | 4’b0001 |

| 2 | 4’b1110 | 4’b0010 |

| 3 | 4’b1101 | 4’b0100 |

| 4 | 4’b1011 | 4’b1000 |

2、Verilog是如何实现RR轮询调度的?

在verilog实现中,仅仅采用简单的组合逻辑和寄存器就可以实现rr轮询调度,不需要状态机等设计。

基本原理是锁存上一次输出请求响应rr_grant[3:0],并且生成相应的有效位rr_mask[3:0],从(rr_valid[3:0]&rr_mask[3:0]) 和 rr_valid[3:0]&(~rr_mask[3:0]) 选取不为0的作为获得rr_grant_tmp,rr_grant_tmp再经过组合逻辑并且取最低有效位。此处mask中1表示请求有效。

| A | B | C | D | E | F | G |

| 时间顺序 | 请求信号rr_req[3:0] | pre_rr_result(rr_grant[3:0]的打拍锁存值) | rr_mask |

~rr_mask 生成有效位 |

rr_grant_tmp B&D or B&E,取其中不为0的 |

请求响应rr_grant[3:0] |

| 0 | 4’b0000 | 4’b0000 | 4’b1111 | 4’b0000 | 4’b0000 | 4’b0000 |

| 1 | 4’b1111 | 4’b0000 | 4’b1111 | 4’b0000 | 4’b1111 | 4’b0001 |

| 2 | 4’b1110 | 4’b0001 | 4’b0001 | 4’b1110 | 4’b1110 | 4’b0010 |

| 3 | 4’b1101 | 4’b0010 | 4’b0011 | 4’b1100 | 4’b1100 | 4’b0100 |

| 4 | 4’b1011 | 4’b0100 | 4’b0111 | 4’b1000 | 4’b1000 | 4’b1000 |

B列:为请求信号rr_req[3:0]

C列:pre_rr_result 为模块内部锁存的上一拍rr_grant[3:0],即寄存器锁存打拍

D列:rr_mask为pre_rr_result经过组合逻辑得到的掩码,rr_mask= {pre_rr_result[2:0],pre_rr_result[3]}-1’b1

E列:~rr_mask为pre_rr_result经过组合逻辑得到的掩码,rr_mask=~( {pre_rr_result[2:0],pre_rr_result[3]}-1’b1)

F列:rr_grant_tmp为B&D or B&E,取其中不为0的

G列:rr_grant_tmp经过组合逻辑输出最低有效位:(~rr_grant_tmp+1’b1)&rr_grant_tmp

审核编辑:刘清

-

寄存器

+关注

关注

31文章

5394浏览量

122198 -

IC设计

+关注

关注

38文章

1326浏览量

104729 -

Verilog

+关注

关注

28文章

1360浏览量

111094

原文标题:IC设计:RR调度原理

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Linux系统调度是实现特性的关键部分

干货分享:基于嵌入式Linux中进程调度实现方法

请问FreeRTOS是如何实现调度的?

Microchip单片机固定时间片轮询调度汇编代码 精选资料分享

Microchip单片机固定时间片轮询调度汇编代码 精选资料推荐

STM32是怎样去实现软件时间片调度的

基于FPGA的轮询合路的设计和实现

基于SDH芯片的S19202的轮询合路的设计

Microchip单片机固定时间片轮询调度汇编代码

STM32 操作系统内核调度原理与实现(1):轮询系统,前后台系统与多线程系统

IC设计:Verilog是如何实现RR轮询调度的?

IC设计:Verilog是如何实现RR轮询调度的?

评论