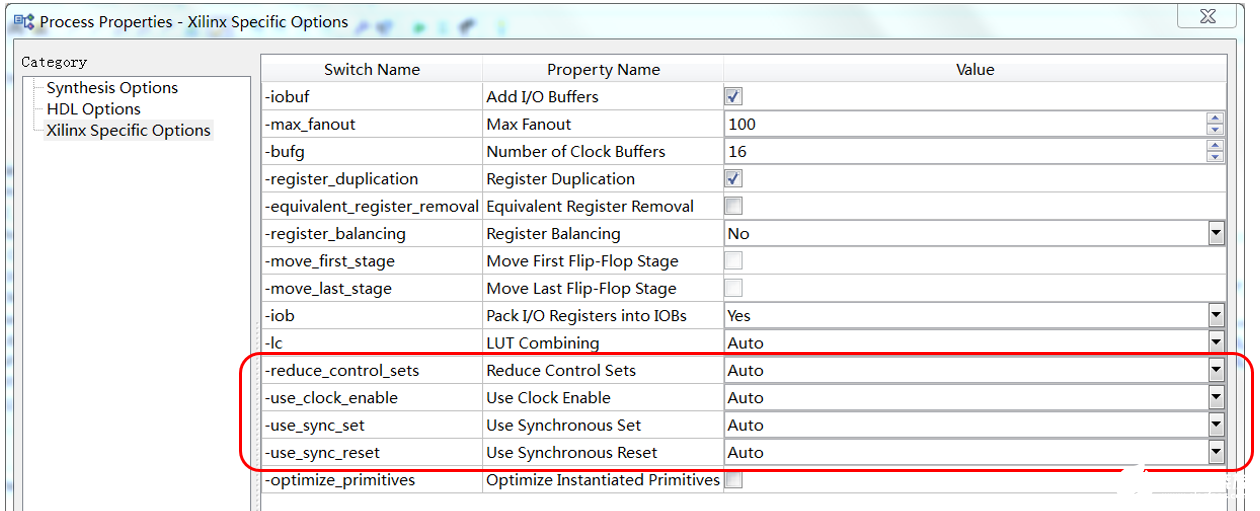

Spartan-6的一个Slice中包含8个触发器(FFs),每个触发器包括两个控制信号:CE、SR(只能用作Reset或Set之一),但这8个触发器共用控制信号输入端口,这一特性限制控制信号不同的触发器在布局(Map)时,不能优化入同一Slice,正是基于此,Xilinx推荐对于低扇出的触发器控制信号在代码编写时尽量吸收进触发器D输入端之前的LUT中,并在XST的综合属性选项中提供配置项,让XST综合时自动将低扇出的控制信号吸收进触发器D输入端之前的LUT中,如下图:

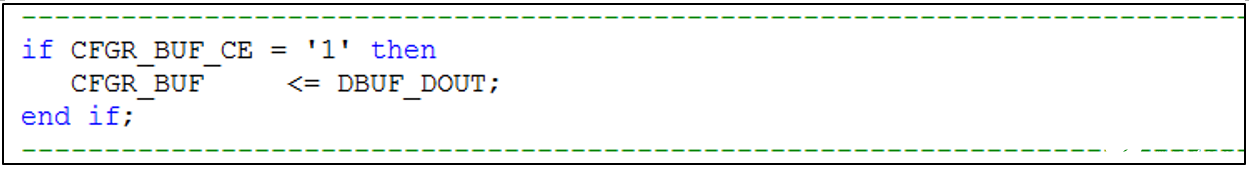

但是,对于设计中大量使用的门控型总线数据,即满足某种条件时寄存一组总线数据,采用FDE的设计方式更有利于控制CE信号的扇出数量,基于此思路,特别试验,代码如下,其中DBUF_DOUT、CFGR_BUF即为32-bits的总线型数据:

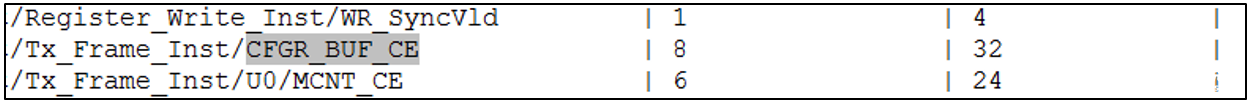

布局后,查看XST的Map Report中的Control Sets章节,如下图:

可以看到,CFGR_BUF[31:0]这组总线数据采用8个Slices实现,每个Slice使用4个FFs,符合设计预期。

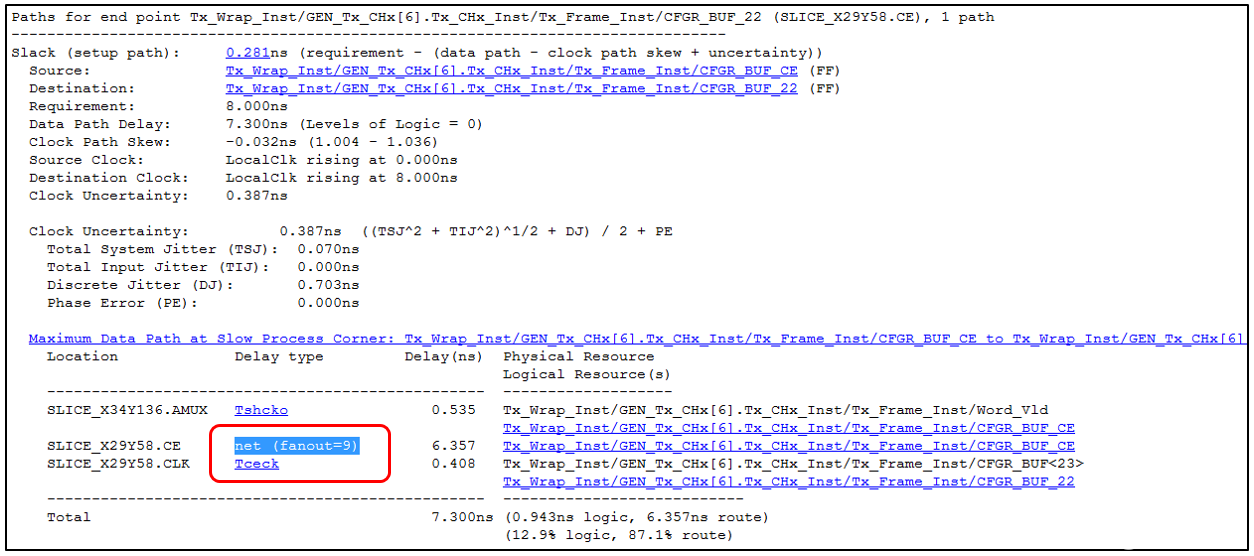

查看PAR后的Static Timing报告,可以看到,Static Timing报告中对CFGR_BUF_CE信号的扇出数量统计为9,即每个Slice的CE输入端口统计为一个信号扇出,符合设计预期,如下图:

综合Xilinx用户手册介绍的原理和实际试验结果,可以得出如下结论:XST在对Spartan-6布局布线时一个Slice的SR、CE输入端口统计为一个信号扇出负载。

审核编辑:黄飞

-

Xilinx

+关注

关注

71文章

2163浏览量

120975 -

触发器

+关注

关注

14文章

1995浏览量

61043 -

控制信号

+关注

关注

0文章

162浏览量

11948

发布评论请先 登录

相关推荐

XMC4300从控制器与Spartan-6 FPGA兼容吗?

Spartan-6 IO是否具有内置的施密特触发器?

Spartan-6 FPGA工业影像目标设计平台(Xilin

基于Spartan-6的FPGA SP601开发设计方案

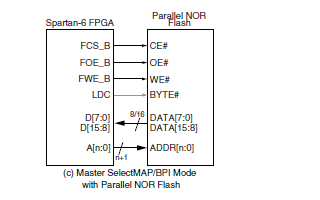

Spartan-6 FPGA Configuration User Guide

Xilinx Spartan-6系列封装概述和管脚分配

如何使用Xilinx Spartan-6的物流解决方案

Spartan-6 FPGA中的DCM功能介绍

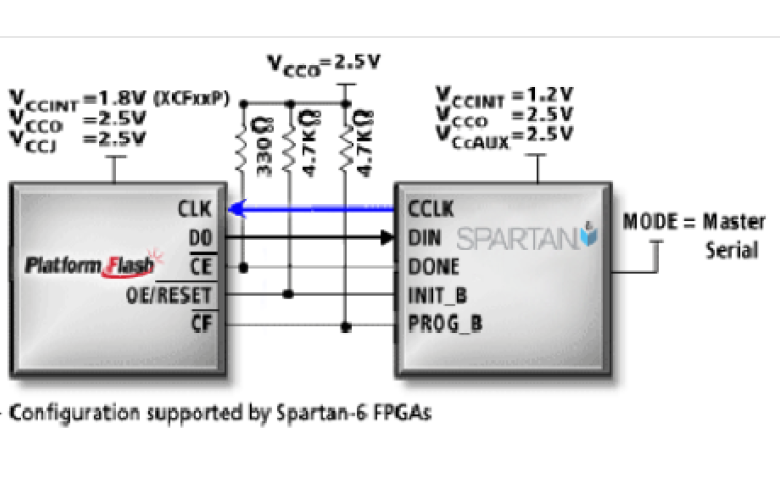

Spartan-6 FPGA的配置教程说明

Spartan-6触发器控制信号的扇出数量统计方式

Spartan-6触发器控制信号的扇出数量统计方式

评论